CDCM7005-SP:高性能时钟同步器的深度解析

在电子设计领域,时钟同步器对于确保系统的稳定运行至关重要。今天我们要探讨的CDCM7005-SP,就是一款高性能、低相噪和低偏斜的时钟同步器,它在诸多方面展现出了卓越的性能。

文件下载:cdcm7005-sp.pdf

一、产品概述

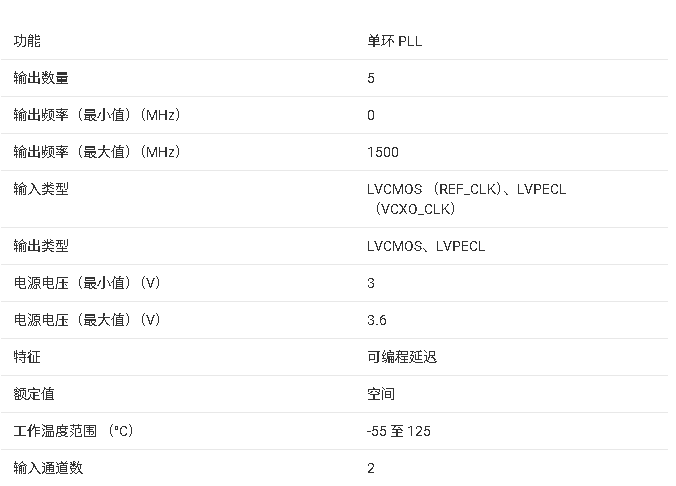

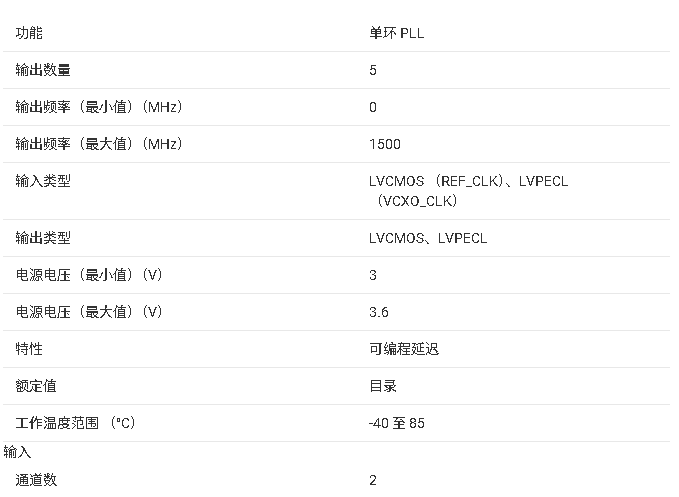

CDCM7005-SP能够将VCXO(压控晶体振荡器)或VCO(压控振荡器)的频率同步到两个参考时钟之一,VC(X)O_IN时钟最高可运行至2.0 GHz。通过选择外部VC(X)O和环路滤波器组件,可以调整PLL环路带宽和阻尼系数,以满足不同的系统需求。该器件支持两个参考时钟输入(PRI_REF和SEC_REF),具备频率保持模式和快速频率锁定功能,可提高系统的故障安全性能和冗余性。其输出可由用户定义,最多可组合成五个LVPECL输出或十个LVCMOS输出,LVCMOS输出成对排列,每个输出可单独反转和禁用,内置的同步锁存器确保所有输出同步,实现低输出偏斜。此外,它通过SPI(3线串行外设接口)可编程,可单独控制设备设置,工作在3.3 - V环境中,工作温度范围为 - 55°C至125°C(Tcase)。

二、产品特性亮点

2.1 参考时钟切换

支持手动和自动两种参考时钟切换模式。手动模式下,通过REF_SEL信号选择;自动模式下,默认选择主时钟,主时钟不可用时切换至从时钟。在自动模式下,两个时钟信号的频率需相似,相差不超过20%,且时钟输入电路可抑制切换时的毛刺,避免后续电路出现未定义的切换情况,输出时钟相位会缓慢跟随新的输入相位,无相位跳变。这为系统在不同时钟源之间的切换提供了稳定可靠的保障,大家在实际设计中可以根据系统的具体需求灵活选择切换模式。

2.2 PLL锁相检测

提供数字和模拟两种PLL锁相指示信号。当PLL根据所选锁相条件锁定时,PLL_LOCK输出逻辑高电平。数字锁相选项可能会在锁定和失锁之间抖动,直到检测到稳定锁定;模拟锁相选项则通过内部电流源对外部电容充电,抑制抖动,但检测逻辑高电平所需时间更长。在实际应用中,需要根据系统对锁相稳定性和响应速度的要求来选择合适的锁相检测方式。

2.3 输出类型与相位调整

支持最多5个LVPECL输出或10个LVCMOS/LVTTL输出,或它们的任意组合。LVPECL输出设计用于端接到50 - Ω负载至VCC - 2V,LVCMOS输出支持标准LVCMOS负载。输出可单独启用或禁用,还可通过P16 - Div的div - by - 4或div - by - 8模式将输出相位偏移90度,LVCMOS还支持每个输出单独的禁用至低电平和180°输出相位偏移。这种丰富的输出配置和相位调整功能,使得CDCM7005-SP能够适应各种不同的系统设计需求。

2.4 频率保持模式

HOLD功能可在输入参考时钟故障或中断时保持输出频率。在此期间,电荷泵关闭(3态),保持最后一个有效输出频率,直到有效参考时钟恢复。该功能需要模拟PLL锁相检测模式处于激活状态,涉及多个寄存器设置,如锁定检测窗口、锁定周期数、频率偏移检测等。这一功能大大提高了系统在时钟源异常情况下的稳定性,大家在设计对时钟稳定性要求较高的系统时一定要充分利用这个功能。

2.5 电荷泵预设与电流方向

电荷泵可预设为VCC_CP/2,有助于在电源启动或复位后快速设置VC(X)O的中心频率,该功能可通过SPI寄存器设置和复位,PLL锁定时必须禁用。电荷泵电流脉冲方向可通过SPI寄存器更改,正CP输出电流适用于无源环路滤波器,负CP电流适用于带有反相运算放大器的有源环路滤波器。这为不同的滤波器设计和系统需求提供了灵活的解决方案。

三、技术规格剖析

3.1 绝对最大额定值与ESD额定值

绝对最大额定值规定了器件在正常工作时所能承受的最大电压、电流和温度等参数,如VCC、AVCC、VCC_CP的电源电压范围为 - 0.5至4.6V,超出这些范围可能会对器件造成永久性损坏。ESD额定值方面,人体模型(HBM)为 + 2500V,带电设备模型(CDM)为 + 1500V,这表明器件在静电防护方面有一定的能力,但在实际使用中仍需注意静电防护措施,避免因静电放电对器件造成损害。

3.2 推荐工作条件

推荐工作条件为器件的正常运行提供了参考范围,如VCC和AVCC的电源电压推荐为3至3.6V,VCC_CP为2.3至VCC,输入电压范围、输出电流等都有相应的要求。在设计电路时,务必确保器件在这些推荐条件下工作,以保证其性能的稳定性和可靠性。

3.3 热信息

热信息对于评估器件在工作过程中的散热情况至关重要。CDCM7005-SP的结到自由空气热阻(RθJA)为21.813°C/W,结到外壳热阻(RθJC)为0.849°C/W。在设计散热方案时,需要根据这些热阻参数合理选择散热方式和散热器件,以确保器件在正常工作温度范围内运行。

3.4 电气特性

电气特性详细描述了器件的各项性能指标,包括电源电流、输出频率、相位偏移、脉冲偏斜等。例如,在不同输出配置和频率下,器件的电源电流会有所不同,这对于评估系统的功耗非常重要。输出频率方面,LVCMOS输出频率最高可达240MHz,LVPECL输出频率最高可达2000MHz,这些参数为我们在选择输出类型和设计系统时钟频率时提供了依据。

四、应用案例分享

4.1 插值DAC的时钟生成

在高速ADC和DAC的应用中,CDCM7005-SP凭借其出色的相噪性能,成为理想的采样时钟发生器。对于集成了插值滤波器的新型高速DAC,CDCM7005-SP能够满足其高采样率的需求。例如,在3G系统中,高速DAC的常见采样率为491.52 MSPS,通过四倍插值,数字输入所需的数据速率可降低至122.88 MSPS,这可以轻松由数字侧支持。CDCM7005-SP可以为DUC/DDC和ADC/DAC提供时钟信号,并且能够确保不同输出之间的最大偏斜不超过70 ps,保证了数据的准确传输。

4.2 相噪性能分析

在相噪性能方面,CDCM7005-SP表现优异。以特定测试条件为例,在不同频率点上,其LVCMOS和LVPECL输出的相噪都处于较低水平。例如,在10 Hz时,LVCMOS输出的相噪为 - 104 dBc/Hz,LVPECL输出的相噪为 - 100 dBc/Hz。此外,PLL稳定时间在特定条件下为400 ms,这对于系统的快速稳定运行非常关键。在实际应用中,我们可以根据这些相噪性能参数,合理选择参考时钟和VCXO,以优化系统的整体性能。

五、设计与布局建议

5.1 电源供应

CDCM7005-SP的电源方案相对简单,需要一般的VCC和模拟AVCC两个电源,两者电压应相同,并使用单独的磁珠进行隔离,无需特殊的电源排序。电荷泵使用单独的电源VCC_CP,该电源应与VCO/VCXO电源匹配,但不超过AVCC/VCC的最大推荐工作电压。同时,由于PD引脚为低电平有效,建议PD与VCC和AVCC同时或稍后升压,且升压速率不应快于VCC和AVCC。在实际设计中,我们要严格按照这些电源供应要求进行设计,以确保器件的正常工作。

5.2 布局准则

在布局方面,高频输入信号应尽可能通过最短路径布线,连续的接地平面应铺设在高信号路由下方,以最小化电流环路。电源旁路电容应尽可能靠近器件放置,避免在旁路电容和器件之间使用过孔。差分走线应保持在一起,以减少噪声注入,并且长度应精确匹配,以保证延迟相等。顶层时钟信号布线具有较小的传播延迟,通过在同一层设置接地平面可以增强抗噪能力。在实际的PCB设计中,我们要严格遵循这些布局准则,以提高系统的性能和稳定性。

六、总结与展望

CDCM7005-SP作为一款高性能的时钟同步器,在参考时钟切换、PLL锁相检测、输出配置、频率保持模式等方面都具有出色的性能。其丰富的功能和灵活的配置选项,使得它能够适应各种不同的系统设计需求。在实际应用中,我们需要根据具体的设计要求,合理选择器件的工作模式和参数,同时注意电源供应和布局设计,以充分发挥CDCM7005-SP的优势。随着电子技术的不断发展,相信CDCM7005-SP在未来的电子设计中将会发挥更加重要的作用。大家在使用过程中如果遇到任何问题或者有新的发现,欢迎在评论区留言分享。

-

电子设计

+关注

关注

42文章

2907浏览量

49916

发布评论请先 登录

CDCM7005QFN-EVM连接开发板时报错,如何解决?

CDCM7005 pdf datasheet (时钟同步器)

CDCM7005-SP 3.3V 高性能抗辐射 V 类时钟同步器和抖动消除器

CDCM7005-SP高性能、低相位噪声和低偏斜时钟同步器数据表

CDCM7005-SP:高性能时钟同步器的深度解析

CDCM7005-SP:高性能时钟同步器的深度解析

评论