CDCE937-Q1 和 CDCEL937-Q1:可编程 3-PLL VCXO 时钟合成器的技术解析

在电子设计领域,时钟合成器的性能对整个系统的稳定性和功能实现起着至关重要的作用。今天,我们将深入探讨 Texas Instruments 推出的 CDCE937-Q1 和 CDCEL937-Q1 可编程 3-PLL VCXO 时钟合成器,了解它们的特性、应用及设计要点。

文件下载:cdcel937-q1.pdf

1. 器件特性亮点

1.1 汽车应用资质

这两款器件均通过了 AEC-Q100 认证,具有出色的温度适应性和 ESD 防护能力。其器件温度等级 1 为 -40°C 至 125°C 的环境工作温度范围,HBM ESD 分类等级为 2,CDM ESD 分类等级为 C4B,能够满足汽车应用的严苛要求。

1.2 灵活的可编程性

- 寄存器与 EEPROM:具备系统内可编程性,拥有串行可编程的易失性寄存器和非易失性 EEPROM,可存储用户设置,方便进行定制化应用。

- 输入时钟概念:支持灵活的输入时钟,外部晶体频率范围为 8MHz 至 32MHz,片上 VCXO 的牵引范围为 ±150ppm,还支持单端 LVCMOS 高达 160MHz 的输入。

- 输出频率选择:输出频率可自由选择,最高可达 230MHz,能满足多种不同应用场景的需求。

1.3 低噪声与高性能

- 低噪声 PLL 核心:集成了 PLL 环路滤波器组件,具有低周期抖动(典型值为 60ps),能提供稳定、低噪声的时钟信号。

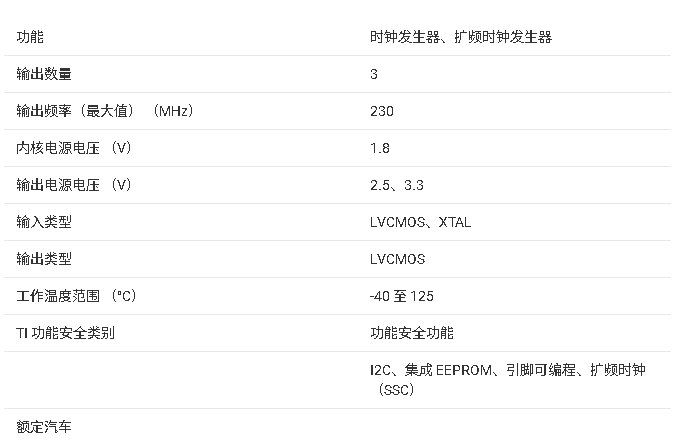

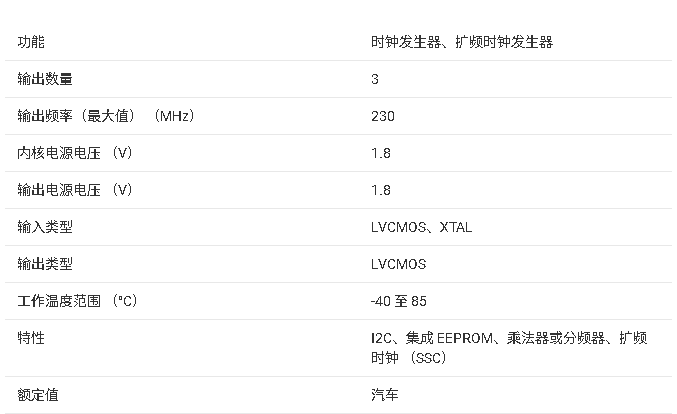

- 独立输出电源引脚:CDCE937-Q1 支持 3.3V 和 2.5V 输出电源,CDCEL937-Q1 支持 1.8V 输出电源,可根据具体应用进行灵活配置。

- 灵活的时钟驱动器:拥有三个用户可定义的控制输入 [S0/S1/ S2],可用于选择扩频时钟(SSC)、频率切换、输出使能或电源关断等功能。

1.4 其他特性

- 可编程 SSC 调制:支持可编程的 SSC 调制,可实现 0PPM 时钟生成,有效降低电磁干扰(EMI)。

- 宽温度范围:工作温度范围为 -40°C 至 125°C,适用于各种恶劣环境。

- 开发与编程套件:提供 TI Pro-Clock™ 开发和编程套件,方便进行 PLL 设计和编程。

2. 应用场景广泛

CDCE937-Q1 和 CDCEL937-Q1 可应用于多个汽车电子领域,如仪表盘、主机、导航系统和高级驾驶辅助系统(ADAS)等。在这些应用中,它们能够提供高精度的时钟信号,确保系统的稳定运行。

3. 详细功能解析

3.1 功能概述

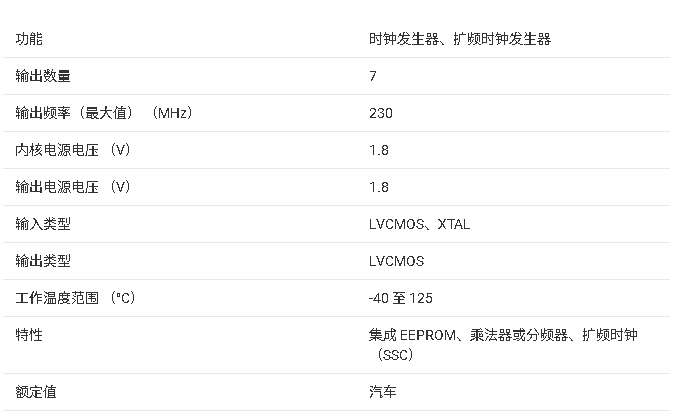

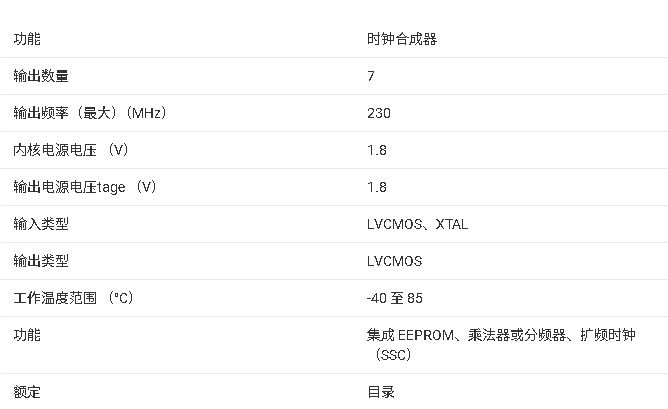

这两款器件是基于模块化锁相环(PLL)的可编程时钟合成器,可从单个输入频率生成多达七个输出时钟,节省了电路板空间和成本。同时,通过集成的可配置 PLL,每个输出都可在系统内编程为高达 230MHz 的任意时钟频率。

3.2 输入与输出

- 输入:可接受外部晶体或 LVCMOS 时钟信号。若使用外部晶体,片上负载电容通常能满足大多数应用需求,其值可在 0pF 至 20pF 之间编程。此外,还可选择片上 VCXO,实现输出频率与外部控制信号的同步。

- 输出:输出频率范围广,支持多种不同的输出电源电压,可根据具体应用进行选择。

3.3 控制与编程

- 控制输入:三个可编程控制输入 S0、S1 和 S2 可用于控制设备的各种操作,如频率选择、SSC 参数调整、PLL 旁路、电源关断等。

- 编程接口:支持通过 SDA 和 SCL 总线进行编程,可实现字节写入、字节读取、块写入和块读取操作。同时,还支持非易失性 EEPROM 编程,方便进行定制化应用。

3.4 SSC 功能

所有 PLL 均支持 SSC(扩频时钟),可采用中心扩展或向下扩展时钟,有效降低电磁干扰(EMI)。通过调整 PLL 频率和分频器设置,内部环路滤波器组件会自动调整,以实现每个 PLL 的高稳定性和优化的抖动传输特性。

4. 设计要点与注意事项

4.1 绝对最大额定值与推荐工作条件

在设计过程中,需严格遵守器件的绝对最大额定值,避免超出范围导致器件损坏。同时,应根据推荐工作条件进行设计,以确保器件的正常运行和性能稳定。

4.2 电源供应

- 电源顺序:使用外部参考时钟时,应先驱动 XIN/CLK 再使 (V{DD}) 上升,避免输出不稳定。若 (V{DDOUT}) 先于 (V{DD}) 施加,建议将 (V{DD}) 拉至 GND 直至 (V_{DDOUT}) 上升。

- 电源控制:器件的 1.8V 电源连接有上电控制电路,在 1.8V 电源达到足够电压之前,整个器件将保持禁用状态。

4.3 布局设计

- 晶体布局:当器件用作晶体缓冲器时,晶体的寄生参数会影响 VCXO 的牵引范围。因此,应将晶体单元尽可能靠近器件放置,并确保晶体端子到 Xin 和 Xout 的布线长度相同。

- 电源旁路电容:应将电源旁路电容尽可能靠近器件引脚放置,并使用低阻抗连接将电容的另一侧接地。

- 信号布线:在晶体及其布线区域,应避免布线其他信号线,以防止噪声耦合。

4.4 编程与配置

- EEPROM 编程:在进行 EEPROM 编程时,需注意编程顺序和状态监测。在编程过程中,SDA 和 SCL 总线不能发送数据,但可进行读取操作。

- 控制引脚设置:S1/SDA 和 S2/SCL 引脚为双功能引脚,可通过设置 EEPROM 中的相关位将其编程为控制引脚。但设置为控制引脚后,串行编程接口将不再可用。

5. 总结

CDCE937-Q1 和 CDCEL937-Q1 可编程 3-PLL VCXO 时钟合成器具有丰富的特性和广泛的应用场景,为电子工程师提供了灵活、高性能的时钟解决方案。在设计过程中,需充分考虑器件的特性和设计要点,以确保系统的稳定性和可靠性。大家在实际应用中遇到过哪些问题呢?欢迎在评论区分享交流。

-

时钟合成器

+关注

关注

0文章

115浏览量

8911

发布评论请先 登录

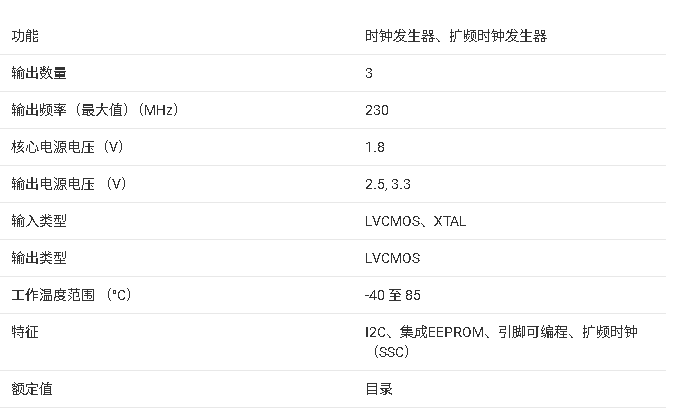

CDCE937和CDCEL937是基于模块化PLL的低成本高性能可编程时钟合成器、乘法器和分配器

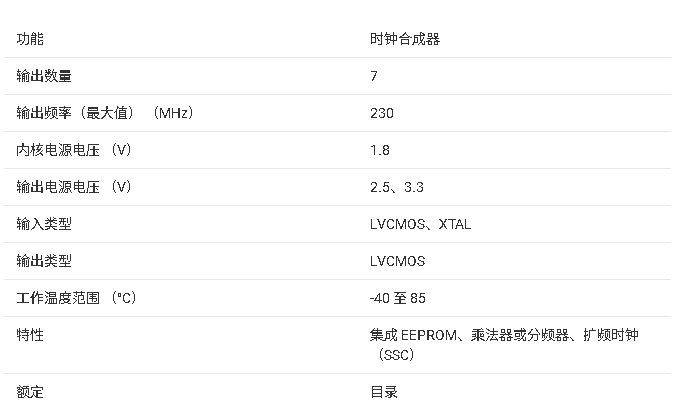

CDCE937-Q1 具有 2.5V 或 3.3V LVCMOS 输出的汽车类可编程 3-PLL VCXO 时钟合成器

CDCEx937-Q1可编程3-PLL VCXO时钟频率合成器数据表

CDCE949-Q1可编程4-PLL VCXO时钟合成器数据表

CDCE913-Q1和CDCEL913-Q1可编程1-PLL VCXO时钟合成器数据表

CDCE937-Q1 和 CDCEL937-Q1:可编程 3-PLL VCXO 时钟合成器的技术解析

CDCE937-Q1 和 CDCEL937-Q1:可编程 3-PLL VCXO 时钟合成器的技术解析

评论