深度剖析 LMX2581E 宽带频率合成器:特性、应用与设计要点

在电子设计领域,频率合成器是构建精确时钟和信号源的核心组件。今天,我们将深入研究德州仪器(TI)的 LMX2581E 宽带频率合成器,探讨其特性、应用场景以及设计过程中的关键要点。

文件下载:lmx2581e.pdf

一、LMX2581E 概述

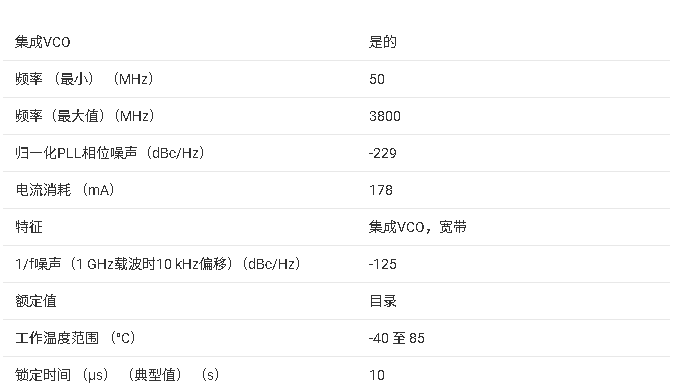

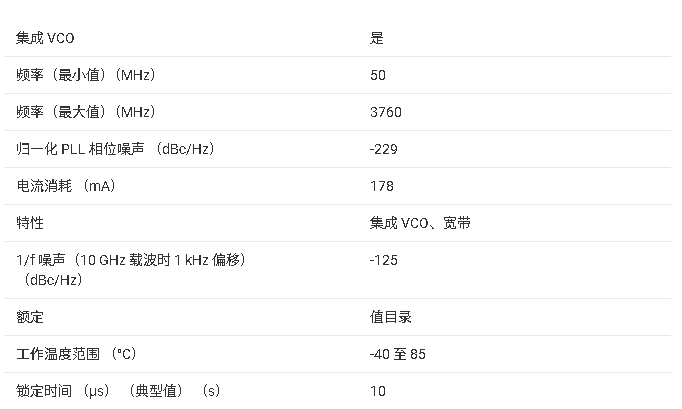

LMX2581E 是一款低噪声宽带频率合成器,它集成了 delta - sigma 分数 N 锁相环(PLL)、多个核心压控振荡器(VCO)、可编程输出分频器和两个差分输出缓冲器。该设备采用 32 引脚 5.0 mm × 5.0 mm WQFN 封装,工作于单一 3.3 V 电源。

1.1 关键特性

- 频率范围广泛:输出频率范围为 50 至 3800 MHz,输入时钟频率最高可达 900 MHz,鉴相器频率最高可达 200 MHz。

- 模式灵活:支持分数和整数模式,满足不同应用需求。

- 低噪声性能:归一化 PLL 相位噪声低至 - 229 dBc/Hz,归一化 PLL 1/f 噪声为 - 120.8 dBc/Hz,2.5 GHz 载波在 1 MHz 偏移时 VCO 相位噪声为 - 137 dBc/Hz。

- 可编程功能丰富:包括分数调制器阶数、分数分母、输出功率(最高可达 12 dBm)、32 级电荷泵电流等。

- 其他特性:具有数字锁定检测、三线串行接口和回读功能,支持低至 1.6 V 的逻辑电平。

1.2 应用领域

LMX2581E 适用于多种应用场景,包括无线基础设施(如 UMTS、LTE、WiMax、多标准基站)、宽带无线、测试与测量以及时钟生成等。

二、详细特性分析

2.1 输入与输出特性

- 输入时钟:OSCin 引脚接受单端信号作为频率参考,其频率可通过 OSCin 倍增器进行倍增,并通过 PLL R 分频器进行分频。为了获得最佳的分数杂散和相位噪声性能,建议使用方波信号,若使用正弦波,较高的频率通常能产生更好的性能。

- 输出缓冲器:RFoutA 和 RFoutB 引脚的输出状态由 BUFEN 引脚和 BUFEN_DIS 编程位控制。输出功率可通过 OUTx_PWR 字进行编程设置。在选择上拉组件时,电阻上拉可使输出阻抗易于匹配,但输出功率受限;电感上拉则能提供更高的输出功率,但需要注意输出阻抗匹配问题。

2.2 VCO 特性

- VCO 核心:内部 VCO 由多个核心(VCO 1 - 4)组成,每个核心具有 256 个不同的频段。通过频率校准例程,设备可以选择正确的 VCO 核心和频段。

- VCO 数字校准:当频率发生变化时,VCO 会进行数字校准,以确保选择合适的 VCO 核心和频段。通过合理设置 VCO_SEL 和 VCO_CAPCODE 等参数,可以显著缩短校准时间。

- VCO 相位噪声:VCO 相位噪声受温度影响,在不同温度下,相位噪声会有所变化。在设计时,需要根据实际应用场景考虑温度因素对 VCO 相位噪声的影响。

2.3 锁相环特性

- PLL N 分频器和分数电路:N 分频器包括分数补偿功能,可实现 1 至 4,194,303 的任意分数分母。整数部分 PLL_N 和分数部分 PLL_NUM / PLL_DEN 均为软件可编程。此外,Delta - Sigma 调制器的阶数也是可编程的,不同阶数的调制器在相位噪声和杂散性能上有所差异。

- 可编程抖动水平:抖动可以用于减少子分数杂散,但使用不当可能会产生杂散并增加相位噪声。因此,在使用抖动时,需要根据分数分母的情况进行合理设置。

- 电荷泵:电荷泵电流可通过软件编程设置为多个不同的级别。鉴相器频率 fPD 可根据公式 (f{PD}=f{OSC{in }} × OSC{2X/R}) 计算得出。

2.4 锁定检测

LMX2581E 提供两种锁定检测电路:Vtune 锁定检测和数字锁定检测。Vtune 锁定检测仅适用于内部 VCO,当调谐电压超出阈值时,会指示设备未锁定。数字锁定检测通过比较鉴相器的相位误差来判断是否锁定,但在某些情况下可能会出现误判。为了获得更可靠的锁定检测结果,建议同时使用这两种方法。

三、设计与编程要点

3.1 电源供应

建议使用低噪声稳压器为电源引脚供电,并为每个引脚进行单独的旁路电容配置,以获得最佳的杂散性能。不同模式下,各引脚的电流消耗有所不同,在设计电源电路时需要根据实际情况进行合理规划。

3.2 布局设计

- 输出缓冲器的上拉组件应尽可能靠近芯片,以提高输出功率。

- 确保 VbiasVCO 和 VbiasCOMP 引脚与地之间有稳固的连接,以降低 VCO 相位噪声。

- 环路滤波器的设计应考虑电容的位置和接地问题,避免将杂散能量耦合到 VCO 输入。

3.3 编程要点

- 串行数据输入时序:在编程时,需要注意 CLK、DATA 和 LE 信号的时序要求,建议 CLK、DATA 和 LE 信号的转换速率至少为 30 V/µs。

- 初始上电编程序列:设备首次上电时,需要按照特定的编程序列进行初始化,确保 Vcc 引脚电压正常,将有效参考信号施加到 OSCin 引脚,并按顺序编程各个寄存器。

- 频率更改序列:在更改频率时,需要根据具体情况编程相应的寄存器。例如,若 OUTx_MUX 状态、VCO_DIV 状态、分数分子的最高位或电荷泵增益发生变化,需要编程相应的寄存器,最后编程 R0 寄存器。

四、应用案例分析

4.1 时钟生成应用

在该应用中,目标是从 100 MHz 输入时钟生成 1500 MHz 输出时钟。为了实现最佳的相位噪声性能,选择较高的鉴相器频率(200 MHz)和较宽的环路带宽(256 kHz),并使用最大的电荷泵增益(31x)。通过合理选择输出功率设置(OUT_A_PWR = 45)和上拉组件(18 nH 电感),可以获得较高的输出功率和较低的抖动。

4.2 分数 PLL 应用

当输出频率与输入频率之间的关系不固定时,可以通过降低环路带宽和鉴相器频率来改善杂散性能,但会牺牲带内相位噪声。在设计过程中,需要根据具体的应用需求权衡这些因素。

五、总结

LMX2581E 宽带频率合成器以其丰富的特性、广泛的应用领域和灵活的编程功能,为电子工程师提供了强大的设计工具。在实际应用中,我们需要深入了解其各项特性和设计要点,根据具体的应用场景进行合理的配置和优化,以实现最佳的性能。你在使用类似频率合成器时遇到过哪些问题呢?欢迎在评论区分享你的经验和见解。

-

频率合成器

+关注

关注

5文章

365浏览量

33875

发布评论请先 登录

业界最低相位噪声频率合成器LMX2581的特性优势是什么

LMX2581E LMX2581E 具有集成 VCO 的宽带频率合成器

LMX2581E宽频带频率合成器技术文档总结

深度剖析 LMX2581E 宽带频率合成器:特性、应用与设计要点

深度剖析 LMX2581E 宽带频率合成器:特性、应用与设计要点

评论