使用目标阻抗去衡量仿真得到的PDN阻抗是否达标,并不是一个科学的做法。但很多时候选择的IC可能并没有提供各个频段所需的PDN阻抗值,甚至翻完整个Datasheet都没有提及PDN,这个时候就需要用到目标阻抗法来衡量仿真结果,毕竟有一个经验公式总比瞎搞好。

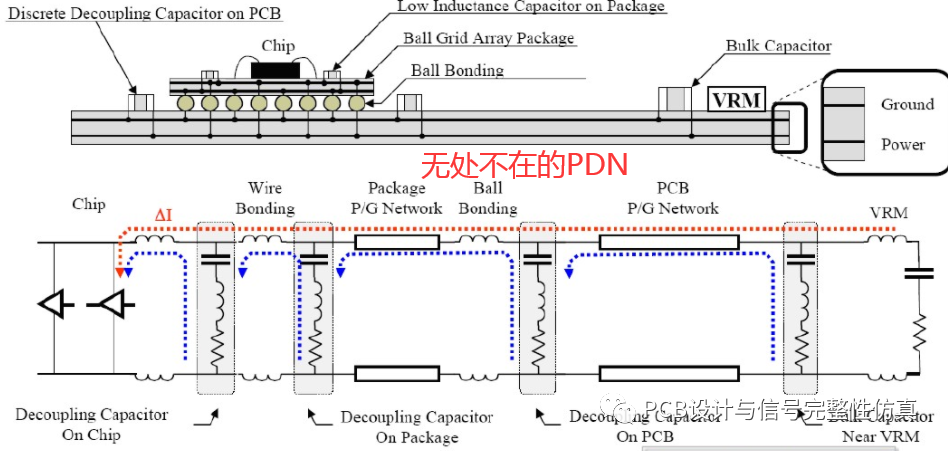

设计中,PDN也叫电源分配网络,全称是Power Distribution Network。为负载提供低噪声的电源,为信号提供低阻抗的返回路径等等都是它需要做的,它是衡量电源设计质量的重要指标。

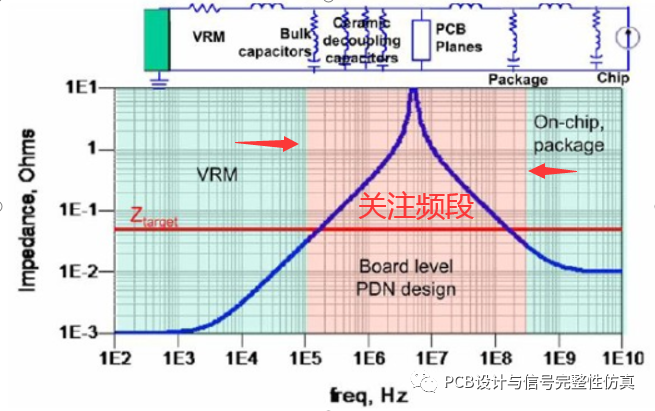

在一个系统中PDN的频率从HZ到GHZ都有。幸运的是对于PCB来说并不需要管这么宽的范围,低频段的交给VRM,高频段的交给IC的片上电容,实际上对于PCB来说需要关注的大概就在100K~100MHZ这样一个范围。

上面这张图中有一根横线(Z target),这跟横线就是目标值,判断电源设计是否合理,很重要的一个指标就是PDN阻抗不能超过目标值。

这个目标值在一些优秀的IC厂商提供的DATASHEET中明确给出,而且是各个频段对应不同的目标值,通常低频要求目标值较低,随着频率增高,这个值会逐渐增加(并不是说高频要求降低了,只是把这个任务的很大一部分交给了片上电容来完成)。

但对于没有给出这些信息的IC厂商,就可以考虑使用经验公式:目标阻抗法。

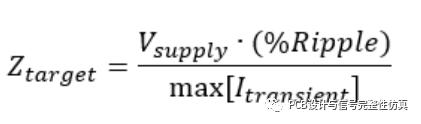

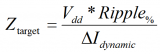

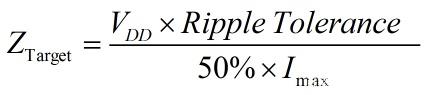

其公式为:

其中Ztarget是我们的目标值,Vsupply表示电压值,%ripple则是纹波的百分比,分母则是最大电流。

如果用最大电流来计算,会使得实际的目标阻抗值比较苛刻,正常情况下可以取0.5倍最大电流值计算即可,乐观点还可以0.3倍最大电流计算。

假设这个电源电压5V,纹波的峰峰值是3%,最大电流是2A,那么悲观的人得出的目标阻抗是:Ztarget=(5*0.03)/2=0.075;

心态正常的人得出的结果是:Ztarget=(5*0.03)/(2*0.5)=0.15;

乐观的小伙伴结果是:Ztarget=(5*0.03)/(2*0.3)=0.25。

因此目标阻抗在一定程度上属于看心情。

不管心情如何,总归是算出了一个目标阻抗值,有这就可以用于判断PDN阻抗是否达标。

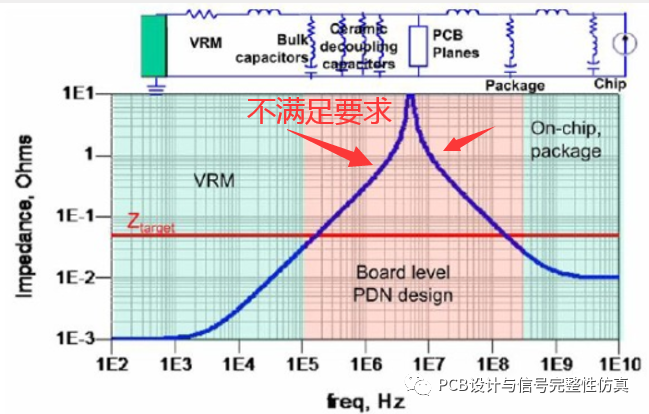

同样是这样图,我们假设Ztarget是我们计算出的目标阻抗,那么实际我们仿真出来的PDN阻抗在约200K~200MHZ这个范围内都是达不到要求的。

想要优化PDN阻抗值,使其在目标值以下的办法还是挺多的,比如改变层叠之类的。众多方法中,最有效的还是电容。

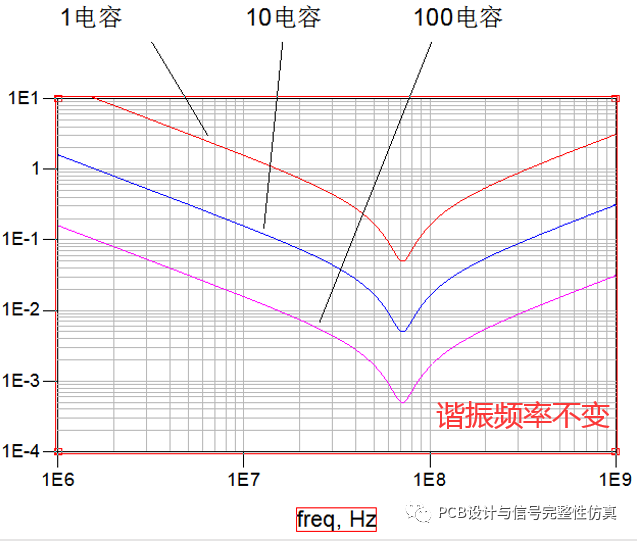

电容的应用从原理上来说分为两种,一种是并联大量的同类型电容,这个时候可以有效降低电源阻抗,且并不会改变谐振频率。

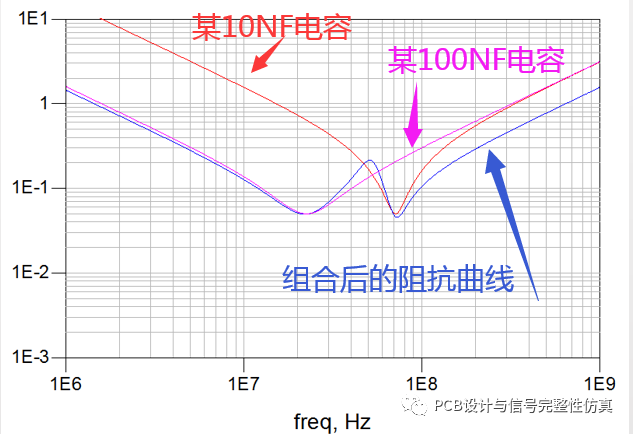

另外一种则是并联不同容值的电容,使用这种方式可以针对性的优化特定频段,但会引入新的反谐振点。

电容的调整是一个很复杂的事情,不光需要考虑各种类型电容的搭配,还需要考虑实际安装位置带来的影响。这种情况下使用前仿真来评估就显得有些力不从心,复杂的计算还是要交给后仿真。

在后仿真中,可以导入实际的PCB板和我们用到的电容库,让软件自动优化,给出限定条件下的最优解。

来源: 本文转载自PCB设计与信号完整性仿真公众号

审核编辑:汤梓红

-

阻抗

+关注

关注

17文章

993浏览量

49511 -

仿真

+关注

关注

55文章

4537浏览量

138672 -

PDN

+关注

关注

0文章

86浏览量

23505 -

电源分配网络

+关注

关注

0文章

14浏览量

8684 -

目标阻抗

+关注

关注

0文章

2浏览量

2339

原文标题:电源分配网络(PDN)与目标阻抗计算方法

文章出处:【微信号:电子设计联盟,微信公众号:电子设计联盟】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

电源分配网络(PDN)与目标阻抗的计算方法

电源分配网络(PDN)与目标阻抗的计算方法

评论