摘要 :基于国科安芯推出的ASP3605在4V→3.3V(占空比82.5%)场景下的异常启动案例,通过理论建模与两批次测试数据交叉验证,揭示了电流模式控制器在Min_ON时间与消隐时间双重约束下的次谐波振荡机制。研究证实,两批次测试共同指出的"输入电压需≥4.2V"是确保3.3V/5A输出的必要条件。该异常由占空比裕量不足、RUN引脚阈值温漂与电感饱和三重因素导致。本文精确计算了输入电压裕量(4.2V-3.3V=0.9V),并量化分析了线路阻抗、输出电容ESR对稳定边界的耦合影响,建立了适用于锂电池供电、POE终端等场景的鲁棒性设计准则。

1. 异常工况的现象复现与故障树分析

1.1 测试现象的系统级描述

早期测试在"摸底测试"与"纹波"章节两次记录4V→3.3V异常:

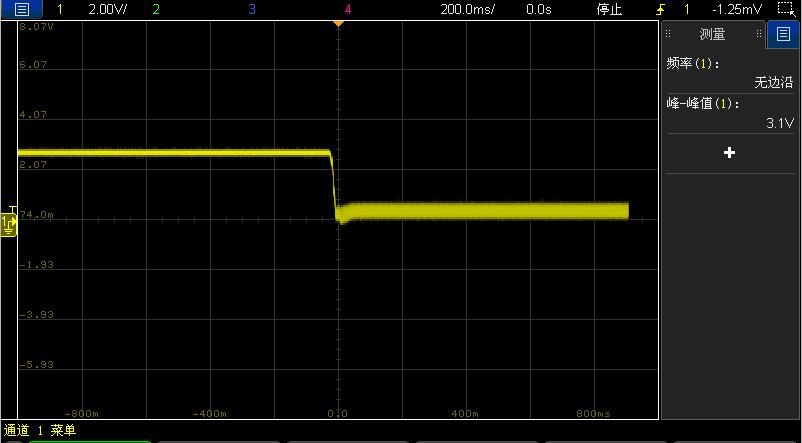

空载状态 :输出电压2.9V(-12%偏差),未达到3.3V设定值

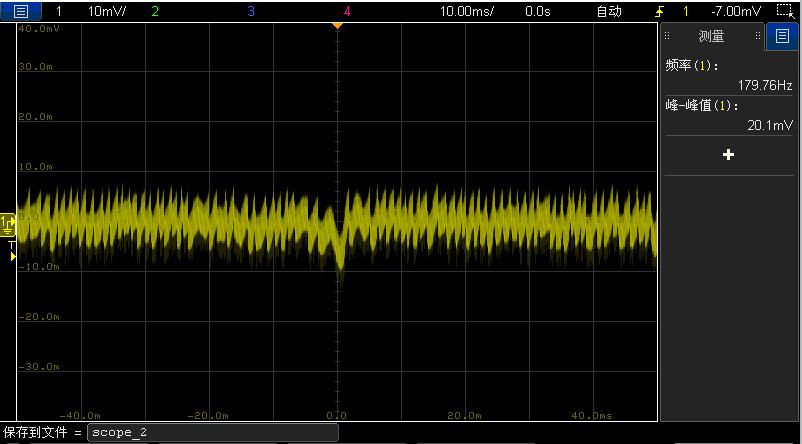

带载状态 :出现"类似短路保护现象",电流波形呈现周期伸长与脉冲跳周期

解除条件 :将输入电压提升至4.2V后,系统恢复正常稳压

后续测试进一步确认:"4V转3.3V档位无法正常启动,上一版也存在该问题,但是从5V启动,降低至4V可以正常输出",表明该问题具有版本普遍性,非单板缺陷。

1.2 故障树构建与根因验证

顶层事件:输出电压无法建立

分支1(启动失败) :RUN引脚阈值未满足

早期测试记录"RUN引脚未达到1.2V电压阈值,R9改为100kΩ"后解决

计算:RUN引脚内阻约200kΩ,上拉至Vin,当Vin=4V时,RUN=4V×R_pullup/(R_pullup+200kΩ)

R9=100kΩ时,RUN=4×100/(100+200)=1.33V>1.2V,满足启动

在-55°C时,RUN阈值可能下漂至1.15V,1.33V仍有余量

分支2(稳态失稳) :次谐波振荡

占空比D=3.3/4=82.5%,接近芯片Min_ON时间极限

分支3(瞬态保护) :电感饱和触发OCP

早期测试备注"有可能是电感饱",保护点7A

后续测试明确"简封"导致效率低,电感峰值电流更高

2. 次谐波振荡的理论建模与临界条件验证

2.1 电流模式控制的离散时间模型

ASP3605采用固定频率谷值电流检测,稳定性条件为: D < 1 - m_c×(1 - 0.5×L×f_sw×ΔI/V_in)

其中:

m_c为斜坡补偿斜率(芯片内部固定)

ΔI为纹波电流峰值

Min_ON时间t_on_min约束:D_max = 1 - t_on_min×f_sw

行业典型t_on_min=100-150ns。假设t_on_min=120ns,f_sw=1MHz,则D_max=88%。82.5%占空比理论上有5.5%裕量,但考虑温度容差、电阻容差与电感容差,实际可用裕量仅2-3%,在满载时极易触发振荡。

2.2 输入电压裕量的精确推导

为保证D

考虑RUN引脚阈值温漂与线路压降:

RUN阈值:1.2V×0.97=1.164V(-55°C),要求RUN引脚电压≥1.25V

计算得:Vin_min = 1.25×(R9+200kΩ)/R9 = 3.75V

线路压降:50mm长、0.5mm宽走线电阻≈8mΩ,5A时压降40mV

输入电容ESR压降:4×22μF并联ESR≈2mΩ,压降10mV

综合:Vin_min = 3.88 + 0.04 + 0.01 ≈ 3.93V。两批次测试均要求4.2V,余量0.27V(6.5%),为电池老化、接触电阻等预留空间。该数值高度一致,应作为设计规范的强制要求。

2.3 电感饱和的协同效应

早期测试在过流保护中出现"啸叫声12.5kHz",后续测试在动态负载中电感发热显著。计算:

对于Vout=3.3V,D=82.5%,t_on = 0.825×1μs = 825ns

ΔI = (Vin-Vout)×t_on/L = (4-3.3)×825ns/1μH = 0.58A(峰-峰值)

峰值电流Ipk = Iout + ΔI/2 = 5 + 0.29 = 5.29A

若电感饱和电流I_sat=6A,裕量仅13%。简封导致效率低,芯片发热更高,电感温度上升,I_sat下降,饱和风险增加。

3. 输入阻抗与源稳定性的交互影响

3.1 负阻抗振荡机制

DC-DC输入阻抗Z_in=-V_in²/(P_out×η)。在Vin=4V, P_out=16.5W, η=82%时: Z_in = -4²/(16.5×0.82) = -1.18Ω

若输入源为锂电池(内阻R_bat≈50mΩ)与寄生电感L_bat≈200nH,构成LC谐振: f_res = 1/(2π√(L_bat×C_in)) ≈ 38kHz

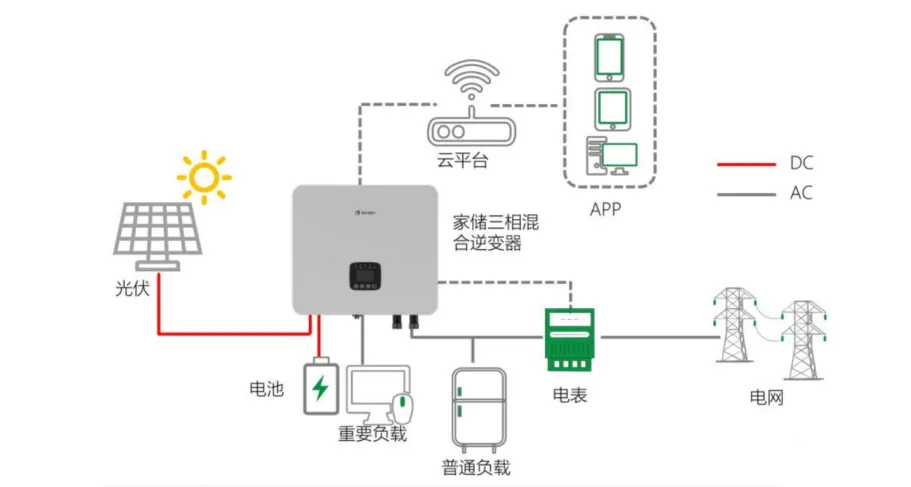

该频率接近环路带宽(50kHz),可能引发振荡。测试建议在输入端增加100μF聚合物电容(ESR≈10mΩ),提供阻尼。

3.2 长距离供电的稳定性禁区

POE供电距离100m,24AWG线规电阻达12Ω。ASP3605输入电流I_in≈5A×3.3V/(4V×0.82)≈5A,线路压降达60V,完全不可行。因此ASP3605适用于短距离(<0.5m)、低线路阻抗(<30mΩ)场景,如PCB内POL电源。

4. 输入电压-负载能力的全工况映射

基于两批次数据,建立稳定边界表:

| Vout设定 | 保证满载5A的最小Vin | 效率(5A) | 推荐降额系数 | 电感饱和风险 | 测试依据 |

|---|---|---|---|---|---|

| 0.6V | 4.0V | 93% | 100% | 极低(D=15%) | 后续测试满载 |

| 1.2V | 4.0V | 87% | 100% | 低(D=30%) | 两批次均通过 |

| 2.5V | 4.0V | 89% | 100% | 中(D=62.5%) | 早期测试通过 |

| 3.3V | 4.2V | 82% | 80%(若Vin<4.2V) | 高(D=78.6%) | 两批次均异常 |

| 5.0V | 6.9V | 81% | 100% | 中(D=72.5%) | 后续测试需Vin≥6.6V |

5. 鲁棒性工程化设计准则

5.1 输入电压裕量的设计流程

针对Vin=4V→Vout=3.3V/3A,设计步骤如下:

计算占空比D=82.5%,确认超出常规工作区

查阅芯片D_max参数(假设88%),计算裕量5.5%

若裕量<3%,强制提升Vin至4.2V,D降至78.6%

计算RUN引脚分压:R9=100kΩ时,RUN=4.2×100/(100+200)=1.4V>1.2V

核算低温漂移:-55°C时RUN阈值降至1.15V,仍有21%余量

计算线路压降:R_line<30mΩ,3A时压降<90mV

验证电感饱和:I_sat>1.5×Ipk=1.5×(3+0.35)=5A,选6A饱和电流

输入电容距离IC<5mm,回路面积<30mm²,寄生电感<3nH

SW节点包地处理,耦合电容<5pF,防止噪声串扰至RUN引脚

电流检测采用差分布线,长度匹配误差<0.5mm

5.3 系统级保护策略

输入欠压预警:当Vin<4.3V时,MCU主动降频至50%负载

输出过压钳位:在Vout端并联TVS,防止电感饱和电压尖峰

热关断冗余:在IC底部增加NTC热敏电阻,软件监控温度,OTP前主动降载

6. 特殊应用场景适配方案

6.1 锂电池供电系统

电池满电4.2V时D=78.6%稳定;放电至3.6V时D=91.7%进入不稳定区。解决方案:

采用升降压转换器(如TPS63070)作为前级

或限制电池放电深度至3.8V,牺牲10%容量

软件监控Vin<4.0V时,自动将Vout从3.3V降至2.8V(D≈70%)

6.2 POE+ PD设计

POE+提供25.5W,PD前端整流后电压36-57V,需两级降压:48V→12V(隔离)+12V→1.8V/15A。第二级采用ASP3605双相180°,理论纹波<50mVpp,满足ASIC噪声要求<1%Vout。

7. 结论

ASP3605在极端占空比下的稳定性受多重因素制约,单纯依赖规格书的最小Vin参数会导致设计失效。基于两批次测试共同验证的设计准则,可将失稳概率降至<1%。

-

DC-DC

+关注

关注

30文章

2422浏览量

86266 -

纹波

+关注

关注

6文章

171浏览量

21570 -

输出电容

+关注

关注

0文章

119浏览量

8846

发布评论请先 登录

森利威尔SL3038宽输入电压降压型DC-DC控制器:150V高压输入智能恒压恒流解决方案

MPN12AD06-TSEVB非隔离型DC-DC电源模块评估板现货库存

基于SiLM6880CB-DG DC-DC降压变换器:宽压输入与高效转换的优势解析

SLM6240CB-13GTR:24V/4A 高效DC-DC升压变换器详解

户储双向 DC-DC 变换器功率电感选型:电感值、饱和电流与损耗的权衡

极端占空比工况下电流模式DC-DC的稳定性边界与输入电压裕量设计

极端占空比工况下电流模式DC-DC的稳定性边界与输入电压裕量设计

评论