ADS556x 是一款高性能的 16 位 ADC 系列,采样率最高可达 80 MSPS。该器件支持第一奈奎斯特区输入频率的极高信噪比。装置 包含低频噪声抑制模式,将噪声从直流提升至约1 MHz。

除了高性能外,该设备还具备多项灵活功能,如 输出接口(双倍数据率 [DDR] LVDS 或并行 CMOS)以及 1 dB 步进的细致增益 直到达到6 dB的最大增益。

*附件:ads5560.pdf

创新技术,如DDR LVDS和不需要的内部参考 外部解耦电容已被用来显著节省引脚数量。这 创新带来了紧凑型的7毫米×7毫米48针VQFN封装。

该设备可以置于外部参考模式,VCM引脚表现为 外部参考输入。对于电力需求高的应用,ADS556x设备提供了 在较低采样率下实现关机模式和自动功率缩放。

该装置的工业温度范围为-40°C至85°C。

特性

- 16位分辨率

- 最大采样率:

- ADS5562:80 MSPS

- ADS5560:40 MSPS

- 全面力量:

- 865毫瓦,80 MSPS

- 674毫瓦,40 MSPS

- 没有缺失的代码

- 高信噪比:84 dBFS(3 MHz 中频)

- SFDR:85 dBc(3 MHz 中频)

- 低频噪声抑制模式

- 可编程细增益,1 dB 步进,直到

最大增益达到 6 dB - 双数据速率(DDR)LVDS和并行

CMOS输出选项 - 内部与外部参考支持

- 3.3伏模拟与数字电源

- 与ADS5547家族的针对针

- 48-VQFN封装(7.00毫米×7.00毫米)

参数

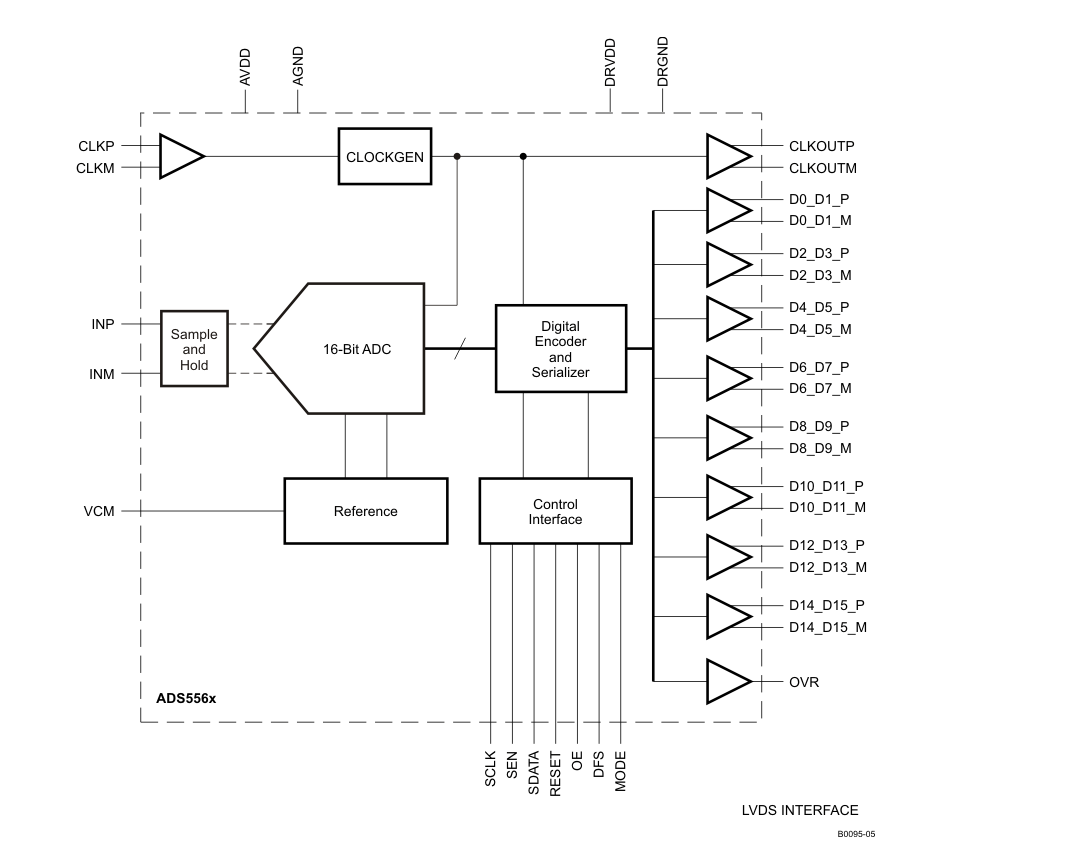

方框图

1. 产品概述

ADS556x系列是德州仪器(TI)生产的高性能16位模数转换器(ADC),包含两个型号:

- ADS5562:最高采样率80 MSPS

- ADS5560:最高采样率40 MSPS

2. 主要特性

- 分辨率:16位无失码

- 采样率:ADS5562达80 MSPS,ADS5560达40 MSPS

- 功耗:80 MSPS时865 mW,40 MSPS时674 mW

- 信噪比(SNR) :84 dBFS(3 MHz中频)

- 无杂散动态范围(SFDR) :85 dBc(3 MHz中频)

- 输出接口:支持双倍数据率(DDR) LVDS和并行CMOS

- 增益调节:可编程精细增益,1-dB步进,最大增益6-dB

- 封装:48引脚VQFN(7mm×7mm)

3. 应用领域

4. 技术规格

- 模拟输入:差分输入,电压范围3.56 VPP

- 电源要求:3.3V模拟和数字供电

- 工作温度:-40°C至85°C

- 参考电压:支持内部和外部参考模式

- 低频率噪声抑制:改善DC至约1 MHz的噪声性能

- 时钟输入:支持差分时钟信号,支持正弦波、LVPECL、LVDS和LVCMOS格式

5. 功能特点

- 灵活的输出选项:DDR LVDS或并行CMOS

- 引脚兼容:与ADS5547系列引脚兼容

- 功耗模式:提供待机模式和时钟停止模式

6. 封装与引脚配置

- 采用紧凑型48引脚VQFN封装

- 提供详细的引脚功能说明,支持LVDS和CMOS两种模式

7. 编程与控制

- 并行接口控制:通过DFS、MODE、SEN、SCLK和SDATA引脚直接配置

- 串行接口编程:通过SEN、SDATA和SCLK引脚访问内部寄存器

- 组合控制模式:支持串行接口和并行引脚组合配置

8. 典型应用

9. 布局建议

- 推荐良好的电源去耦

- 强调差分信号布线对称性

- 提供布局示例和热管理建议

该数据手册提供了从基本特性到详细应用设计的完整技术参考,适用于高速数据采集系统的设计与开发。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

CMOS

+关注

关注

58文章

6233浏览量

243407 -

电容

+关注

关注

100文章

6525浏览量

160101 -

MSPS

+关注

关注

0文章

574浏览量

29067 -

adc

+关注

关注

100文章

7946浏览量

556898 -

输出接口

+关注

关注

2文章

33浏览量

15010

发布评论请先 登录

相关推荐

热点推荐

ADS5560采样正弦波失真的原因?怎么处理?

目前使用xilinx的fpga在做ads5560的采集方案,出现了采集的正玄波数据失真的问题。

在ads5560配置成测试模式的时,数据与规格书里提到的

发表于 12-04 06:35

用ADS5560做数据转换,输出时钟的占空比不是50%,改变输入时钟频率占空比会变化,是正常的嘛?

现在用ADS5560做数据转换,使用单端输入时钟,18MHz,发现输出时钟的占空比不是50%,改变输入时钟频率占空比会变化,时钟频率越低,占空比越大,请问这是正常现象吗?手册中直接写的输出时钟的占空比是50%,求助

发表于 12-20 07:27

ADS5560不加输入的时候在差分输入端用示波器观察会发现有一个干扰是怎么回事?这是什么原因呢?

ADS5560不加输入的时候在差分输入端用示波器观察会发现有一个干扰是怎么回事?这是什么原因呢?

发表于 01-02 07:48

用FPGA配置ADS5562怎么确认寄存器是否配置正常?

1、用FPGA配置ADS5562怎么确认寄存器是否配置正常

2、输入时钟和输出时钟的延时怎样配置在合理的范围里

发表于 01-02 06:49

采用ADS5560作为ADC进行信号采集,数字端如果有负载对模拟端都会有较大干扰,如何解决?

采用ADS5560作为ADC进行信号采集,输入时钟为25MHz,测量发现:

数字端不接负载,模拟端噪声共模5mv以内。

数字端(特别是CLKOUT)如果有负载(即使是10k电阻),对模拟端(VCM

发表于 01-06 08:05

当ADS5560工作在DDR LVDS模式下,采样率为30MSPS时,对应的时钟延迟是多少?

ADS5560的DataSheet上只给出了在20MSPS和40MSPS采样率下,输入时钟到输出时钟的延迟,即t_PDI;请问,当ADS5560工作在DDR LVDS模式下,采样率为30MSPS时,对应的时钟延迟是多少?

发表于 02-13 07:50

ADS5562,pdf (16-Bit 40/80 MSPS

ADS556X is a high performance 16-bit A/D converter family with sampling rates up to 80 MSPS.

发表于 06-03 15:44

•23次下载

ADS5560/ADS5562EVM User's

1 Overview 11 ADS556xEVM Quick-Start Procedure 2 Circuit Description 21 Schematic Diagram 22 EVM

发表于 06-03 15:53

•2次下载

ADS5560,pdf (16-Bit 40/80 MSPS

ADS556X is a high performance 16-bit A/D converter family with sampling rates up to 80 MSPS.

发表于 06-03 15:55

•18次下载

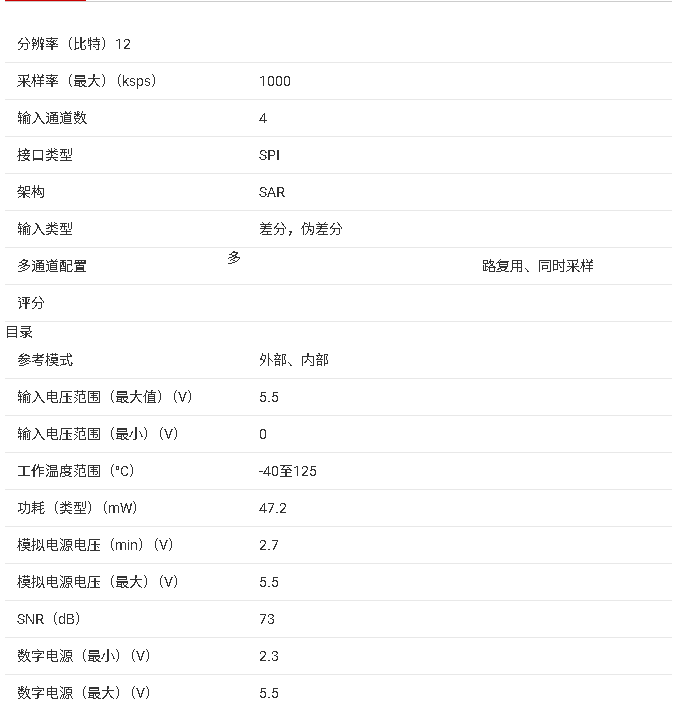

ADS7223 数据手册总结

该ADS8363为双16位、1MSPS的模数转换器(ADC),配备八个伪或四个全差分输入通道,分为两对,用于同步采集信号。模拟输入与ADC输入保持差分。输入多路复用器可采用伪差分模式,支持每个ADC

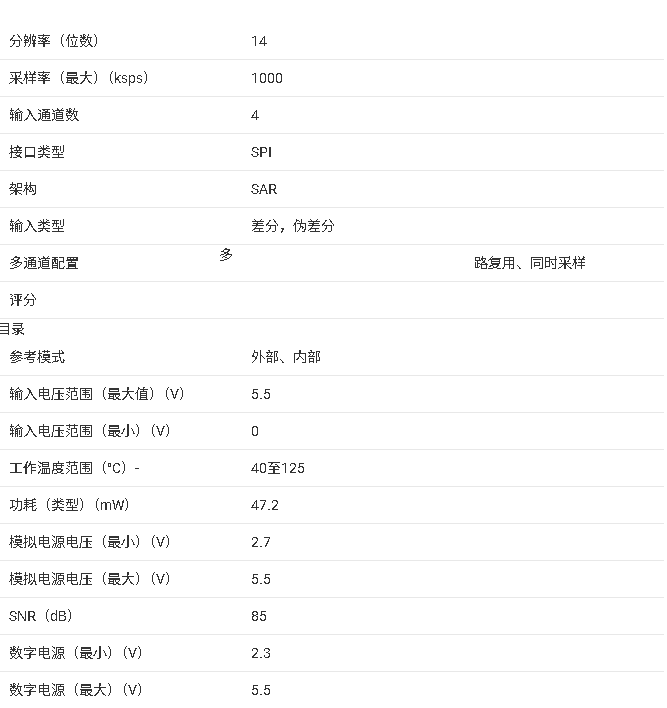

ADS7263 数据手册完整总结

该ADS8363为双16位、1MSPS的模数转换器(ADC),配备八个伪或四个全差分输入通道,分为两对,用于同步采集信号。模拟输入与ADC输入保持差分。输入多路复用器可采用伪差分模式,支持每个ADC

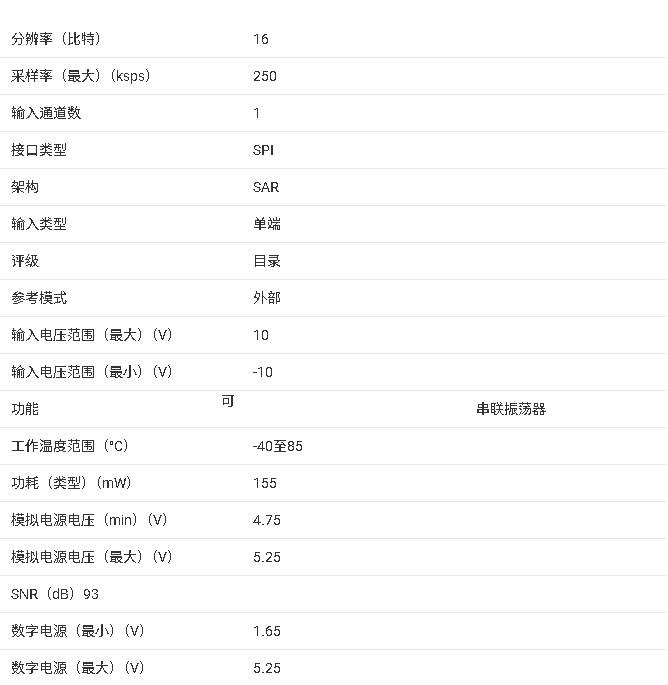

ADS8519 数据手册总结

该ADS8519采用了先进的CMOS结构,实现了完整的16位采样模数(A/D)转换器。它包含一个完整的16位、基于电容的逐次近似寄存器(SAR)A/D转换器,具备采样保持、参考、时钟和串行数据接口

ADS5560/ADS5562 数据手册总结

ADS5560/ADS5562 数据手册总结

评论