通信对抗是电子对抗的重要组成部分, 而通信对抗侦察是实施通信对抗的前提和基础, 是使用通信侦察设备探测、搜索、截获敌方无线电通信信号, 并对其信号进行测量、分析、识别、监视以及对敌方通信设备的测向和定位, 以截获其信号频率、电平、调制方式等技术参数以及电台位置、通信方式、通联特点、通信网结构和属性等情报。频率合成器是接收机中的一个关键部件, 它的性能直接决定了接收机的性能指标。而频率合成器中应用最广泛的就是锁相环频率合成器。在通信对抗侦察接收机中, 广泛应用锁相环频率合成器构成本地振荡器,它的性能指标在整个侦察系统性能指标中起着决定性的作用。本文介绍了利用美国国家半导体(NS) 公司的锁相芯片LMX2306 为核心器件设计的锁相环电路构成的频率合成器, 将其应用在通信对抗侦察接收机中, 通过PC 机控制, 实现其输出的频率在搜索频率范围之间进行步进自动搜索和按预置频率选频搜索以及在指定频率驻留的功能。

1 系统实现原理

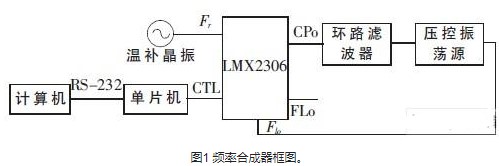

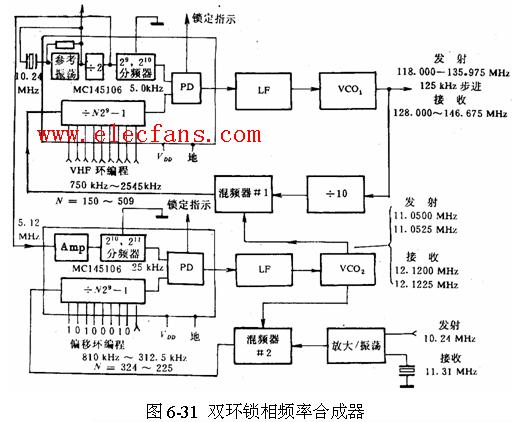

频率合成器原理框图如图1 所示。本系统基于锁相环原理, 利用12.8 MHz 的温度补偿晶振与压控振荡器MAX2606 的反馈信号经LMX2306 的分频、鉴相, 并经电荷泵和环路滤波器形成与相位差成比例的电压信号来控制压控振荡器MAX2306 的输出。单片机AT89S52 在上位机软件通过串行口接收搜索范围及搜索速度, 控制LMX2306 的锁定输出, 从而达到一本振扫描的目的。

2 LMX2306 的内部结构及控制方法

LMX2306 是NS 公司生产的一款单片集成的射频PLL 芯片, 使用了NS 公司的ABiC 第5 代BiCMOS 0.5μm 技术及数字锁相环技术, 可提供灵活的锁相环设计。

因此, 由LMX2306 构成锁相环, 只需结合高稳定度的本地参考振荡, 再外置环路滤波和压控振荡器(VCO) 及其他的外围电路即可实现频率的合成。

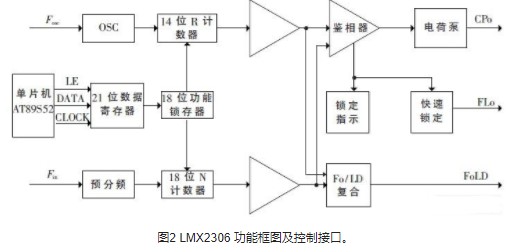

LMX2306 内置1 个分频比为8/9 的双模前置分频器( 以P 表示)、1 个程序分频器(N) 、1 个参考分频器(R)和数字鉴相器(PD) , 并自带锁相检测指示(Lock Detect) 、电荷泵输出等。LMX2306 本地参考基准时钟频率为5 MHz ~40 MHz , 最大鉴相频率为10 MHz , 射频输出工作频率为25 MHz~550 MHz , 工作电源从2.3 V~5.5 V。LMX2306 的优势之一是能提供灵活的分频系数, 可通过CPU 接口实现对其不同的设置。其功能框图如图2 所示。

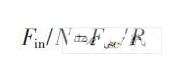

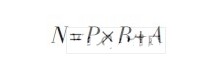

根据图2 可得:

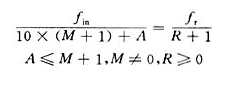

式中,R 为14 位可编程参考分频器的分频比, 分频比为3~1 683 ,LMX2306 预分频比P 固定为8;N 为18 位程序分频器的分频比,N 由5 位吞吐分频器A 和13 位可编程分频器B 构成,A 分频范围:0~7(A

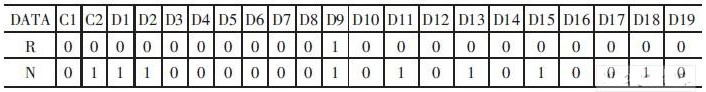

单片机AT89C52 的P1 口作为锁相环的输出端口,P1.7 、P1.6 、P1.5 口分别对应LMX2306 的LE( 使能端, 低电平有效)、DATA( 数据输入脚)、Clock ( 时钟输入端, 上升沿有效)。从Data 脚输入的频率控制字共21 位, 其中低两位是地址位为C1、C2,00 表示输入数据设置R 分频器,01 表示输入数据设置N 分频器; 高19 位是数据位D1、D2……D19 , 在Clock 信号配合下按位输入, 按D19 、D18……D1 及C2、C1 的顺序输入, 在LE 的上升沿锁存到21 位数据寄存器中。其中,R 分频器有效数据位为D1 ~D14 , 最大分频比为16 383 ; 数据位D1 ~D5 配置N 分频器的吞吐分频器A 最大分频比为7, 数据位D6~D18 配置N 分频器的可编程分频器B 最大分频比为8 189 。在本系统中, 参考晶振频率为12.8 MHz , 信道间隔为25 kHz。若要求本振锁定输出为120 MHz,由式(1) 、式(2) 得R=12.8 MHz/25 kHz =512 ,N=120 MHz/25 kHz =4 800,A=3,B=4 776。具体DATA 管脚的输出如表1 所示。

表1 LMX2306 控制字表

3 环路滤波器的设计

在频率合成器的设计过程中, 环路滤波器的选择和设计是必不可少的, 也是整个设计成功与否的关键。因为: ( 1 ) 目前在频率合成器设计中, 鉴相器和压控振荡器采用的都是集成器件, 一般只要在选择的器件中注意其性能指标的匹配就可以了, 只有环路滤波器是自己计算设计的;(2)最重要的原因是环路滤波器可以滤除由鉴相器输出的误差电压的高频分量和噪声, 且对环路参数调整起着决定性的作用。

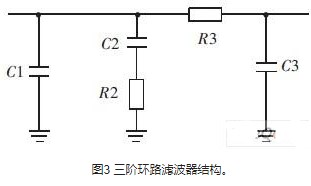

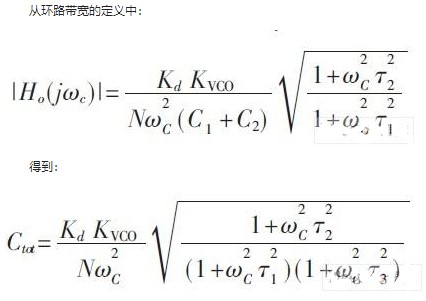

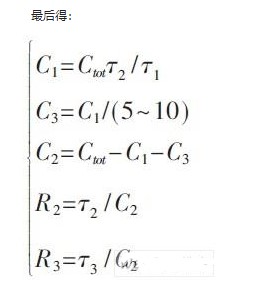

环路滤波器由电阻、电容以及放大器组成, 可分为无源环路滤波器和有源环路滤波器两类。有源环路滤波器在无源环路滤波器增益不足的情况下可以加大环路增益,但从锁相环系统的角度, 有源和无源环路滤波器没有区别, 都是具有一定数量的零点和极点的低通滤波器。而对于有电荷泵的锁相环,有源滤波器毫无必要, 反而会引入更多的噪声, 所以电荷泵锁相环都采用无源环路滤波器, 常用的有二阶或三阶无源滤波器, 而三阶环路滤波器与二阶环路滤波器相比, 能更好地滤除参考源的边带频率, 所以应用更为广泛。三阶环路滤波器的结构图如图3 所示。

其中C3可以自由的给定, 但至少要小于C1/5。C2取得较大有两个好处: 一是给后面的VCO 一定的输入电容, 可使寄生影响减小; 二是可以减小R3, 使得热噪声减少。

在设计中, 根据计算及工程经验来确定环路滤波器各元件的参数值。

4 电路设计及测试

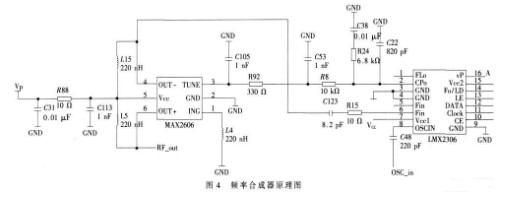

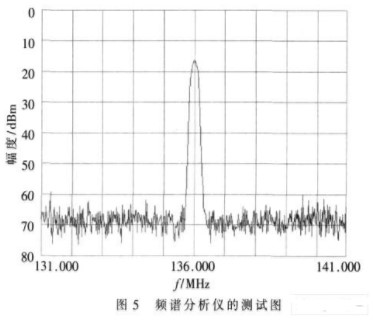

由理论计算得频率合成器电路图如图4 所示, 用GSP810 频谱分析仪在锁定输出为136 MHz 时所得的频谱分析仪的测试图如图5 所示, 经测试频率合成器的主要技术指示如下:

频率准确度:±10 ppm; 输出信号功率:17±1 dBm; 单边带相位噪声:<-63 dBc/Hz@10 kHz 。

-

芯片

+关注

关注

462文章

53539浏览量

459158 -

振荡器

+关注

关注

28文章

4155浏览量

142324 -

频率合成器

+关注

关注

5文章

305浏览量

33414

发布评论请先 登录

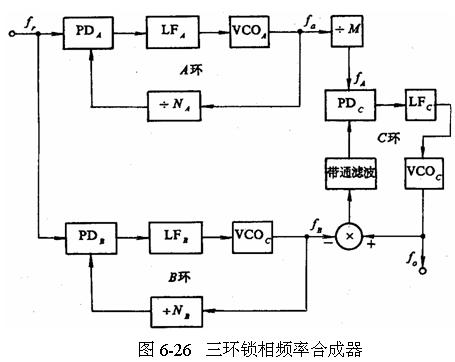

详解频率合成器高性能架构的实现

LMX2502/LMX2512铂™ 集成压控振荡器频率合成器系统

2.3V至5.5V的LMX2306/16/26频率合成器

基于DDS芯片和集成锁相芯片构成的宽频合成器设计

基于集成锁相环频率合成芯片PE3236实现锁相式频率合成器的设计

基于锁相芯片LMX2306实现频率合成器的设计及应用

基于锁相芯片LMX2306实现频率合成器的设计及应用

评论