基于砷化镓集成无源器件(Integrated Passive Device,IPD)工艺,研制出了一款性能优良的K波段发夹型带通滤波器芯片,测试结果表明:在19.5~21.3 GHz频带内,该芯片滤波器的插入损耗<2.6 dB,最小插入损耗为20 GHz处2.2 dB, 带内输入输出回波损耗<-25 dB,群时延波动<50 ps, 测试结果与仿真设计十分吻合。该滤波器尺寸仅为2.96 mm×1.8 mm×0.1 mm,相比传统工艺的微波滤波器,体积大大缩小,符合当前通信、雷达等微波系统中器件小型化的发展趋势,具有广阔的应用前景。

0 引言

随着当代半导体工艺与器件的日趋改善与进步,得益于系统级封装(System In Package,SIP)的集成架构与设计思路,当代雷达、通信、电子战等微波系统朝着小型化、高密度集成、高可靠性、低成本等方向发展,因此对微波系统中器件与模块提出了更高的要求。

微波滤波器作为微波系统中重要的无源器件,在射频前端应用广泛,其各项指标很大程度地影响着微波系统的整体指标。在(亚)毫米波频带的实际工程应用中,PCB、LTCC、腔体等传统工艺制造的滤波器[1-3]由于其相对尺寸过大、加工精度、量产一致性及难以与系统集成等问题已无法满足当代微波系统小型化与高性能的要求,而当前采用体声波和声表面波技术的MEMS滤波器[4-5]虽然拥有较小的尺寸和不错的量产能力,但是由于材料与工艺的限制,其实际应用的频段目前主要在C波段以下,无法满足更高频率的微波系统的需求。

GaAs作为第二代半导体材料,采用GaAs衬底的高电子迁移率晶体管(High Electron Mobility Transistor,HEMT)等有源工艺制造的如功放、移相器等有源芯片早已大量应用在各军用及民用微波系统中。在无源器件的实现上,得益于GaAs衬底极低的介质损耗(为万分之一量级)和微电子工艺制程,采用GaAs衬底IPD工艺制造的如滤波器、功分器、耦合器等器件具有较高的性能与加工精度、较小的体积、优秀的量产一致性,因此十分适合于微波毫米波系统中的大规模应用。

本文则是基于国内某GaAs IPD工艺线,研制出了一款K波段带通芯片滤波器,体积仅为2.96 mm×1.8 mm×0.1 mm,比原有采用传统工艺制造的器件,体积缩小了约80%,实现了无源器件的小型化,其相应的性能指标完全满足系统需求。

1 工艺简介

为了使微波无源器件在GaAs衬底上集成,本项目的IPD工艺使用先进和高成品率的微电子制造过程,其工艺典型的无源器件的衬底模型示意图如图1所示。

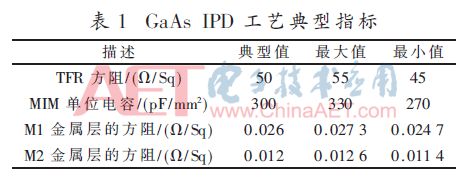

图1中底部的100 μm的GaAs为整个集成无源器件的衬底介质,再通过若干如光刻、显影、溅射、剥离、金属蒸镀、刻蚀等微电子工艺即可在衬底上面形成一系列的金属、电介质、过孔等多层结构,可形成不同的基本无源元件如MIM(Metal-Instric-Metal)电容、螺旋电感、TFR(Thin Firm Resistor)电阻等,该IPD工艺的典型参数指标如表1所示。

2 带通滤波器设计

2.1 耦合矩阵综合

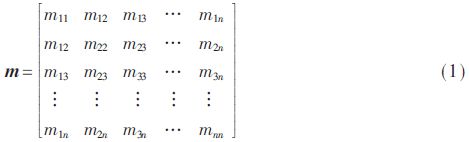

根据滤波器耦合矩阵的理论[6],无论何种结构的微波滤波器,其电特性参数由其耦合系数矩阵m和外部品质因素QE所决定,n阶滤波器的典型广义耦合矩阵如式(1)所示:

因为滤波器为互易无源器件,所以式(1)的滤波器广义耦合矩阵是对称的,其中mii为各个谐振器频率的相对偏移,对于同步调谐的滤波器来说,mii=0;mij为谐振器间的互耦合系数,其与耦合强度成正相关关系,决定了滤波器的相对带宽大小。实际应用中,需要将广义耦合矩阵通过式(2)转换成狭义耦合矩阵:

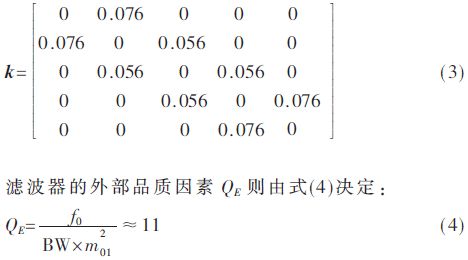

式中,f0为滤波器的中心频率,BW为滤波器的带宽。结合实际项目中对滤波器的指标要求:中心频率为20.4 GHz、带宽大于1.8 GHz,并需要较高的带外抑制,拟采用5阶契比雪夫响应的形式来实现,结合CoupleFil滤波器矩阵综合软件和式(2)可以确定该滤波器的狭义耦合矩阵如式(3)所示。

2.2 电路原理图设计

2.2.1 谐振单元的确定

在确定了滤波器的狭义耦合矩阵和外部品质因素后,需进行具体的电路设计。根据微波滤波器基本理论知识[6],可采用1/2介质波长的开路微带线作为基本谐振单元,为了减小滤波器的插入损耗即需要提高单个谐振器的Q值,微带线损耗即影响谐振器Q值的主要因素为其导体损耗,导体基本的电阻计算公式为:

式中,ρ为导体的电阻率,L为导体长度,h和w分别为导体横截面的厚度和宽度。可知在导体电阻率e和长度L确定的条件下,要想减小微带线的导体损耗主要有两种方法:第一种方法就是增加导体的厚度,结合本IPD的工艺特性,可选择M1+M2两层导体(其中M1层厚1 μm,M2层厚2 μm)同时走线方式,即将M1与M2层之间的SiN刻蚀后金属化填充,使总导体厚度达到该工艺目前的3 μm的最大值;第二种方法则是增加导体的宽度,结合Txline软件可计算出在频率20.4 GHz处,100 μm厚的GaAs衬底上的特征阻抗为50 Ω,半波长的微带线的宽度和长度分别约为70 μm和2 600 μm。因此在实际设计中考虑采用宽度更大即特抗阻抗更低的微带谐振器作为谐振器单元,为了节约版图面积即实现滤波器的小型化,将微带开路谐振单元设计成U型的发夹结构。

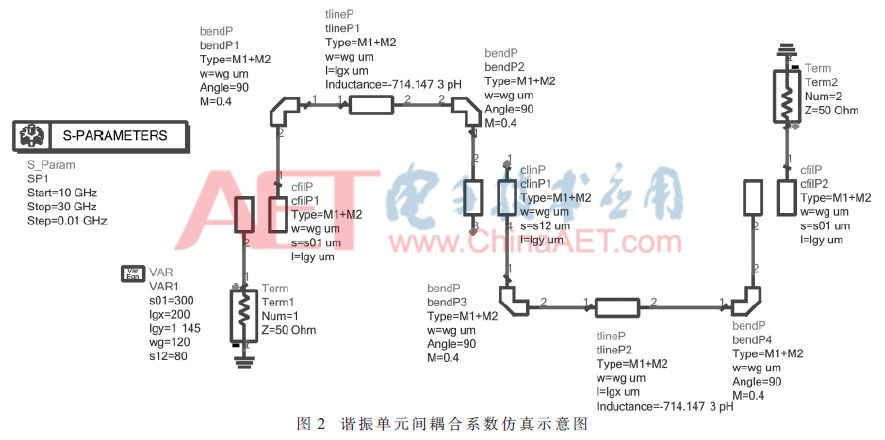

2.2.2 耦合系数的仿真

在确定了滤波器基本谐振单元的尺寸后,需要根据狭义耦合系数矩阵和外部品质因素来综合出各个谐振器间的实际物理尺寸,发夹型微带谐振器单元间主要通过缝隙耦合,以1和2谐振单元为例,谐振器间的耦合系数仿真示意图如图2所示。

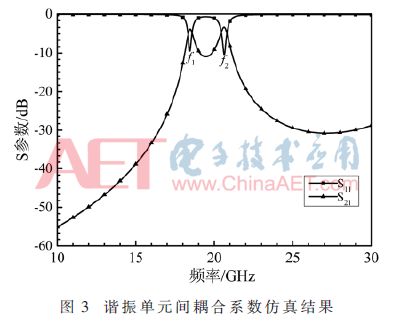

影响发夹谐振器间耦合系数的因素即为两个发夹谐振单元的缝隙(即如图3中的S21变量),仿真初值为80 μm,仿真结果如图3所示。

从图3的S参数仿真结果可知,其仿真曲线有两个谐振尖峰点f1和f2,分别为18.46 GHz和20.62 GHz。为了使源和负载耦合效应对谐振单元间耦合的影响最小化,仿真过程中尽可能加大图中源端和负载端微带与谐振单元间的缝隙(即图3中的S11变量),使得两个谐振尖峰频率不随S11变量的变化而变化为止。谐振器间耦合系数的综合近似公式为:

根据图3的仿真结果和式(6),对比式(3)的狭义耦合矩阵,可知其耦合系数比理想值偏大,耦合过强,因此要适当增加两个谐振单元的缝隙以降低两者的耦合强度。由于本滤波器采用输入输出完全对称的结构,同理只需再对谐振器2和3之间进行仿真,调节两者间的耦合系数,以满足理论的耦合系数值,即可得到5个谐振单元间缝隙大小的初值。

2.2.3 外部品质因素的仿真

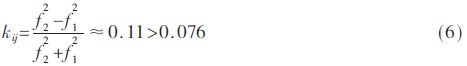

在确定完各谐振单元间的耦合缝隙大小即耦合系数后,需要通过改变滤波器输入输出馈电位置来调节其外部品质因素的大小,外部品质因素原理图仿真示意图如图4所示。

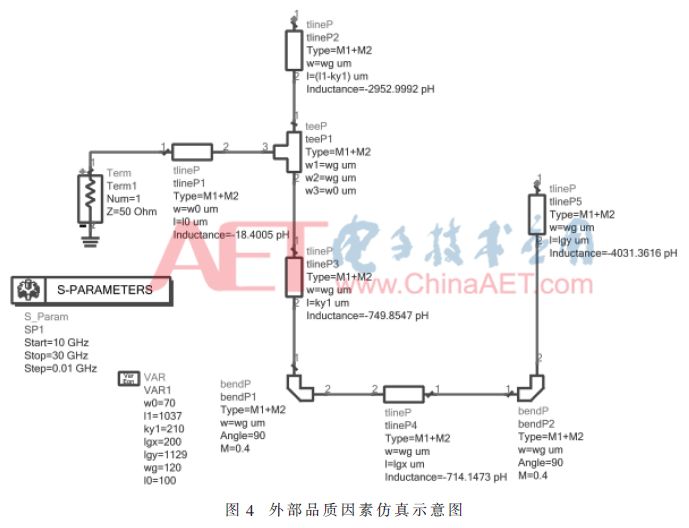

在谐振单元确定的情况下,采用特征阻抗50 Ω即宽度为70 μm的微带线进行直接馈电,其外部品质因素由图4中的ky1参量即馈电点距离发夹谐振器底部的距离来决定,图4的仿真结果如图5所示。

图5中f0为单个发夹型谐振器的谐振频率即20.38 GHz,f1和f2分别为S11相位与谐振频率点处相差±90°的两侧频点,分别约为19.31 GHz和21.45 GHz,频域法的外部品质因素估算公式为:

即外部品质因素约等于谐振点处频率f0除以两侧与f0相位各相差90°频点的差值,图5中ky1等于210 μm时,计算得出的Qe为9.5要小于理论值的11。因此需要进一步调节馈电点的位置,即ky1的值以满足初步理论的指标要求,最终各参数的值见下文。

2.3 版图的仿真与设计

由于上节基于原理图和耦合矩阵理论提取的初步尺寸只是针对单个或两个谐振器而言的,而忽略了其他谐振单元耦合效应的影响, 同时原理图相对简单的电路级仿真已无法准确地预测K波段下的电磁场结果,原理图仿真的尺寸参数只能作为版图设计的参考初值,与最终实际物理尺寸可能存在一定甚至是较大的偏差。因此鉴于GaAs IPD工艺具有精准的电磁(EM)仿真模型,在上节综合出滤波器各单元结构的初步尺寸后,可直接根据该IPD的工艺设计规则和模型进行基于Momentum的芯片滤波器整体版图仿真与设计。

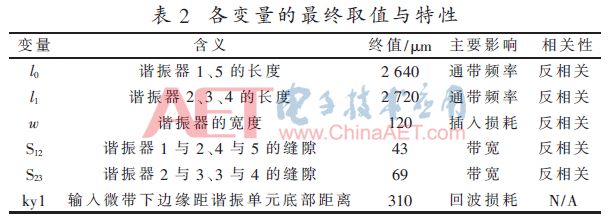

版图设计时主要需参考整体原理图的仿真结果和耦合矩阵理论,对影响滤波器性能的主要参数即各谐振器的长度(l)、宽度(w)、谐振单元间的耦合缝隙(S12和S23)、输入输出馈电点的位置(ky1)进行调节,进而找到上述变量对滤波器的插损、带宽、通带范围等特性影响的变化趋势,并且需在芯片尺寸与整体性能做出一定的折中,这是一个不断迭代的过程,最终上述各参数调节后的取值及对滤波器特性主要影响关系见表2。

最终流片的版图如图6所示,芯片尺寸为2.96 mm×1.8 mm×0.1 mm。

3 实物与测试结果

其他微电子工艺如Si CMOS、GaAs HEMT等有源芯片的流片时间长达3~5个月,而基于GaAs IPD工艺的无源MMIC由于其日趋成熟稳定的工艺与纯无源结构,具有较快的流片周期,典型的流片时间仅为20天,十分符合现代快速的科研生产需求。最终本文研制的小型化K波段带通滤波器芯片实物如图7所示。

滤波器芯片采用Keysight公司的N5247A矢网和Cascade公司的ACP系列的GSG-150探针进行测试,实测与仿真结果对比如图8所示。

从图8可知,该滤波器芯片实测与仿真结果吻合度很好,验证了该工艺模型的准确性。图8(a)的S参数测试结果表明,在通带19.5-21.3 GHz内,其插入损耗最小值约2.2 dB,最大值2.6 dB,回波损耗小于-25 dB,匹配效果十分良好,其在带外15.5 GHz与26.8 GHz处的带外抑制已达到50 dB。图8(b)群时延测试结果表明,该滤波器的带内群时延约为360~405 ps,群时延波动小于50 ps,具有很好的相位响应。

为了验证IPD工艺的稳定与一致性,随机抽取本次流片的5块芯片分别进行单独测试,最终各芯片测试结果如图9所示。

从图9可知,随机抽取的各滤波器芯片的测试结果十分吻合,难以辨别出测试结果的差异,进而证明了该工艺的成熟与稳定,十分符合对于一致性要求较高的批量化应用。

4 结论

本文设计并实现了一款基于GaAs IPD微电子工艺的发夹型K波段带通滤波器芯片,该滤波器拥有优良的性能和一致性,且相比采用传统LTCC、薄膜、PCB工艺研制的滤波器,体积大大减小,实现了器件的小型化,目前已代替传统滤波器在某毫米波通信项目中直接应用,该GaAs IPD工艺也为今后微波毫米波系统中其他无源器件的小型化指明了一个新的方向。

-

滤波器

+关注

关注

162文章

8355浏览量

184776 -

GaAs

+关注

关注

3文章

893浏览量

24809 -

IPD

+关注

关注

4文章

90浏览量

27352

原文标题:【学术论文】基于GaAs IPD的K波段芯片滤波器

文章出处:【微信号:ChinaAET,微信公众号:电子技术应用ChinaAET】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

P波段腔体滤波器的小型化设计

滤波器设计资料集锦

X波段微带带通滤波器的设计介绍

L波段发夹型微带滤波器的设计

详解FIR滤波器和IIR滤波器的区别

基于椭圆函数的LC带通滤波器设计与仿真

一种新型小型化K波段带通滤波器的设计解析

高通正式推出了ultraSAW滤波器

正交镜像滤波器的详细资料介绍

如何实现一种UHF波段带通滤波器的设计资料说明

基于GaAs IPD的K波段滤波器芯片的设计资料分析总结

基于GaAs IPD的K波段滤波器芯片的设计资料分析总结

评论