文章来源:老虎说芯

原文作者:老虎说芯

本文介绍了CoWoP(Chip‑on‑Wafer‑on‑Substrate)封装的概念、流程与优势。

什么是 CoWoP?

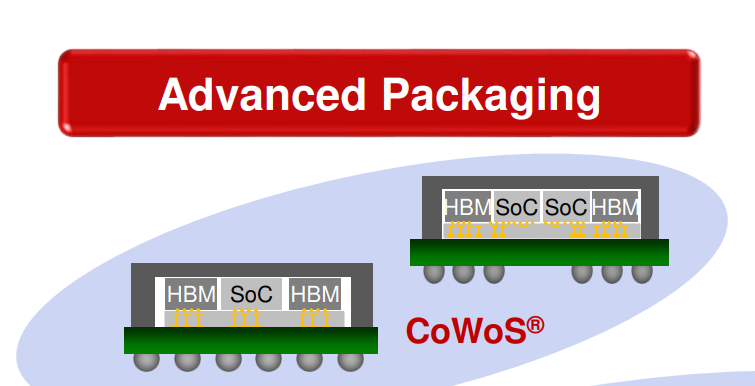

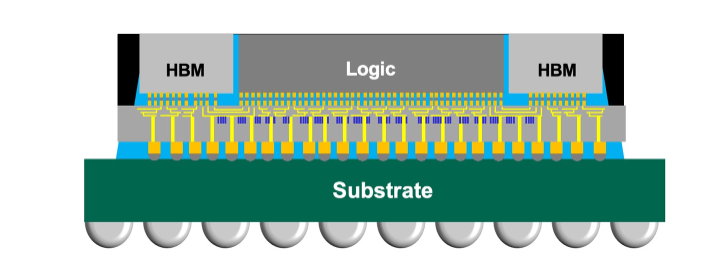

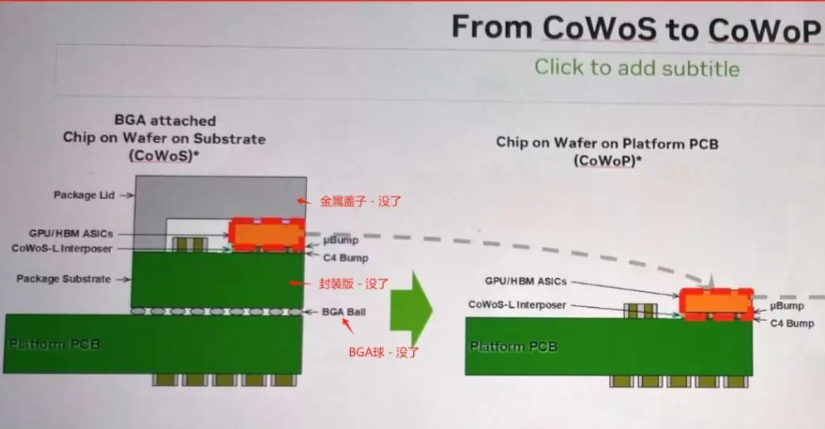

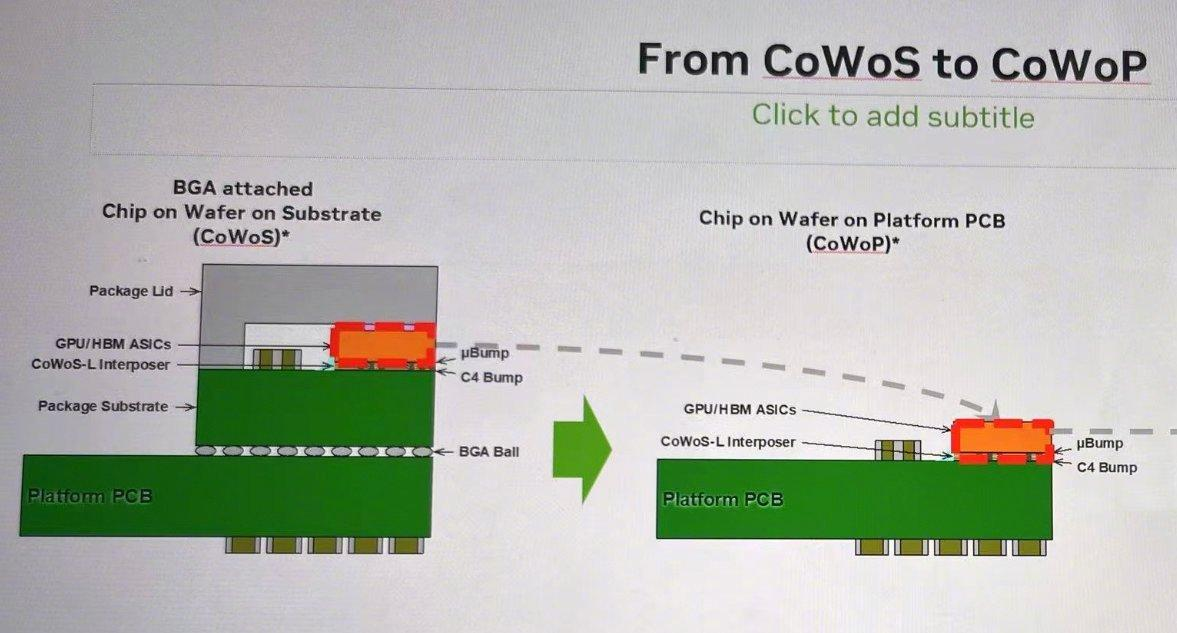

CoWoS(Chip‑on‑Wafer‑on‑Substrate):传统先进的 2.5D 封装,将硅芯片(Logic + HBM)并排贴在一个中介层(硅 Interposer)上,再焊接到封装基板(Package Substrate),然后用 BGA 焊球连接到主板。

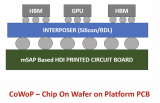

CoWoP的核心思路就是把这个封装基板去掉 ——CoWoP = CoWoS - 封装基板。中介硅片 + 芯片直接安装在增强型主板上,不再走传统封装那一层。

为什么这么做?CoWoP 有什么好处

省掉中间层,降低信号损耗

封装基板那层走线、引线、接触都会带来寄生电阻、电容。去掉后,逻辑芯片对高带宽连接(如 NVLink)更可靠、更远、更快。

热性能更强

没有封装基板那块厚材料,封装热膨胀系数配合更一致、热堆栈更薄,散热更直接、更好控温,减少板变形(warpage)。

成本下降

去掉封装底板和封装盖,少了材料、工艺、BGA焊球等制造步骤,潜在节约封装成本,同时也减轻整体厚度、体积。

CoWoP 的关键技术要点

主板(Platform PCB)必须升级

PCB 上要具备过去由封装 substrate 提供的高密度布线能力,包括精准微线距、精准信号/电源/地层布线能力。

中介层(Interposer)依然重要

包含 GPU 核心和 HBM 等小 die,放在高精度硅片 interposer 上,保持高带宽连接能力。

可靠力学与热匹配设计

硅 interposer、die 与 PCB 的热膨胀系数(CTE)必须匹配,避免因热循环导致 warpage 或失效。

信号电气完整性管理

PCB 与 interposer 对高速信号(如 NVLink、HBM RDL)路径需要严格控制阻抗、延迟、电容、电感分布。

系统流程概览(从传统到 CoWoP)

| 阶段 | CoWoS 流程 | CoWoP 流程 |

|---|---|---|

| 封装结构 | Die → Interposer → Package Substrate → BGA → PCB | Die → Interposer → 直接贴装到 PCB(平台 PCB) |

| 制造复杂度 | 多层焊接、BGA、substrate 工艺 | PCB 信号层复杂化,封装 substrate 去除 |

| 信号路径 | die→sub→BGA→PCB,中间寄生多 | die→PCB 路径短,直接布线更低寄生 |

| 热管理 | 封装基板热阻仍存在 | 板子薄、无盖封装,热阻更小,散热更好 |

| 成本 | 封装 substrate + 材料费高 | 省掉 substrate,节省封装成本 |

CoWoP 是在先进 AI 封装中,去掉了封装基板这一层,把 die + interposer 直接贴到平台 PCB 上,借力 PCB 本身承接 substrate 功能,让信号更快、热阻更小、成本更低,但要求 PCB、设计和热机械一体化的集成度非常高。

CoWoP对半导体产业链的影响

1、封装模式变革:需求迁移与供应链重构

从CoWoS‑S 向 CoWoS‑L 或 CoWoP的转变,意味着对封装基板层的大幅调整。

CoWoS 能力长期供不应求,CoWoP 的推广可能部分缓解这一瓶颈,特别是若 CoWoP 能有效替代部分 CoWoS-S 产能需求 。

建立多元化的封装供应链,减轻对 CoWoS 的依赖。

2、对封装、PCB、PCB 材料与制造合作伙伴的挑战

CoWoP 将封装 substrate 功能迁移到平台 PCB,这要求 PCB 厂商升级生产工艺:更细线距、高密度线路、多层电源地层、低热膨胀系数材料等。

原先制作封装 substrate 的企业,可能转向更多 interposer 的测试与组装环节,或扩展业务至高精度 PCB 领域。

3、封装供应商与功耗相关链条的重新布局

传统 CoWoS substrate 供应商业务可能减少,而提供硅中介层(interposer)的需求将持续增长。

HBM 高带宽内存供应商由于 CoWoP 依然使用 HBM,与封装 interposer 集合,因此对 HBM 的依赖继续强化,市场需求和价格仍上涨趋势明显。

4、研发挑战与联盟协同升级

CoWoP 要求 PCB 与 interposer、die 一体设计,信号、电源、热管理、机械力学需协同工程化实现。这推动设计工具商、EDA、材料商、PCB 厂商共研新规范。

封装技术更新加快,CoWoP 与 CoWoS‑L、FOPLP(扇出面板级封装)形成互补和竞争。这对封装厂商提出更高要求,也创造新的合作空间 。

5、小结

CoWoP 带来的最核心影响是:将封装 substrate 的功能重置到主板层,推动 PCB 制造商、设计工具、材料供应商与传统封装厂商重新协作,重构 AI 封装与供应链生态。它不仅可能缓解 CoWoS 的产能瓶颈,还将推动封装与板级供应链迈向更高集成度和设计协同性时代。

-

芯片

+关注

关注

462文章

53592浏览量

459817 -

半导体

+关注

关注

336文章

30043浏览量

258961 -

封装

+关注

关注

128文章

9154浏览量

147968

原文标题:CoWoP(Chip‑on‑Wafer‑on‑Platform)封装是什么

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

简单认识CoWoP封装技术

最近大火的CoWoP跟CoWoS、CoPoS有什么区别?

芯片封装测试流程详解ppt

层叠封装技术的发展道路和概念

NB-IoT的概念及优势

STM32的中断系统基本概念

HLS/HLV 流程说明及优势

形式验证入门之基本概念和流程

CoWoP能否挑战CoWoS的霸主地位

CoWoP封装的概念、流程与优势

CoWoP封装的概念、流程与优势

评论