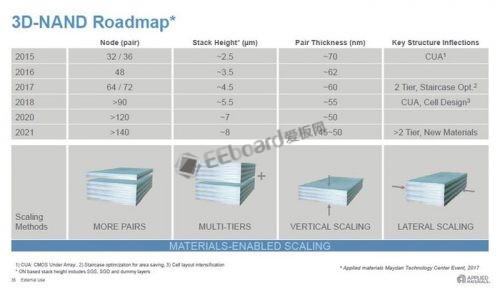

在正在举行的国际存储研讨会2018(IMW 2018)上,应用材料公司Sean Kang介绍了未来几年3D-NAND的发展线路图,到了2021年,3D-NAND的堆叠层数会超过140层,而且每一层的厚度会不断的变薄。

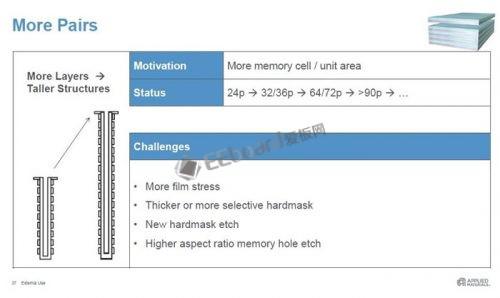

身在日本的PC Watch前往了本次会议的研讨会,自3D-NAND诞生以来它的堆叠层数就在不断的增长,三星造出来的第一代3D V-NAND只有24层,下一代就变成了32层,随后就变成48层,到了现在大多数厂商都是64层,而SK海力士则是72层,而下一代的3D-NAND堆叠层数将超过90层,再下一个阶段会超过120层,到了2021年会超过140层。

而闪存的Die Size也随着堆叠层数的增长而增长,在32层时代的时候是128Gbit,48层时256Gbit,64/72层是512Gbit,明年的96层闪存应该会达到768Gbit,128层应该会有1024Gbit的Die Size,达到144层时就不清楚会有多大了,肯定会大于等于1024Gbit。

在堆叠层数增加的时候,存储堆栈的高度也在增大,然而每层的厚度缺在缩小,以前的32/36层3D NAND的堆栈厚度为2.5μm,层厚度大约70nm,48层的闪存堆栈厚度为3.5μm,层厚度减少到62nm,现在的64/72层闪存堆栈厚度大约4.5μm,每层厚度减少到60nm,没升级一次堆栈厚度都会变成原来的1.8倍,而层厚度会变成0.86倍。

现在各家厂商都在3D NAND上加大力度研发,尽可能提升自己闪存的存储密度,此前东芝与西数就宣布计划在今年内大规模生产96层堆叠的BiCS4芯片,并会在年底前发货。

-

闪存

+关注

关注

16文章

1883浏览量

117010 -

可制造性设计

+关注

关注

10文章

2065浏览量

16364 -

3D-NAND

+关注

关注

0文章

4浏览量

2806 -

华秋DFM

+关注

关注

20文章

3512浏览量

6150

发布评论请先 登录

叠层固态电容的性能优势

贴片电感代理-叠层电感的实际应用

SK海力士321层4D NAND的诞生

实用电气控制线路图册

HDMI2.0滤波保护叠层共模滤波器介绍

天合光能钙钛矿晶体硅叠层技术再破世界纪录

芯片3D堆叠封装:开启高性能封装新时代!

Sean Kang介绍未来几年3D-NAND的发展线路图,2021年堆叠层数会超过140层,而且会不断变薄

Sean Kang介绍未来几年3D-NAND的发展线路图,2021年堆叠层数会超过140层,而且会不断变薄

评论