文章来源:学习那些事

原文作者:小陈婆婆

半导体封装正快速走向“堆叠+融合”:PoP把逻辑和存储垂直整合,先测后叠保良率;光电路组装用光纤替代铜线,直接把光SMT做进基板。两大技术同步突破,本文分述如下:

PoP叠层封装

光电路组装技术

PoP叠层封装

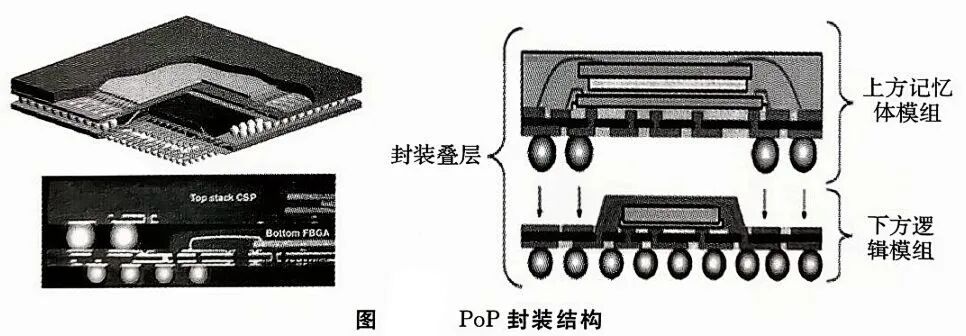

半导体封装技术正朝着高频模块、多芯片模块(MCM)、系统级封装(SiP)及堆叠封装(如PoP)方向加速演进,传统封装与电路板装配的界限日益模糊,形成半导体装配与传统PCB装配的深度集成。其中,封装体叠层技术(Package On Package, PoP)凭借其独特的结构优势与工艺特性,已成为3G/4G/5G移动终端、数码相机、AI芯片模块等高集成度场景的优选方案,并在2025年持续推动着封装工艺的革新与成本优化。

PoP的核心特征在于通过垂直堆叠实现逻辑运算单元与存储单元的紧密集成,通常采用2~4层逻辑+存储组合,存储型PoP甚至可达8层堆叠。

这种结构不仅显著提升了逻辑运算功能与存储空间密度,更通过“先测试后堆叠”的工艺路径实现了更高的良品率——各层器件在堆叠前可独立测试,有效降低了因单颗芯片失效导致的整体封装报废风险,从而控制了总体生产成本。相较于器件内置器件(PIP)技术,PoP赋予终端用户更大的器件组合自由度,无需受限于设计公司的固定存储结构,适配性更强,尤其契合移动终端对小型化、高性能与成本敏感的复合需求。

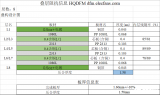

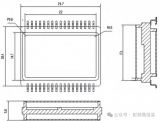

从工艺实现层面看,PoP底部通常采用PSvfBGA(Package Stackable very thin fine pitch BGA)作为基座,顶部则搭载Stacked CSP(如FBGA或fine pitch BGA)。典型SMT流程中,顶层CSP需通过助焊剂浸蘸或锡膏转移工艺完成装配,替代传统锡膏印刷以避免设备冗余与工艺复杂化。此过程中,焊球高度、间距及器件间隙的精确控制成为关键——回流前需确保顶部器件底面与底部器件顶面的间隙满足模塑高度(0.27~0.35mm)要求,回流后则需监控焊球高度与间隙的稳定性,以避免应力集中引发的可靠性问题。影响这些尺寸的因素涵盖焊盘设计、焊球尺寸公差、贴装精度、回流环境温度曲线、助焊剂/锡膏蘸取量、元器件及基板翘曲变形等多个维度,需通过多参数协同优化实现封装可靠性与良率的平衡。

当前行业最新进展显示,PoP技术正朝着更高集成度、更薄厚度与更优热管理方向突破。例如,采用超薄模塑材料与低应力焊料,可将单层模塑高度压缩至0.25mm以下,支持8层以上存储堆叠;通过引入热界面材料(TIM)与微型热管结构,有效缓解高功率芯片堆叠下的热集中问题;同时,结合AI驱动的工艺仿真与在线检测技术,可实时优化贴装精度与回流参数,将良率提升至99.5%以上。此外,PoP在汽车电子、物联网模块等新兴领域的渗透加速,如ADAS芯片与高带宽存储器的堆叠封装,以及边缘计算节点中SiP与PoP的混合集成方案,均体现了该技术在跨领域应用中的灵活性与扩展性。

展望未来,PoP技术将继续与先进封装技术如2.5D/3D TSV、扇出型封装(Fan-Out)等深度融合,推动封装向“更小、更快、更智能”方向发展。随着5G-Advanced、6G通信及AI芯片需求的爆发,PoP在高频高速信号完整性、低功耗设计及异构集成方面的创新将成为关键突破点,进一步模糊封装与组装的边界,重构半导体产业链的价值分配模式,为终端用户提供更丰富的器件组合选择与更优的成本效益方案。

光电路组装技术

光电路组装技术作为应对信息化时代数据传输瓶颈的关键突破口,正通过光电子技术与传统电子电路的深度融合,重构高频高速信号传输的底层架构。

该技术以光纤为核心光路载体,将光信号传输容量提升至传统铜线的数万倍,有效解决了高速信号串音、电磁辐射及布线带宽限制等核心问题。

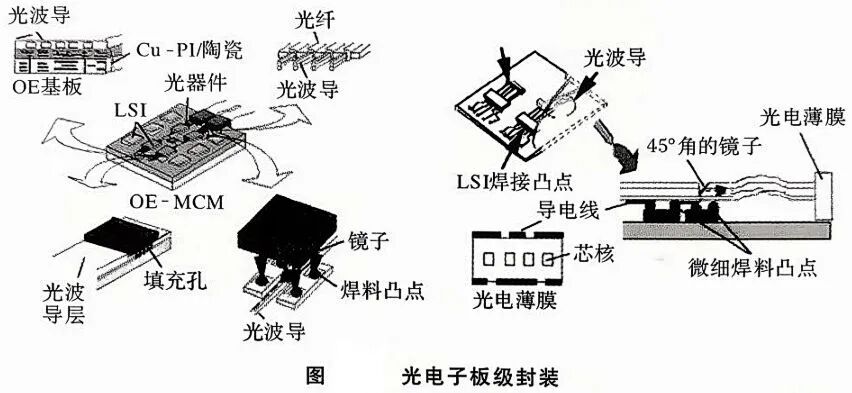

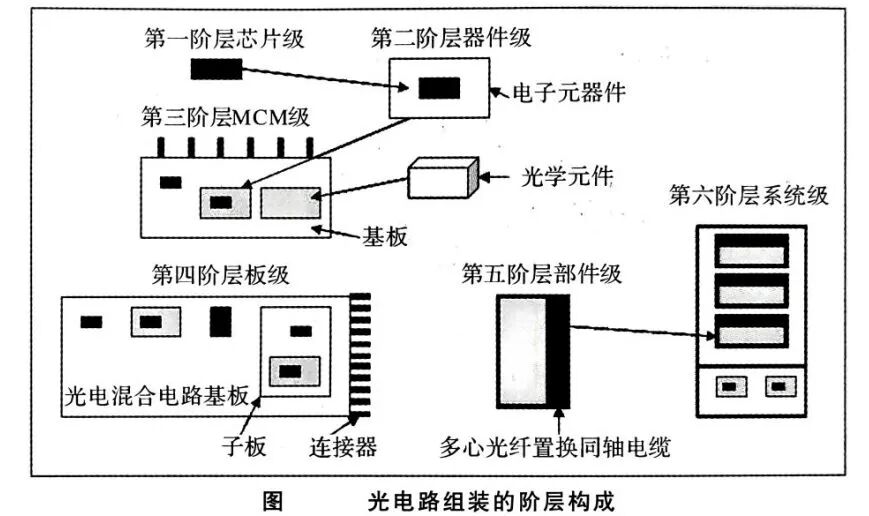

从技术体系架构看,光电路组装涵盖芯片级至系统级的全链路集成。

芯片级聚焦LSI内部连接危机,通过引入激光与光二极管实现1mm级光布线,突破金属布线RC延迟瓶颈;器件级则推动光学与电子元器件的同基板混合集成,如日本与欧美重点研发的PLC基板混合光集成技术,通过无透镜空间光耦合实现光路与光纤的直接对接,布线长度扩展至厘米级;MCM级采用氧化聚酰亚氨光路积层一体化技术,在铜PCB基板上构建光电混合型多芯片模块,光布线长度达10~20cm,实现半导体激光、光二极管与LSI的高密度互连。

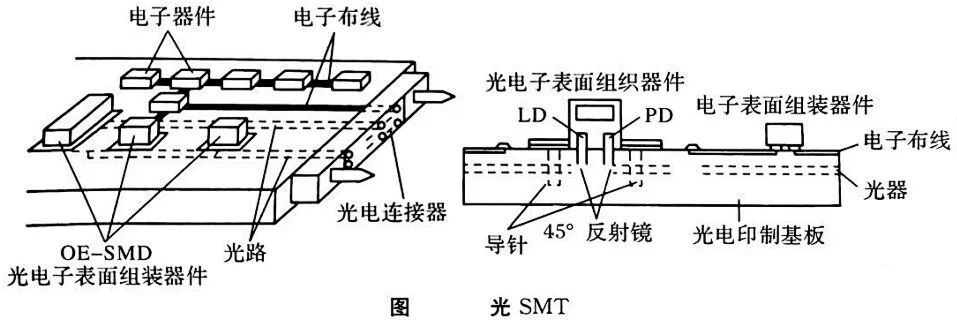

板级层面,光表面组装技术(光SMT)成为核心,通过将传送电信号的铜导体与光路集成于同一基板,形成光电混合电路基板,支持光器件/模块的埋置化与高密度布线,当前正突破聚合物光纤布线与黏结剂涂布工艺等关键技术;部件级针对系统级布线瓶颈,采用多芯光纤替代传统电缆,实现轻量、小径、高速、高密度布线,布线长度扩展至米级;系统级则聚焦光源创新,欧美主推全波长面发光激光,日本商用化端面激光技术,形成差异化技术路径。

当前行业最新进展显示,光电路组装技术正朝着更高集成度、更低功耗与更优热管理方向突破。例如,采用硅基光子集成技术(PIC)与CMOS工艺的异构集成,可将光模块尺寸压缩至传统方案的1/3,功耗降低40%;通过引入低损耗氮化硅光波导与铟镓砷光电探测器,实现200Gbps以上单通道传输速率。在应用层面,光SMT已广泛应用于数据中心高速互连、自动驾驶激光雷达模块及AI加速卡的光电混合封装,如英伟达最新H100 AI芯片采用光电混合封装技术,实现PCIe 5.0接口与光模块的直接集成,带宽密度提升3倍;此外,在消费电子领域,光电路组装正推动手机、平板等终端的光学指纹识别、3D传感模块向更薄、更节能方向演进。

展望未来,光电路组装技术将与2.5D/3D TSV、扇出型封装等先进封装技术深度融合,推动“光-电-热”协同设计成为主流。随着6G通信、量子计算及边缘AI的爆发,光电路组装在高频高速信号完整性、低功耗设计及异构集成方面的创新将成为关键突破点,进一步模糊光电封装的边界,重构半导体产业链的价值分配模式,为终端用户提供更优的性能密度与成本效益方案,持续赋能社会信息化与数字化的高速发展。

-

半导体

+关注

关注

336文章

29999浏览量

258444 -

电路板

+关注

关注

140文章

5255浏览量

106499 -

封装技术

+关注

关注

12文章

595浏览量

69155

原文标题:PoP叠层封装与光电路组装技术

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

元器件PIP(堆叠封装)和PoP(堆叠组装)的比较

叠层电感-叠层陶瓷电感-贴片叠层电感-片式叠层电感

元器件PIP和PoP的优缺点

嵌入式存储封装技术SiP/SOC/MCP/PoP的区别是什么

多个叠层芯片封装技术趋势

叠层电感的优点和应用

元器件PIP(堆叠封装)和PoP(堆叠组装)的比较

0.4mm层叠封装(PoP)封装的PCB组装指南,第二部分

PoP叠层封装与光电路组装技术解析

PoP叠层封装与光电路组装技术解析

评论