本篇博文主要讲解在 PL 中如何使用 AXI Interrupt Controller (INTC) 的级联模式,将 IP 核超过 32 个的中断连接到 PS 上。

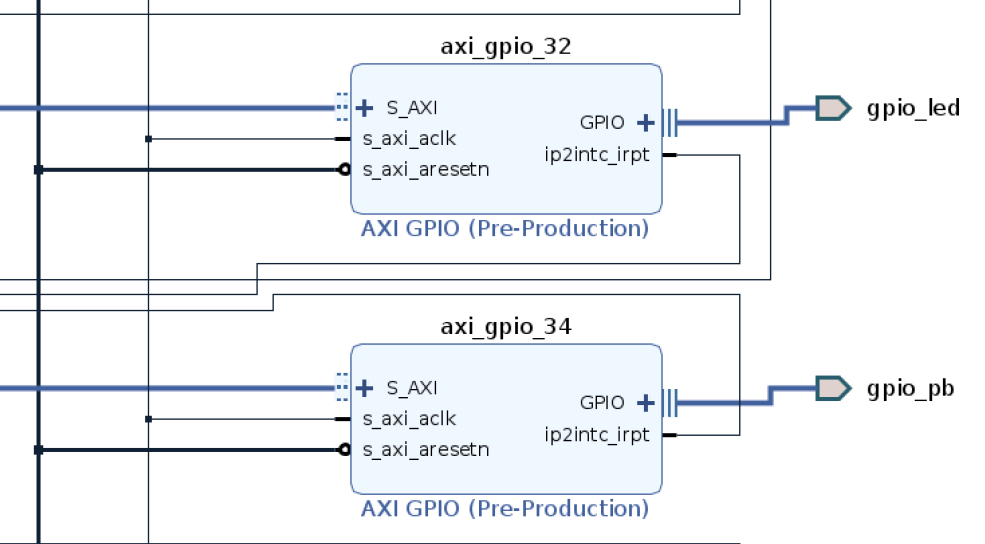

在 AMD Vivado Design Suite 设计中使用了 AMD AXI GPIO 中断。

设计示例是以 VCK190 评估板为目标创建,使用的是 Vivado 2020.2 版本。中断功能在 PetaLinux 2020.2 上经过了测试。

AXI GPIO:

General Purpose Input/Output (GPIO) 核提供输入输出访问的接口,用于对接器件的交互。该核还可用于控制外部器件的行为。

中断:

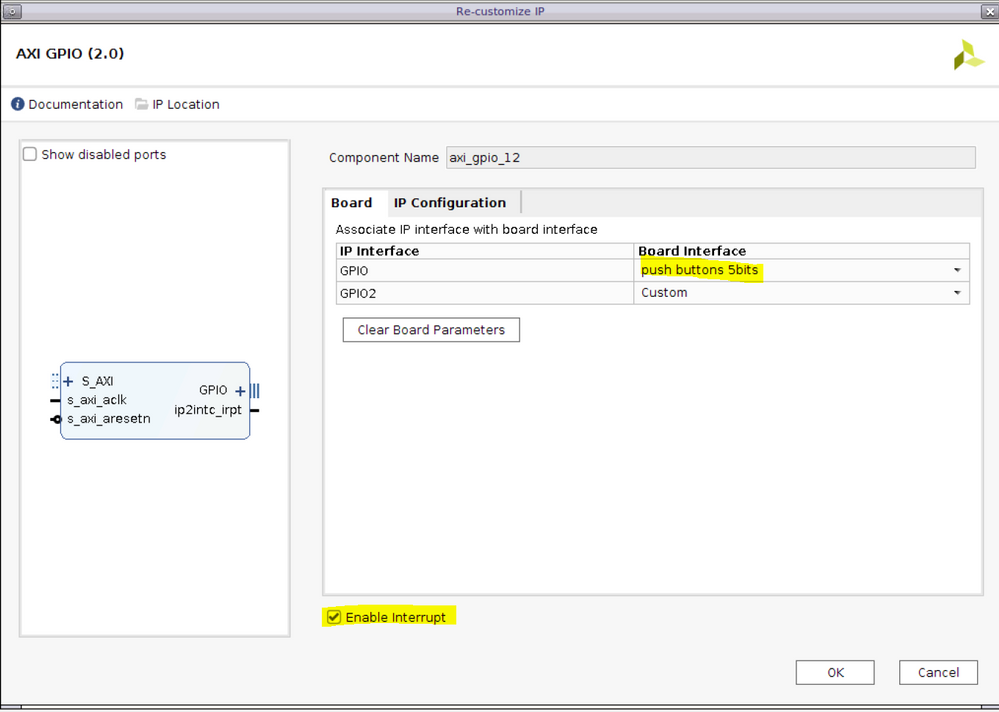

在 AXI GPIO 中必须先为对应的 GPIO 通道启用中断,这样即可从该通道读取中断状态。使用 AXI GPIO 自定义中的“Enable Interrupt”选项来启用中断。

对于输入模式,gpio_input 管脚连接到 VCK190 的如下按钮 (PUSH BUTTON):

gpio_input(0) = GPIO_SW15

gpio_input(1) = GPIO_SW16

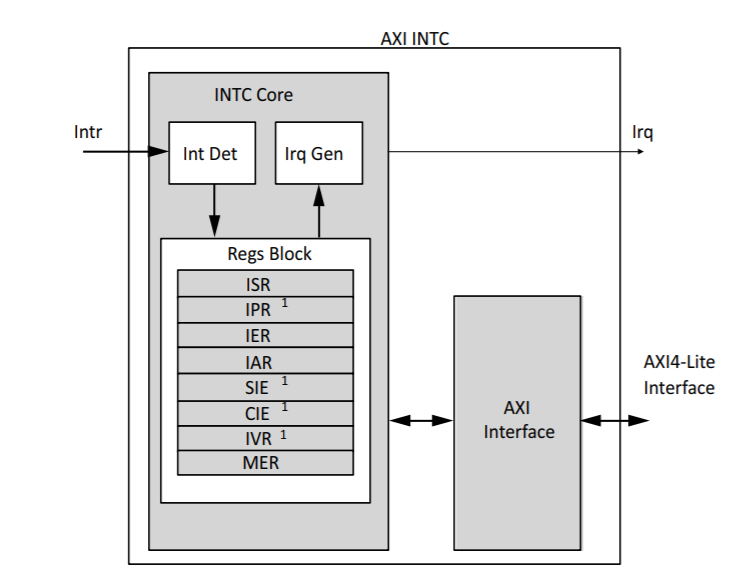

AXI INTC:

AXI Interrupt Controller (INTC) 核可将来自外设器件的多个中断输入集中到系统处理器的单一中断输入上。寄存器用于检查、启用和确认中断。

此示例的主要目的是将超过 16 个中断连接到 PS。AXI INTC 核可满足此需求。使用单一 AXI INTC 块的情况下最多可连接 32 个中断,并且还可使用级联。

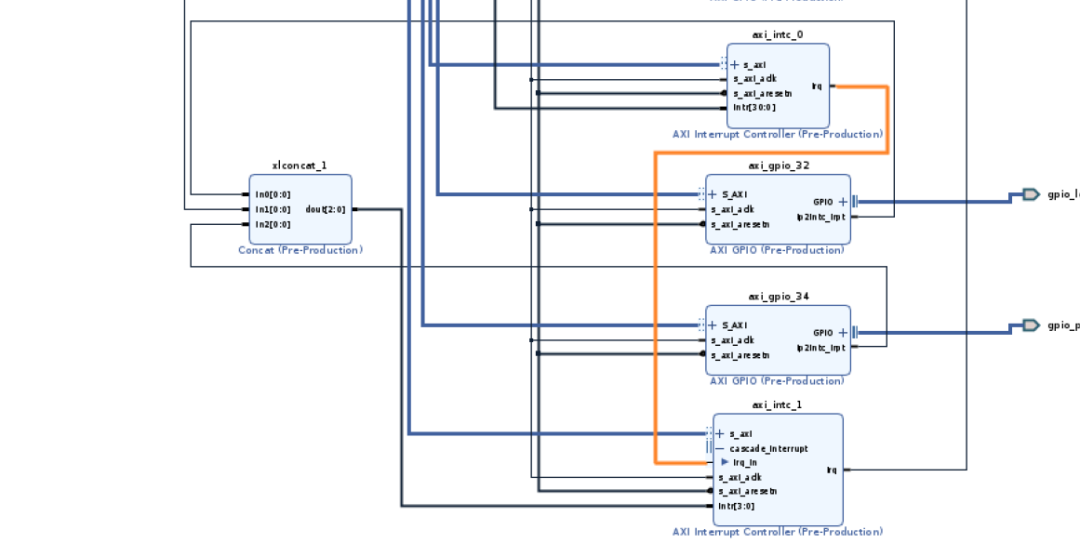

在级联模式下,有不少于两个 AXI INTC 实例连接到同一个处理器。参数 C_EN_CASCADE_MODE 表示的“Enable Cascade Interrupt Mode”和参数 C_CASCADE_MASTER 表示的“Cascade Mode Master”都需要在此模式下配置。

注释:必须使用主 AXI INTC 实例的 irq_in 端口或第 31 个中断位,来实现从次级 AXI INTC 实例的级联。

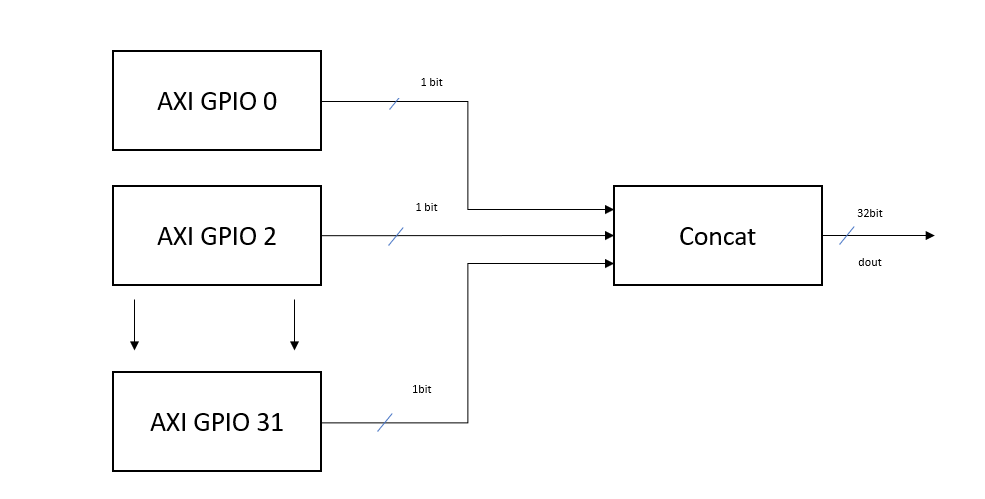

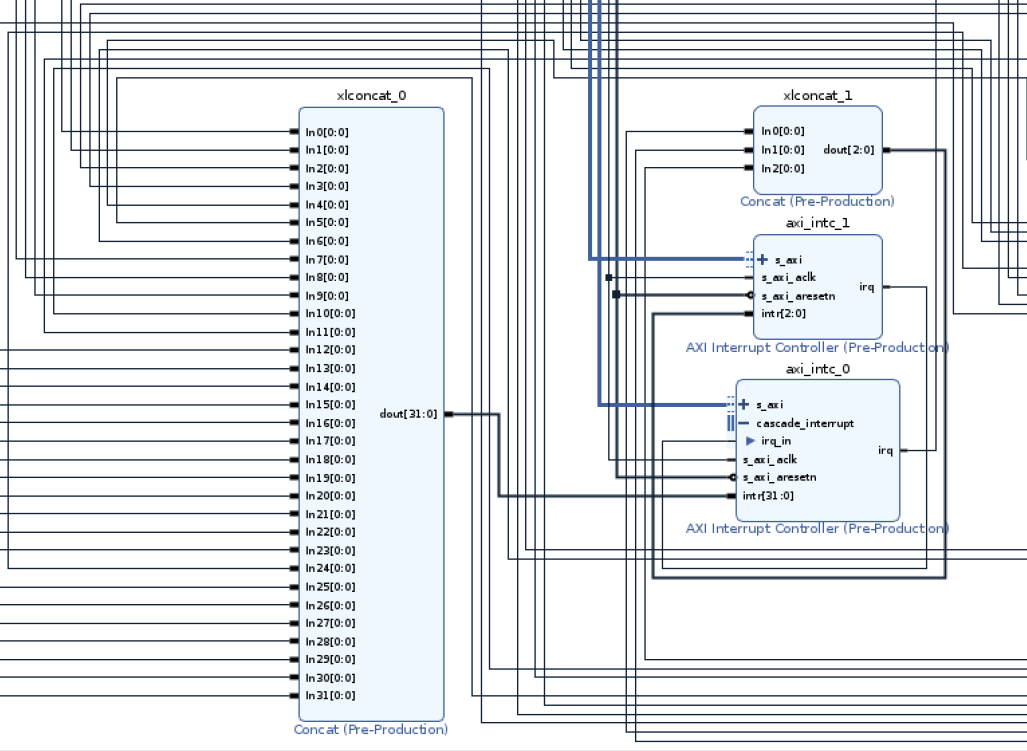

在下文描述 Concat IP 的多个图例中,可以看到中断的连接方式。

块设计:

下文解释了设计中使用的 IP 及其连接。

Concat IP:

Concat IP 核可提供相应机制来将不同宽度的总线信号组合到单一总线内。

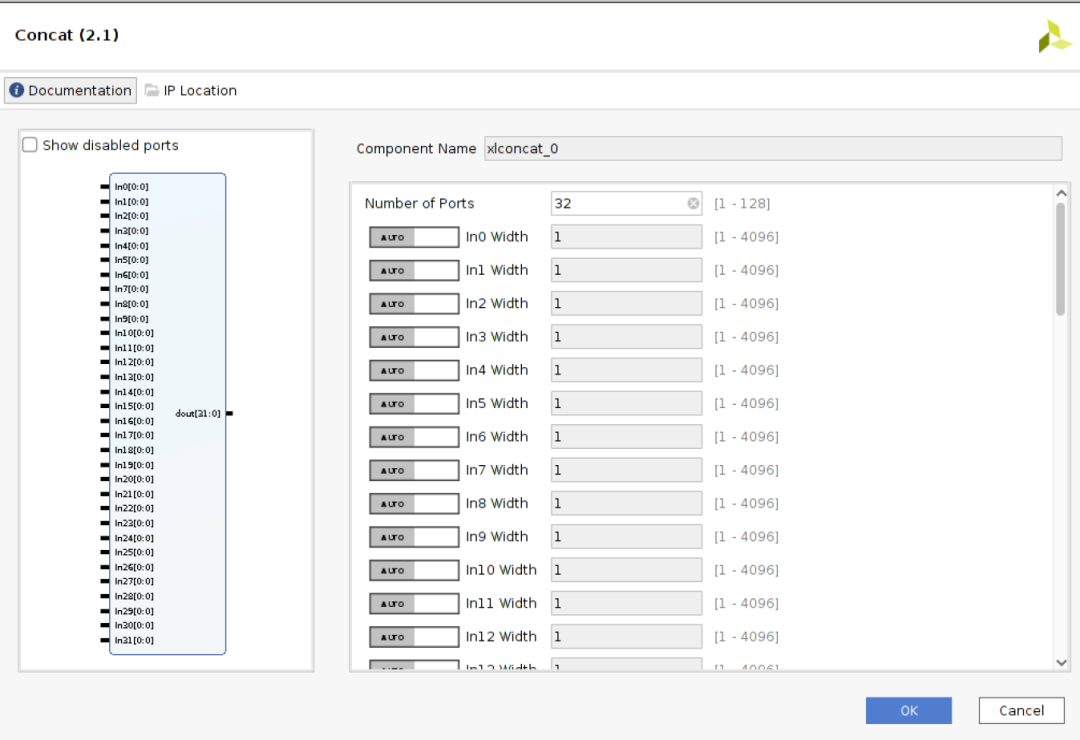

从 IP catalog 添加 Concat 块,然后双击 IP(如下所示)以打开“Re-customize IP” 对话框。

在上图中,将“Number of Ports”参数设置为期望的输入端口数。在此示例中,所选端口数量为 32。

完成 IP 自定义后的结果如下:

如前所述,输出端口 AXI_INTC_0 连接到下一个 AXI_INTC_1 的 irq_in 中断输入端口。

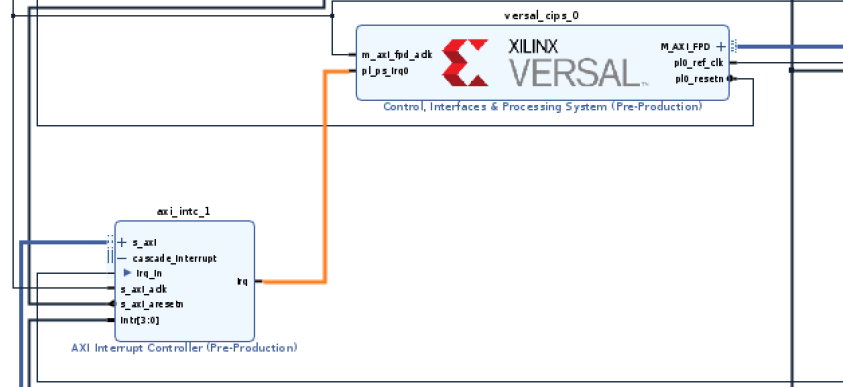

AXI_INTC_1 的输出连接到 AMD Versal 自适应 SoC CIPS 块的 pl_ps_irq0 端口:

请验证设计并遵循其余步骤进行操作以生成比特流。

导出硬件,用于构建 PetaLinux 镜像。

PetaLinux:

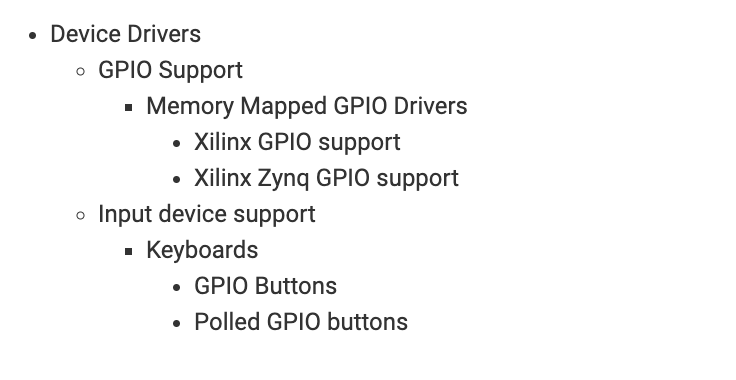

内核配置:

在 Menuconfig 中启用以下选项。默认情况下,这些选项均已启用,但您应核实其状态,以防万一。

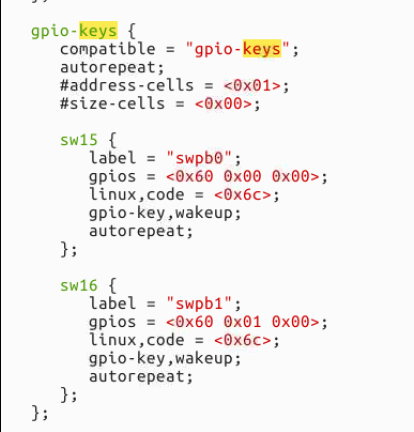

向设备树添加按钮:

按钮仅可用于 Input GPIO 应用程序。

创建的每个子节点均可控制 GPIO 中对应的单个位。在 dts 文件中的“gpio-keys”键节点下,根据设计,为按钮 (Push Buttons) 创建含如下名称的子节点:

完成此操作后,请启动 Linux。

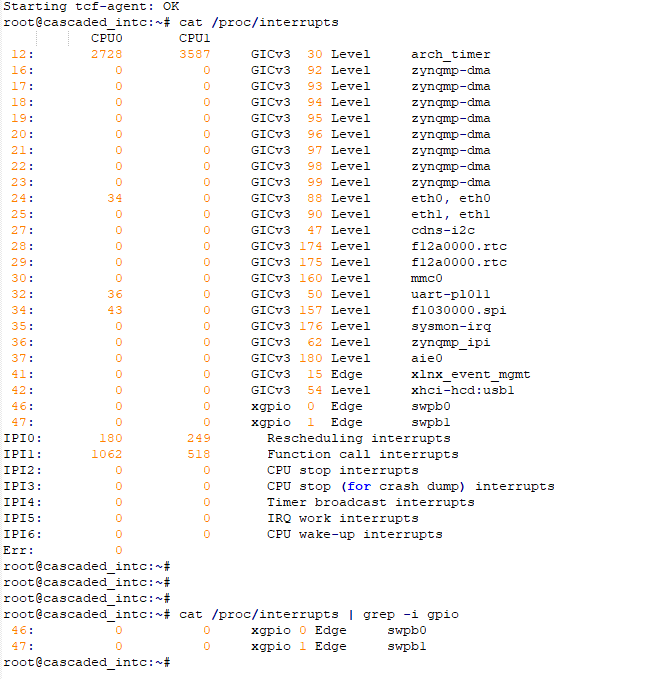

您可在 cat /proc/interrupts 中看到按钮 SW15 和 SW16 的标签。

-

amd

+关注

关注

25文章

5708浏览量

140452 -

soc

+关注

关注

40文章

4635浏览量

230281 -

中断

+关注

关注

5文章

920浏览量

43886 -

评估板

+关注

关注

1文章

1041浏览量

31346 -

Versal

+关注

关注

1文章

176浏览量

8546

原文标题:开发者分享|AMD Versal™ 自适应 SoC 上的级联模式示例

文章出处:【微信号:gh_2d1c7e2d540e,微信公众号:XILINX开发者社区】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

在AMD Versal自适应SoC上使用QEMU+协同仿真示例

使用Aurora 6466b协议实现AMD UltraScale+ FPGA与AMD Versal自适应SoC的对接

【ALINX 技术分享】AMD Versal AI Edge 自适应计算加速平台之 Versal 介绍(2)

AMD Versal自适应SoC中eMMC烧录/启动调试检查表(上)

AMD Versal自适应SoC内置自校准的工作原理

Versal™ 自适应 SoC 助力 8K 处理 – 为 8K 做好准备(3)

AMD率先推出符合DisplayPort™ 2.1 8K视频标准的FPGA和自适应SoC

AMD发布第二代Versal自适应SoC,AI嵌入式领域再提速

AMD Versal™ Adaptive SoC CPM PCIE PIO EP设计CED示例

AMD Versal自适应SoC CPM5 QDMA的Tandem PCIe启动流程介绍

AMD Versal自适应SoC器件Advanced Flow概览(上)

AMD Versal自适应SoC器件Advanced Flow概览(下)

AMD Versal自适应SoC上的级联模式示例

AMD Versal自适应SoC上的级联模式示例

评论