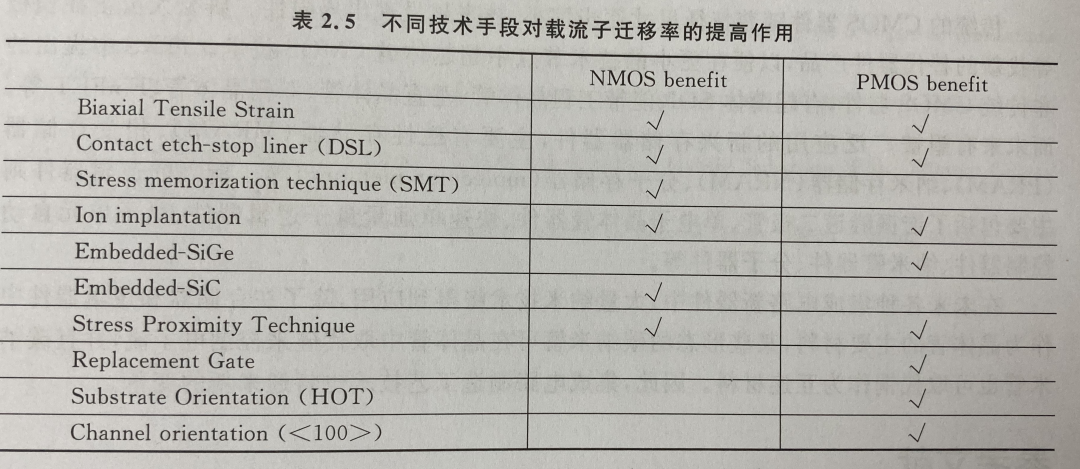

在高k金属栅之外,另一种等效扩充的方法是增加通过器件沟道的电子或空穴的迁移率。表2.5列举了一些提高器件载流子迁移率的手段及其对 PMOS或者 NMOS的作用。

应力技术是提高MOS 晶体管速度的有效途径,它可改善NMOS晶体管电子迁移率和PMOS晶体管空穴迁移率,并可降低MOS 晶体管源/漏的,应变硅可通过如下3种方法获得:①局部应力工艺,通过晶体管周围薄膜和结构之间形成应力;②在器件沟道下方嵌入SiGe层;③对整个晶圆进行处理。

局部应力工艺已经被广泛应用来提升CMOS 器件性能。源漏区嵌入式锗硅技术产生的压应力已经被证明可以有效提高 PMOS 器件的驱动电流。另外,源漏区嵌入式碳硅技术产生的拉应力可以提高 NMOS 器件的驱动电流。应力记忆技术在 NMOS 器件性能提升中得到使用。金属前通孔双极应力刻蚀阻挡层技术也是有效的局部应力工艺,拉应力可以提高 NMOS 的器件性能,而压应力可以提高PMOS的器件性能。

对于 PMOS,众所周知,具有(110)晶面取向的衬底比具有(100)晶面取向的衬底的空穴迁移率性能更高。而对于 NMOS,具有(110)晶面取向的衬底比具有(100)晶面取向的衬底的电子迁移率要差。晶向重排可以通过改变 PMOS 晶体管排版设计(layout)或者是在标准<100>晶体表面进行通道方向重新排列完成。

混合取向技术(Hybrid Orientation Technology, HOT)将PMOS 做在(110)晶面衬底,NMOS 做在(100)晶面衬底上,从而在改进PMOS 空穴迁移率的同时,不损害NMOS 的电子迁移率。IBM 公司在2003年IEDM上提出利用晶圆键合和选择性外延技术,得到(110)晶面上的PMOS 和(100)晶面上的NMOS,报告显示将其应用于 90nm CMOS, PMOS 性能可以提高40%。

硅直接键合(Direct Silicon Bonding,DSB) 晶片(一种键合(100)和(110)衬底的大块CMOS 混合型晶片)是公认的推进这一方法的候选方案。IBM 曾将(100)层的面旋转45°并将(110)衬底的DSB 层变薄来获得标准的(100)晶片,成功地将环形振荡器的延迟比传统的DSB 衬底0°(100)晶片—它键合到一个具有两个硅衬底,即(100)和(110)衬底的晶片上——的结果改进了10%,并将这一成果与技术集成到一起。新发展将环形振荡器延迟比标准(100)晶片改进了30%。这一成果可以与能达到更高进展的技术集成到一起。

-

NMOS

+关注

关注

3文章

404浏览量

36957 -

晶体管

+关注

关注

78文章

10443浏览量

148696 -

PMOS

+关注

关注

4文章

274浏览量

31733

原文标题:载流子迁移率提高技术

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

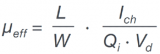

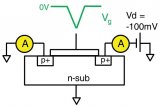

如何精准提取MOSFET沟道迁移率

新型超快速单脉冲技术解决传统迁移率测量挑战

载流子平衡的低压高效有机白光器件

载流子迁移率测量方法总结

载流子输运现象之散射率、迁移率、电阻率、砷化镓

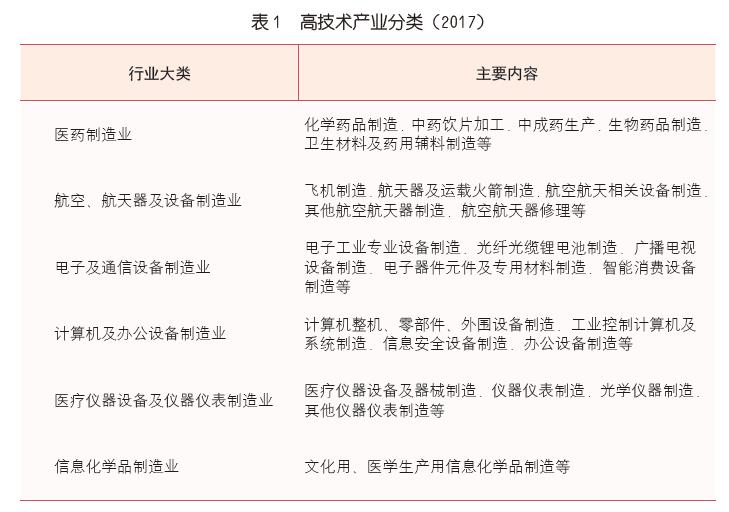

高技术制造业快速增长 高技术制造业包括哪些行业

8.2.10.3 4H-SiC反型层迁移率的实验结果∈《碳化硅技术基本原理——生长、表征、器件和应用》

8.2.10.1 影响反型层迁移率的机理∈《碳化硅技术基本原理——生长、表征、器件和应用》

8.2.10.2 反型层迁移率的器件相关定义∈《碳化硅技术基本原理——生长、表征、器件和应用》

如何通过霍尔效应测量半导体中电子和空穴的迁移率?

高电子迁移率晶体管介绍

载流子迁移率提高技术详解

载流子迁移率提高技术详解

评论