概述

MAX9240A紧凑型解串器可用于通过50Ω同轴电缆或100Ω屏蔽双绞线(STP)电缆与GMSL串行器进行接口。该器件与MAX9271或MAX9273串行器配对使用。

并行输出可编程为单输出或双输出。双输出在每个像素时钟周期选通输出一半的并行字。双输出可与具有双输入功能的GMSL串行器一起使用。

该器件具有一个运行速度为9.6kbps至1Mbps的嵌入式控制通道。通过使用控制通道,微控制器(µC)可以不受视频时序影响,随时对串行器/解串器和外设寄存器进行编程。提供两个可编程GPIO端口和一个连续采样的GPI输入。

为了与更长的电缆一起使用,该器件配有可编程均衡器。并行输出端可提供可编程扩频。串行输入符合ISO 10605和IEC 61000-4-2 ESD标准。内核电源范围为1.7V至1.9V,I/O电源范围为1.7V至3.6V。该器件采用48引脚(7mm x 7mm) TQFN-EP封装,引脚间距为0.5mm,工作温度范围为-40°C至+105°C。

数据表:*附件:MAX9240A用于同轴电缆或STP电缆的6.25MHz至100MHz、25位GMSL解串器技术手册.pdf

应用

- 汽车摄像头系统

特性

- 非常适合摄像头应用

- 与低成本50Ω同轴电缆和FAKRA连接器或100Ω STP配合使用

- 错误检测/纠正

- I^2^C 到 I^2^C 模式下支持9.6kbps至1Mbps控制通道,具有时钟延展功能

- 出色的电源电流:90mA(最大值)

- 百万像素摄像头的双倍速率时钟

- 电缆均衡功能支持15m电缆全速运行

- 48引脚(7mm x 7mm) TQFN-EP封装,引脚间距为0.5mm

- 百万像素摄像头的高速数据反序列化

- 单输出或双输出的串行比特率高达1.5Gbps:6.25MHz至100MHz时钟

- 多种控制通道模式实现系统灵活性

- UART到UART或UART到I^2^C 模式下支持9.6kbps至1Mbps控制通道

- 降低EMI和屏蔽要求

- 并行输出上的可编程扩频有助于降低EMI

- 在串行输入端跟踪扩频

- 提供用于摄像头上电和验证的外设功能

- 内置用于串行链路BER测试的PRBS检查器

- 串行链路短接在一起、短接到地、短接到电池或开路故障检测

- 两个GPIO端口

- 用于摄像头帧同步触发和其他用途的专用"上/下"GPI

- 远程/在本地从睡眠模式唤醒

- 满足严格的汽车和工业要求

- 工作温度范围为-40°C至+105°C

- ±10kV接触放电和±15kV空气放电IEC 61000-4-2 ESD保护

- ±10kV接触放电和±30kV空气放电ISO 10605 ESD保护

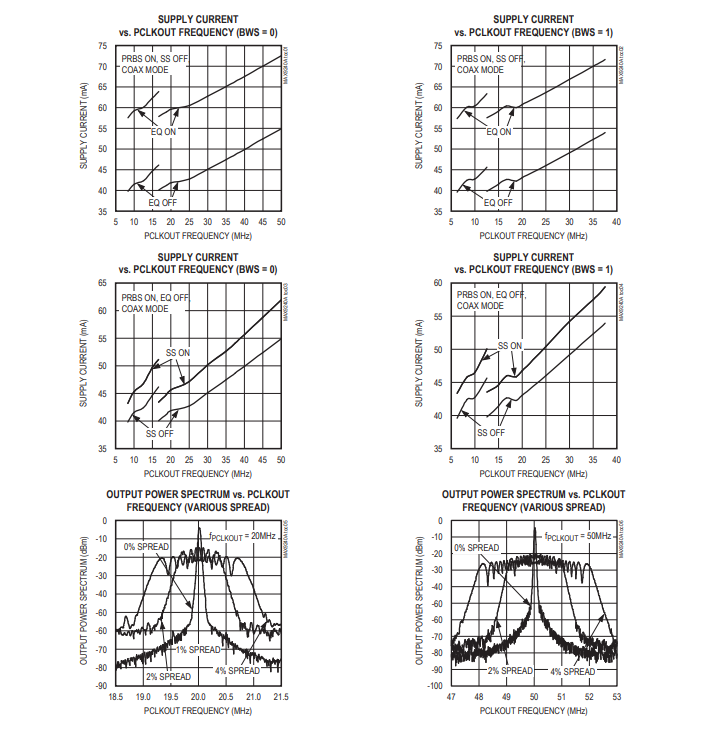

典型操作特性

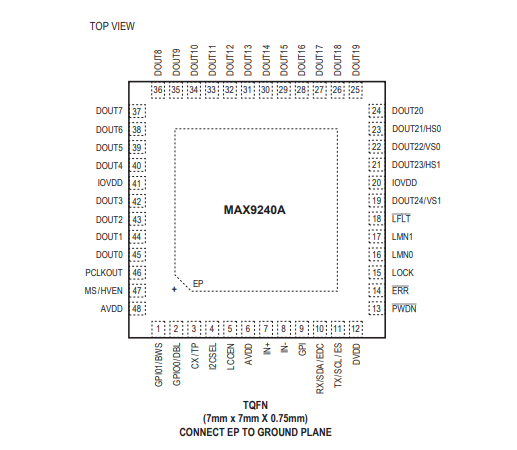

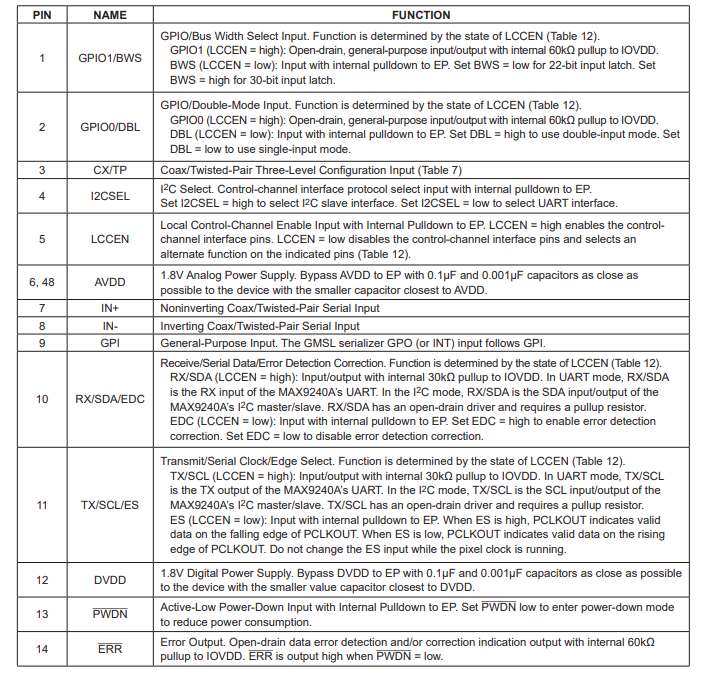

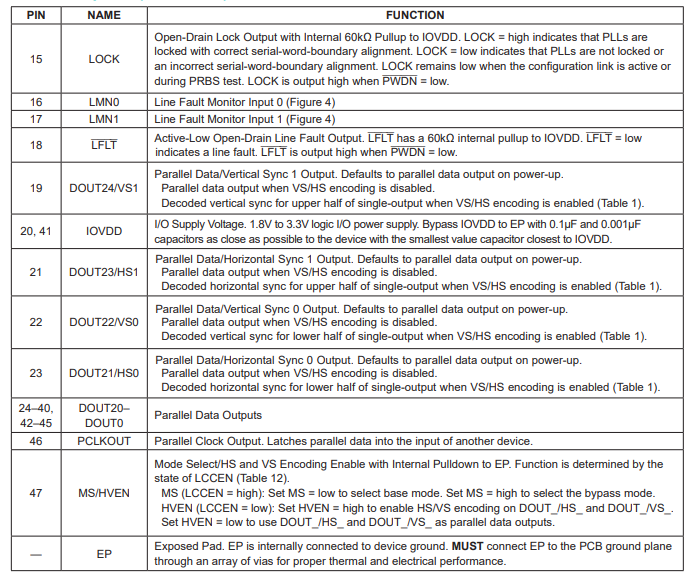

引脚配置描述

详细说明

MAX9240A解序列化器与MAX9271或MAX9273序列化器配对时,可提供完整的工作特性集,与任何GMSL序列化器配对时,除基本功能外也具备相应特性。

该解序列化器的最大串行比特率为1.5Gbps,适用于15米或更长的电缆,在25比特单输出模式下,输出时钟最高可达100MHz;在15比特双输出模式下,最高可达75MHz。这种比特率和输出灵活性支持多种显示器,从QVGA(320 x 240)到WVGA(800 x 480)及更高分辨率,颜色深度为18比特,也支持兆像素图像传感器。输入均衡功能与GMSL序列化器的预加重功能相结合,可延长电缆长度并增强链路可靠性。

控制通道使微控制器能够对序列化器和解序列化器的寄存器进行编程,也可用于配置外设。控制通道还用于配置和访问GPIO。微控制器可以位于链路的任一端,或在使用两个微控制器时位于两端。有两种控制通道操作模式可用。基本模式使用I²C或GMSL UART协议,而旁路模式使用自定义UART协议。UART协议支持全双工通信,而I²C支持半双工通信。

扩频时钟可用于降低并行输出上的电磁干扰(EMI)。串行输入符合ISO 10605和IEC 61000-4-2 ESD保护标准。

寄存器映射

寄存器用于设置解序列化器的工作条件,并在基本模式下通过控制通道进行编程。解序列化器有自己的设备地址,与之配对的序列化器也有其设备地址。类似地,序列化器有自己的设备地址,解序列化器也有自己的设备地址。无论何时更改设备地址,都需将新地址同时写入两个设备。默认情况下,解序列化器的设备地址由任何GMSL串行器的CXTP输入和默认设备地址设置为0x80(见表7)。寄存器0x00和0x01保存设备地址。

位图

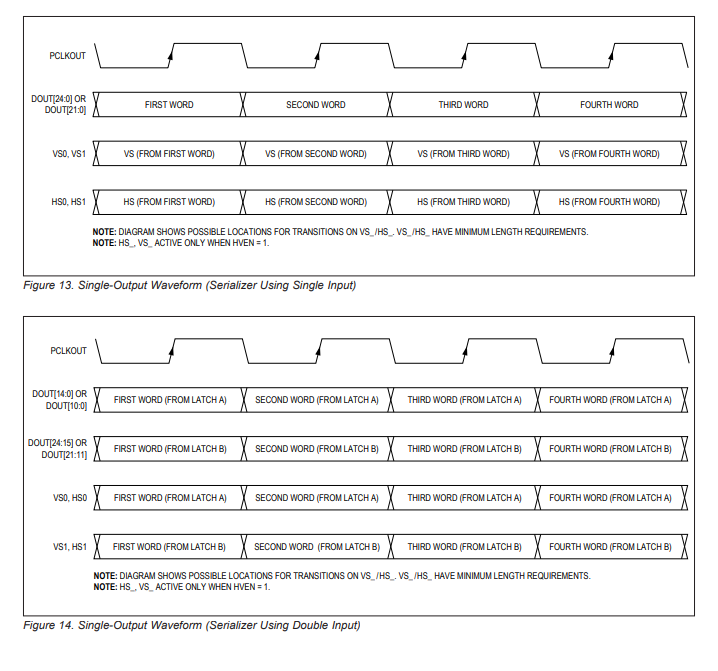

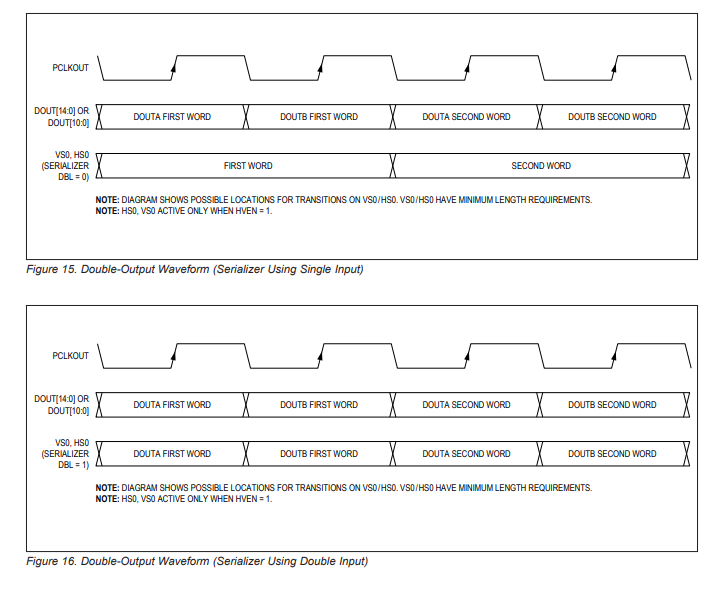

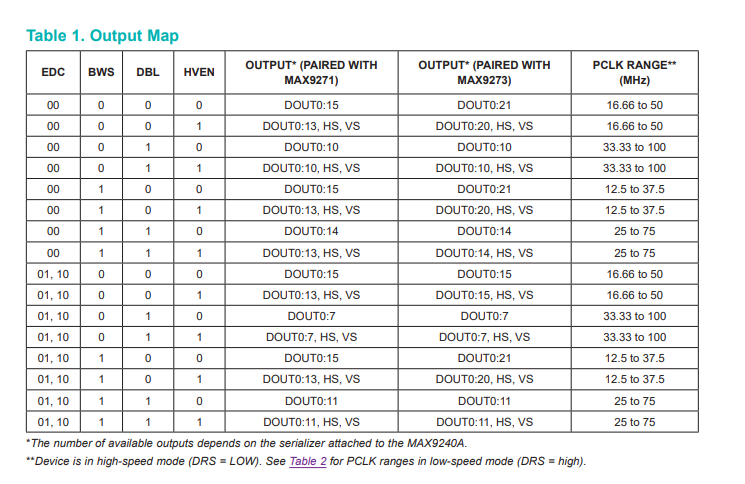

并行输出功能和宽度取决于双/单输出模式(DBL)、HS/VS编码(HVEN)、使用的纠错方式(EDC)和总线宽度(BWS)引脚的设置。表1列出了控制引脚的映射。未使用的输出引脚为低电平。

在双输出模式下,并行输出分为两个半宽度字,输出速率为串行字速率的两倍(见图15和图16)。解序列化器设备将像素时钟速率从33.3MHz提升至100MHz,用于15比特双输出模式;从25MHz提升至75MHz,用于11比特双输出模式。

在单输出模式下,设备在每个PCLKOUT周期对并行数据进行一次时钟采样。解序列化器设备将像素时钟速率从6.25MHz提升至50MHz(见图13和图14)。

-

解串器

+关注

关注

1文章

152浏览量

14635 -

GMSL

+关注

关注

2文章

68浏览量

16780 -

STP

+关注

关注

0文章

58浏览量

10691

发布评论请先 登录

MAX9240A: 6.25MHz to 100MHz, 25-Bit GMSL Deserializer for Coax or STP Cable with Line Fault Detect Data Sheet MAX9240A: 6.25MHz to 100MHz, 2

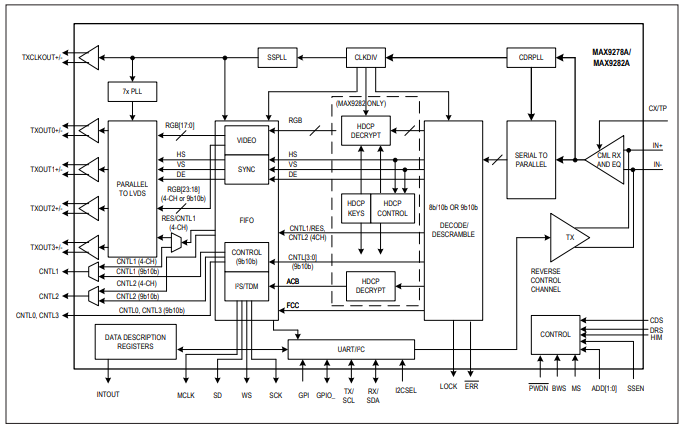

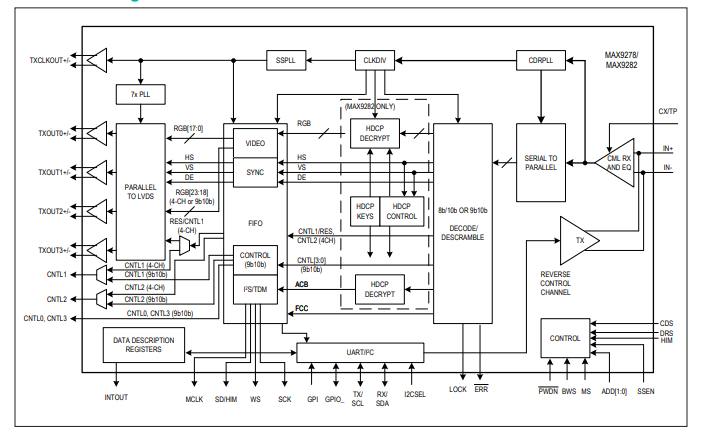

MAX9278A/MAX9282A 3.12Gbps GMSL解串器,用于同轴电缆或STP输入和LVDS输出技术手册

MAX9291/MAX9293 3.12Gbps GMSL串行器,用于同轴或STP输出及HDMI输入技术手册

MAX9277/MAX9281用于同轴电缆或STP输出驱动和LVDS输入的3.12Gbps GMSL串行器技术手册

MAX9275/MAX9279用于同轴电缆或STP输出驱动和并行输入的3.12Gbps GMSL串行器技术手册

MAX9240A用于同轴电缆或STP电缆的6.25MHz至100MHz、25位GMSL解串器技术手册

MAX9240A用于同轴电缆或STP电缆的6.25MHz至100MHz、25位GMSL解串器技术手册

评论