来源:至芯

大家好,欢迎来到至芯科技FPGA炼狱营地,准备开启我们的伟大征程!正所谓“兵马未动,粮草先行”,战前的准备自是必不可少,在FPGA的漫漫沙场,我们何以入场,何以取胜呢?在这里我们为各位战友准备了vivado 2018.3的使用教程。

1.1 新建工程

首先点击图标打开Vivado2018.3软件,如图所示:

打开之后,如图所示,点击“CreateProject”新建一个工程。

打开新工程向导首页,直接点击“Next”,如图所示:

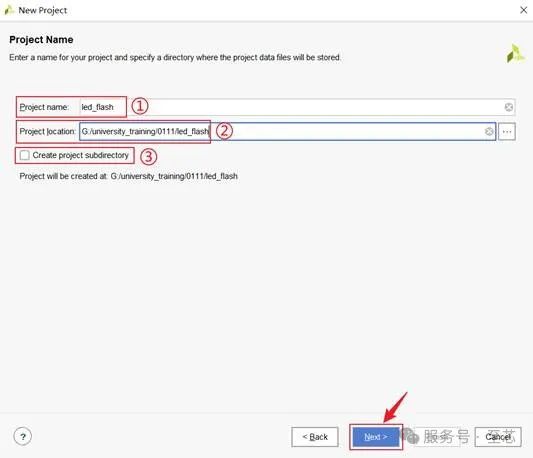

如图所示:其中①框是设置工程的名字,这里取名为led_flash;②框是设置新建工程的存储路径,这里保存在新建的led_flash文件夹下;③框是选择是否在②框的工程文件夹下新建一个子文件夹用于存放工程。这里不勾选。

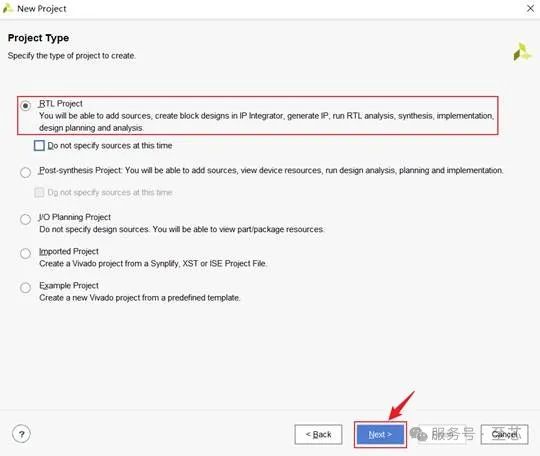

如图所示,选择“RTLProject”即可,直接点击“Next”。

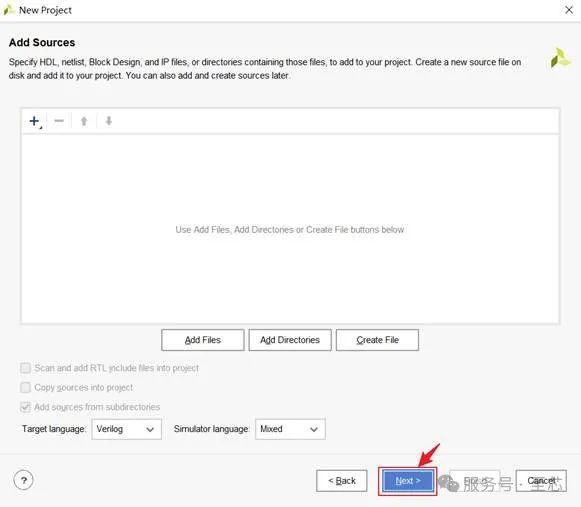

如图所示,在该页面中可以点击“AddFiles”来选择添加已经写好的源文件,如果有多个文件可以一次性全部添加进工程,这里没有写好的源文件,所以就不添加。该页面直接按默认设置,点击“Next”:

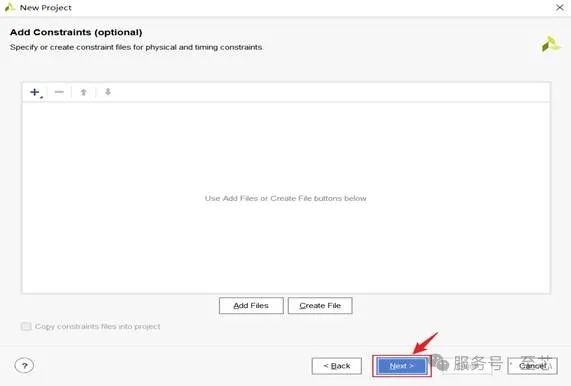

如图所示,在该页面可以点击“AddFiles”来选择添加已经写好的约束文件,同样的这里选择不添加。该页面直接按默认设置,点击“Next”:

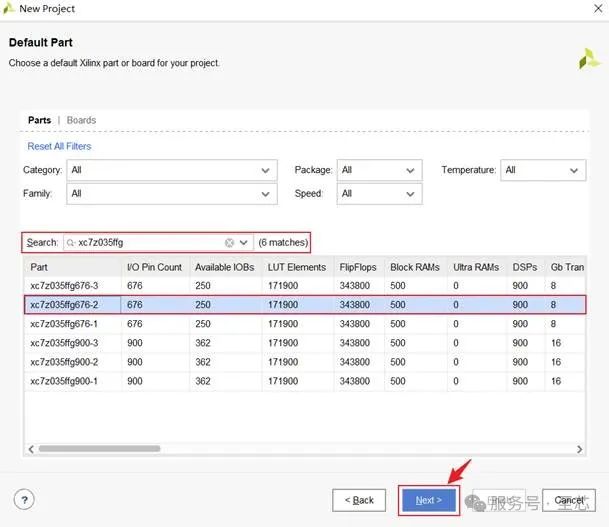

如图所示,该界面是选择FPGA芯片的型号,此开发板的型号:XC7Z035FFG676-2,选中第2个点击“Next”:

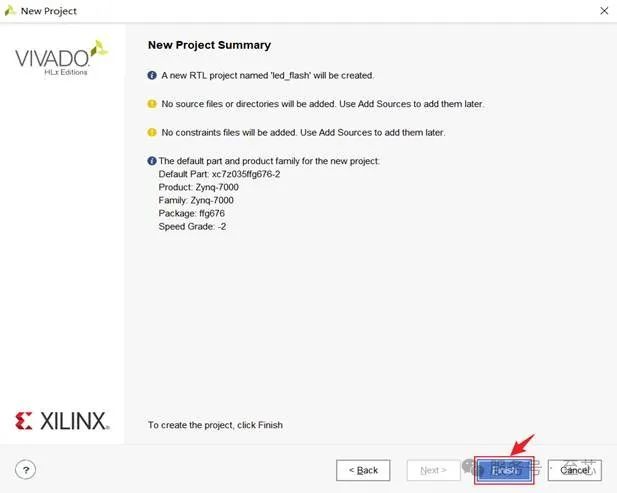

如图所示,最后生成整个新工程向导的一个总结,可以验证下是否和自己最初的选择有无差异,如果没有问题点击“Finish”。

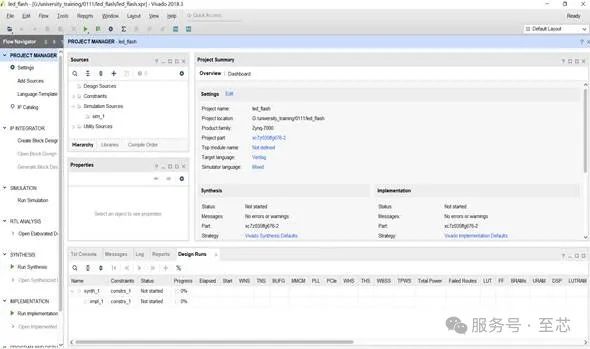

新建工程完毕后,进入Vivado工程设计界面,如图所示。

打开led_flash文件夹发现里面生成了一些文件夹和文件,led.xpr就是这个工程的工程文件,如图所示:

1.2 RTL代码编写

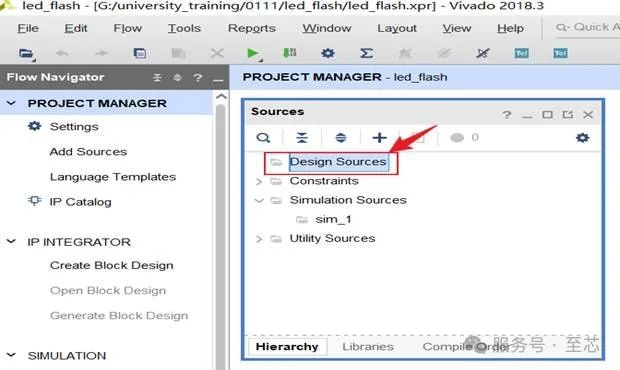

如图所示,新建一个.v文件,用于编写代码。找到“DesignSources”右击,弹出如图所示界面。

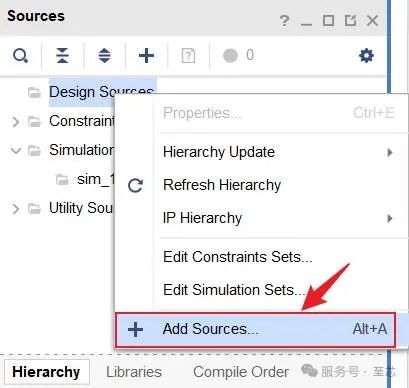

点击“Add Sources…”。

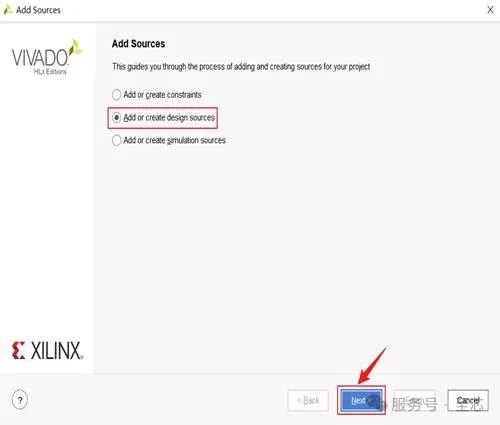

如图所示,选择“Addor create design sources”。点击“Next”。

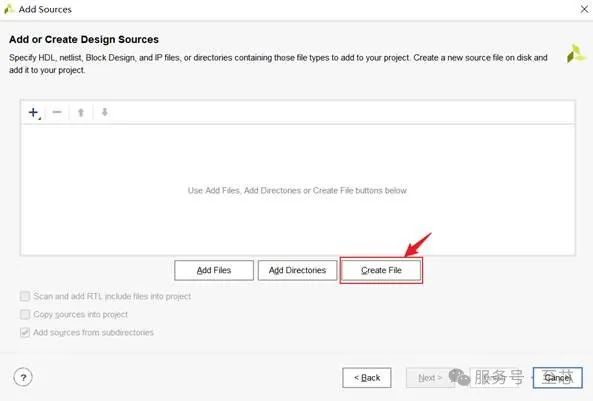

如图所示,选择“CreateFile”。

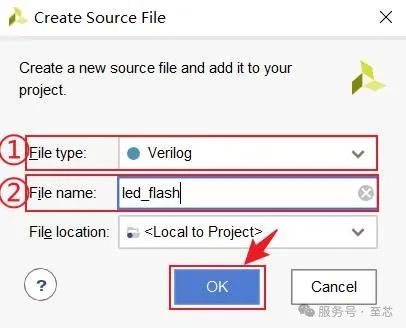

如图所示,①框中选择语言,②框中输入文件的名字。点击“OK”。

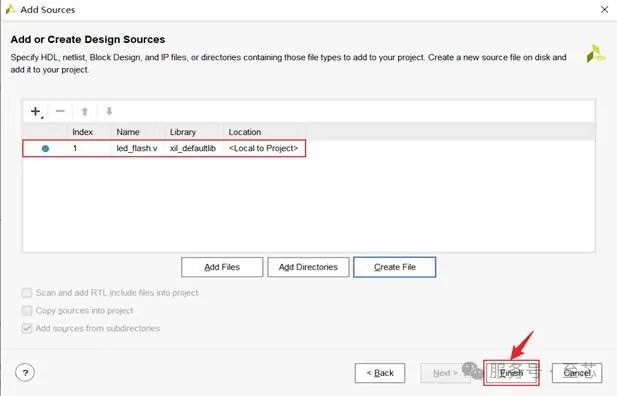

如图所示,点击“Finish”。

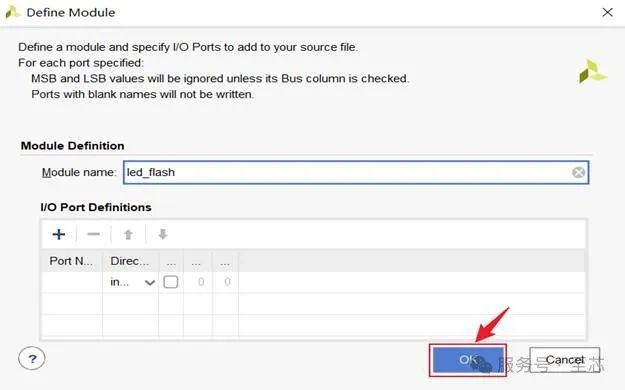

如图所示,点击“OK”。

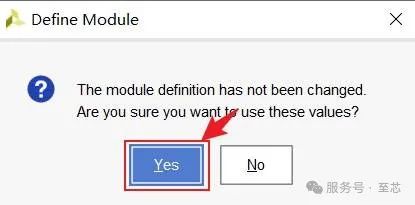

如图所示,点击“Yes”。

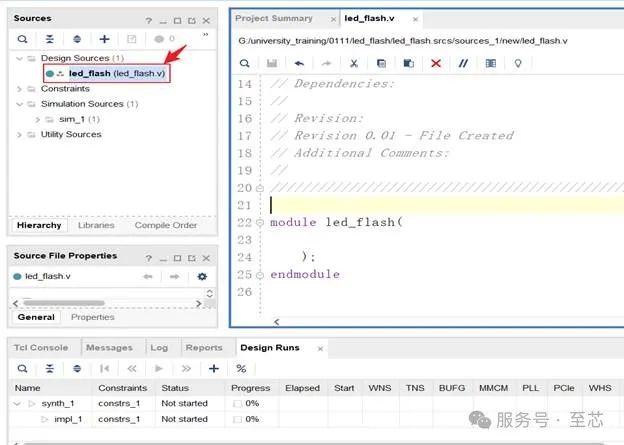

如图所示,新的文件已经添加进来。

1.3 Testbench代码的编写

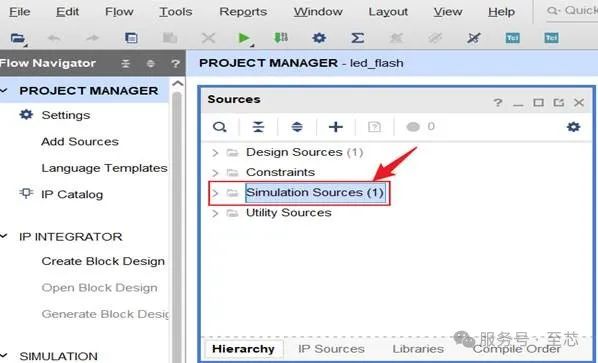

如图所示,找到“SimulationSources”,右击,弹出如下图所示界面。

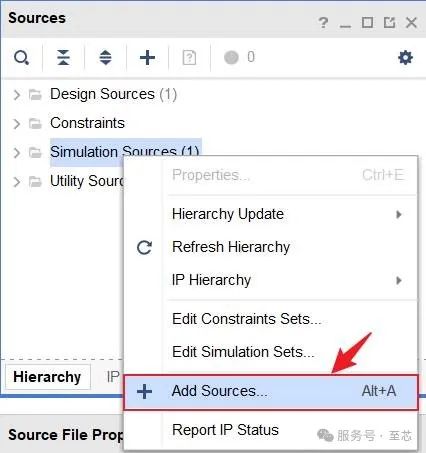

如下图所示,点击“AddSources…”。

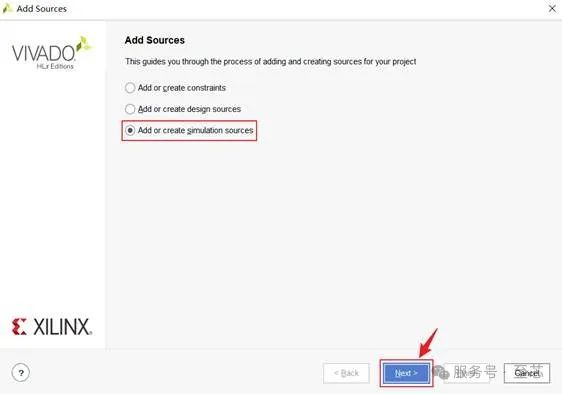

如下图所示,点击“Addor create simulation sources”。点击“Next”。

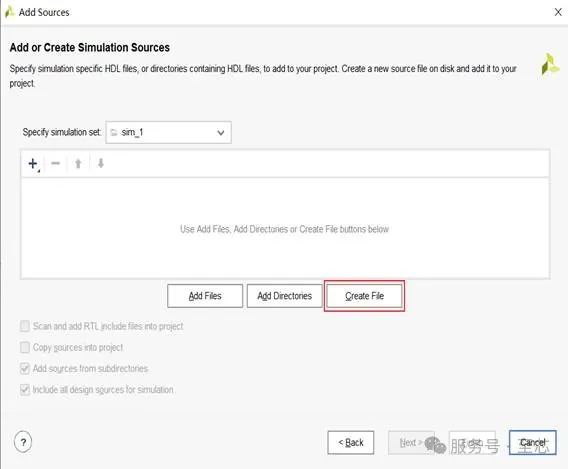

如下图所示,选择“CreateFile”。

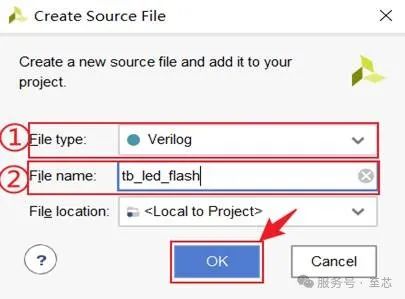

如图所示,①框选择文件的类型,②框输入仿真文件的名字。点击“OK”。

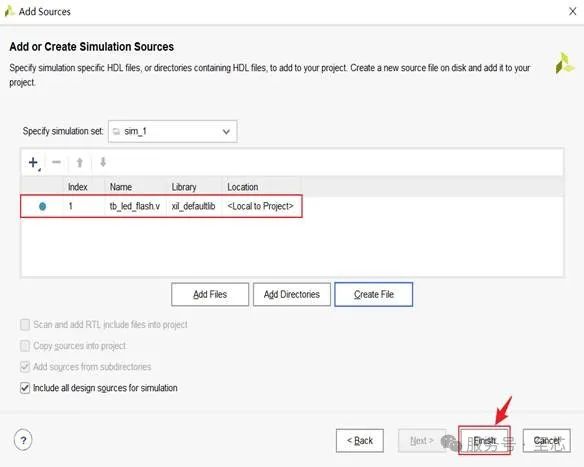

如图所示,点击“Finish”。

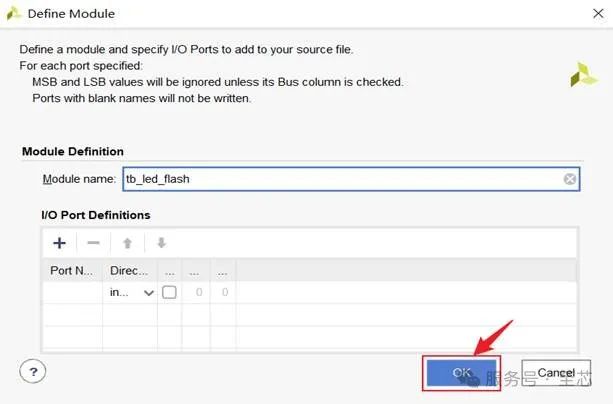

如图所示,点击“OK”。

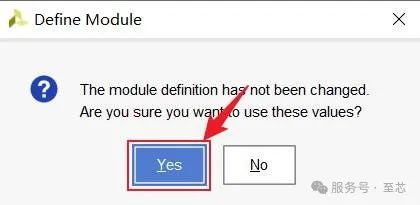

选择“Yes”。

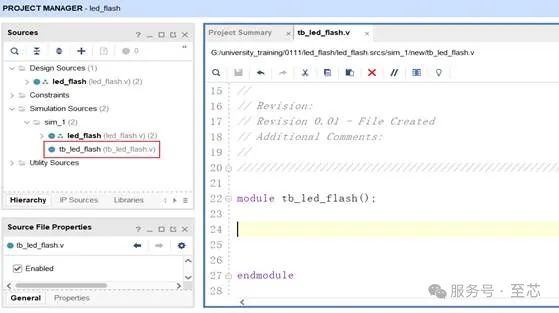

如图所示,仿真文件已经加入工程。

1.4 打开SIMULATION观察波形

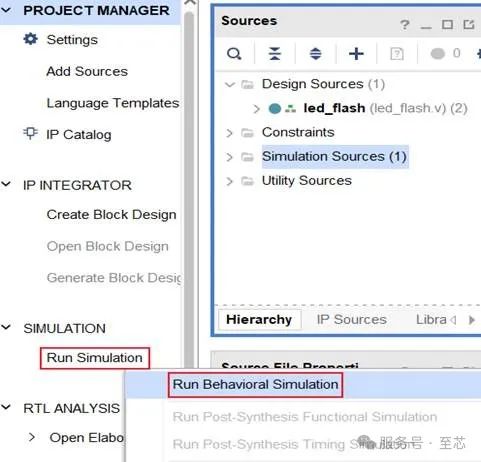

如图所示,在Vivado界面中,左键单击SIMULATION下的Run Simulation后会出现Run Behavioral Simulation选项,单击该选项进入仿真页面。

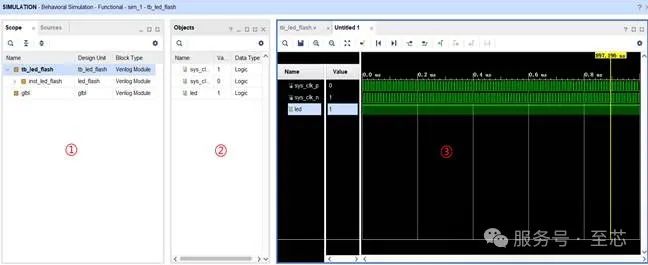

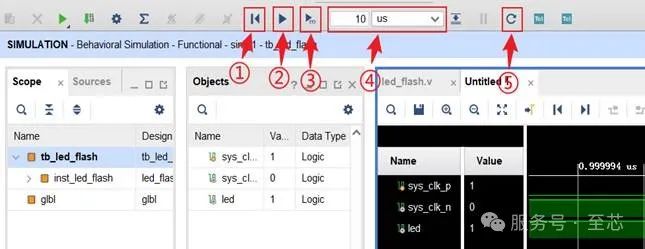

如图所示,其中①窗口可以看到设计的模块划分,可以选择相应模块,右键点击Add Wave Window将模块下的全部信号添加到波形界面进行查看;②框中显示的是选中模块下的信号,同样也可以选中相应的信添加到仿真界面进行查看;③框为波形显示界面,在该界面可以看到添加信号的波形,初始默认添加的信号为测试文件模块的端口信号。

下面为大家介绍一些查看仿真波形图比较常用的一些操作,如图所示:

其中箭头①所指的图标是波形复位,点击后会直接对界面的波形进行全部清空。

箭头②所指的图标是运行仿真,点击该图标后会一直运行仿真,除非遇到HDL语句中的中断仿真语句,如“$stop”或者手动点击如图所示箭头所指的图标,仿真才会停止。使用该功能时需要注意,如果点击了该图标,一定要记得点击停止仿真,否则仿真机会一直运行下去,这会耗费电脑大量的内存资源。

箭头③所指的图标是让仿真运行特定的一端时间,该段时间可以在④框中进行任意设置,比如这里设置的时间是1000ns,那么点击③图标时,仿真就会运行1000ns。如果我们再点击一次,仿真就会在原有的基础上再往下运行1000ns。

箭头⑤所指的图标是进行重新编译仿真,当对源代码进行了修改后,就可以通过点击该图标来进行重新仿真。

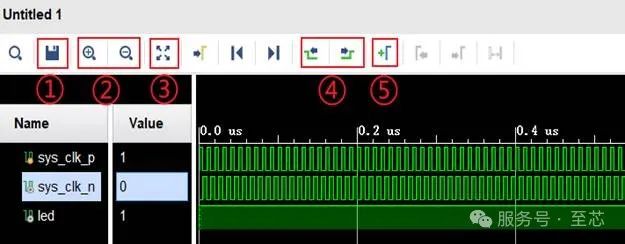

如图所示,①框图标是对波形进行保存,也可以使用快捷键“Ctrl+S”进行保存;②框中图标是对波形进行放大以及缩小;点击③图标是显示全部仿真时间的波形图;④框图标让参考线(图中黄色的线即是参考线)定位的选中信号的上升沿或者下降沿;点击⑤框中图标可添加参考线。

1.5 管脚约束

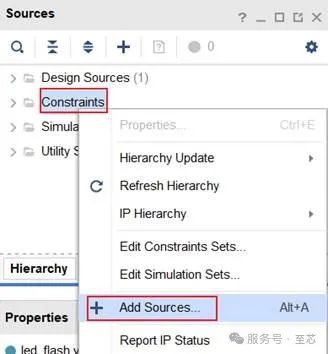

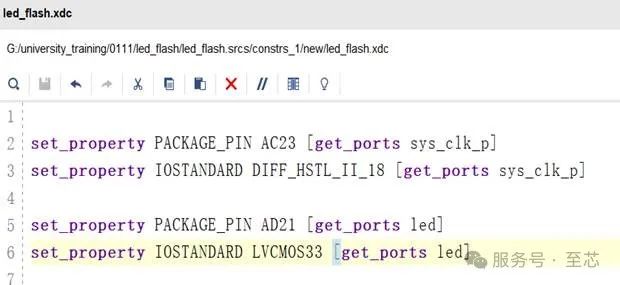

仿真结束即验证了代码设计的正确性,也就是说可以上板验证了,但是在上板之前还需要进行管脚约束,根据原理图确定时钟和led分别与FPGA芯片的哪个管脚对应。

如图所示,找到“Constraints”à“Add Sources…”

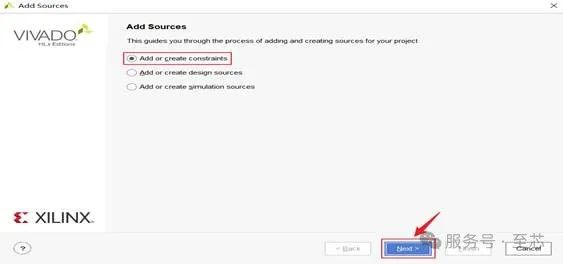

如图所示,选择“Addor create constraints”,点击“Next”。

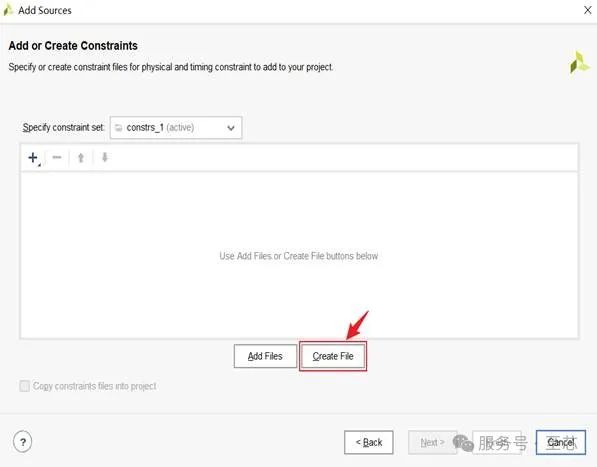

如图所示,选择“CreateFile”。

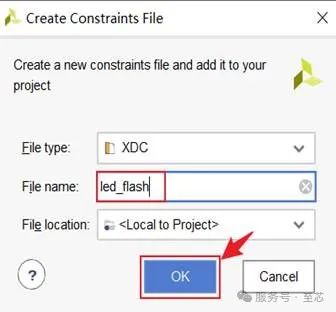

如图所示,给约束文件起个名字,然后点击“OK”。

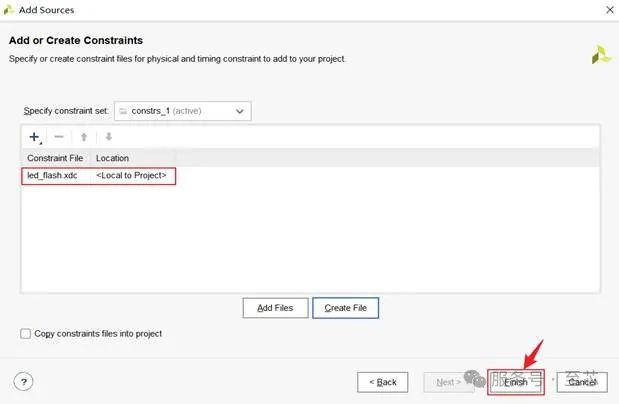

如图所示,点击“Finish”。

如图所示,编写约束文件。

1.6 逻辑分析仪的使用

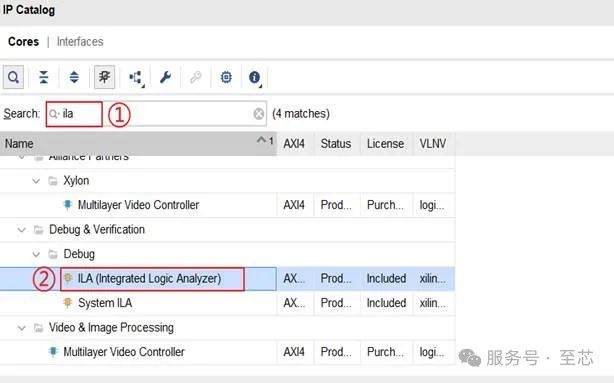

鼠标左键点击“IPCatalog”,进入IP核搜索界面。

如图所示,在①框处输入ila;双击②框处的“ILA(Integrated Logic Analyzer)”,进入ila的配置界面。

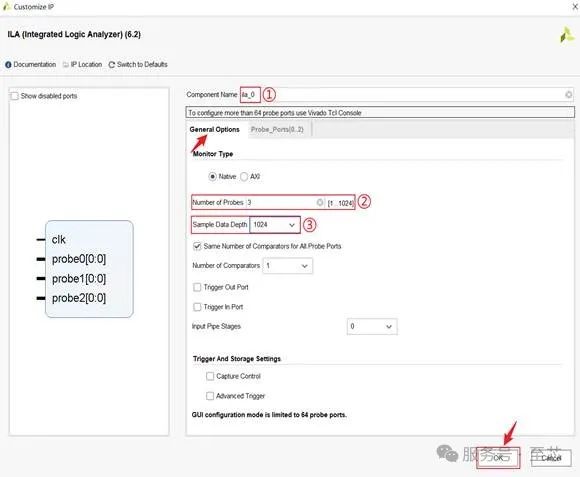

如图所示,进入ila的配置界面,在“GeneralOptions”界面,①框是IP核的名字,保持默认即可。②框是探针的数量,根据所抓取的信号来选择,如果想要抓3个信号,那么探针的数量就是3;如果想抓5个信号,那么探针的数量就是5。③框是采样深度,采样深度可以选择的有1024、2048、4096、8192…131072等。

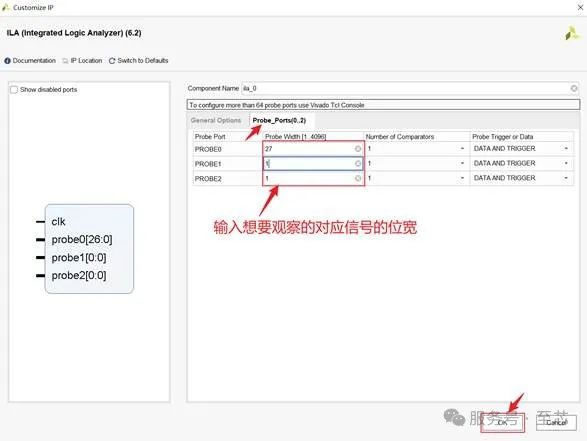

如图所示,在“ProbePorts”界面,输入对应信号的位宽。然后点击“OK”。

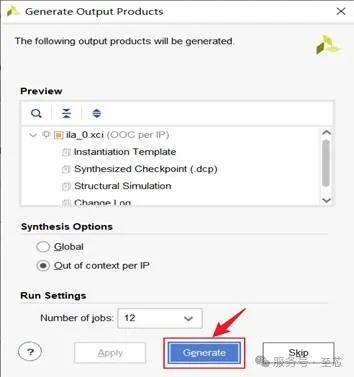

如图所示,点击“Generate”。

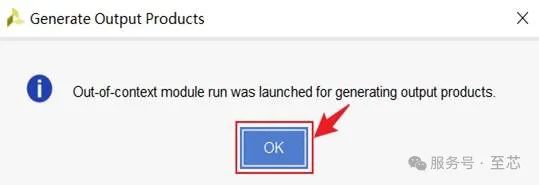

如图所示,点击“OK”。

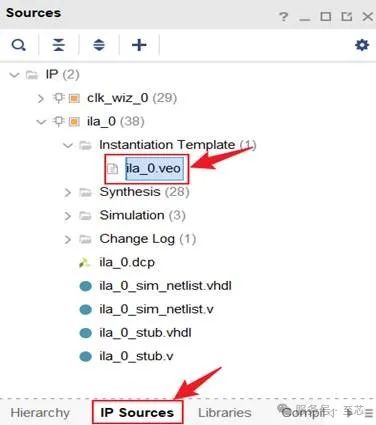

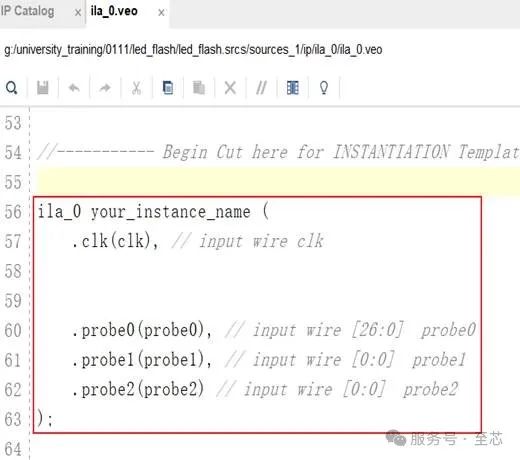

如图所示,在“IPSources”栏中,找到ila的例化模版,双击进去,把例化文件复制到想要观察的信号对应的模块中。

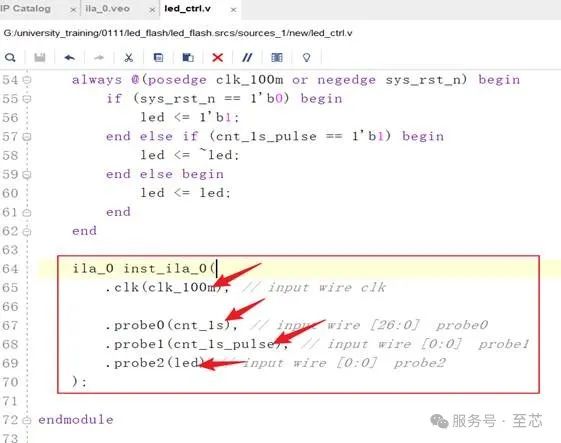

如图所示,复制例化文件。

如图所示,将想要观察的信号接到探针上,逻辑分析仪时钟的选择非常重要,信号用哪个时钟驱动的,逻辑分析仪就使用哪个时钟。

自此,逻辑分析仪加入完毕,重新编译,生成bit文件。

下板文件生成之后,连接板卡的电源与烧写线。

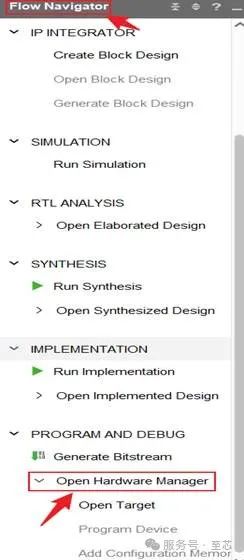

鼠标左键点击“OpenHardware Manager”。

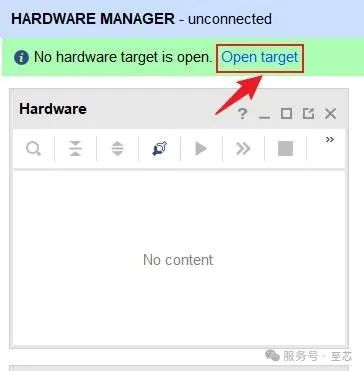

鼠标左键点击“Opentarget”。

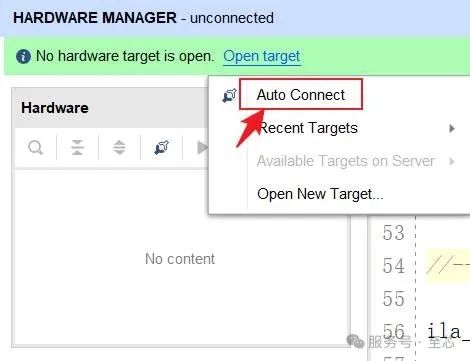

如图所示,点击“AutoConnect”。

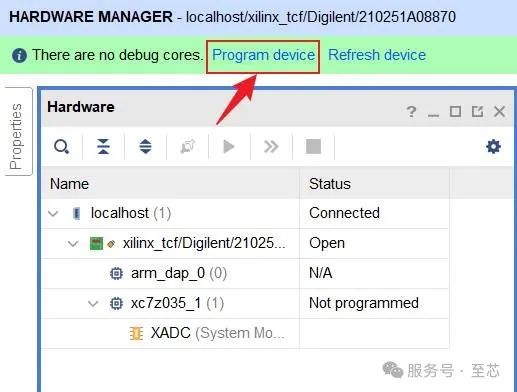

如图所示,鼠标左键点击“Programdevice”。

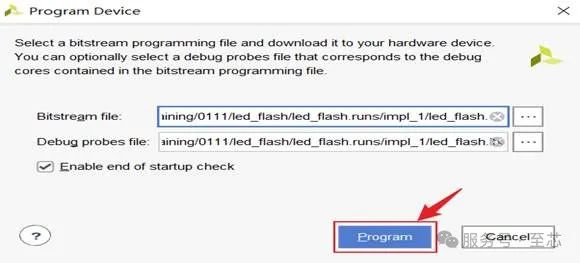

如图所示,点击“Program”就可以烧写程序。

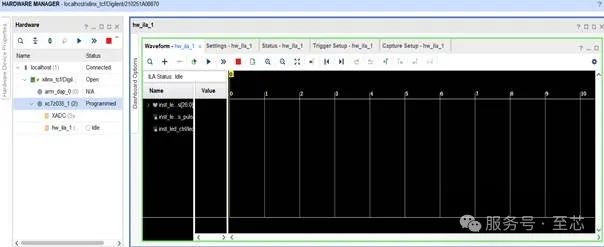

如图所示,烧写程序之后,弹出如图所示界面。

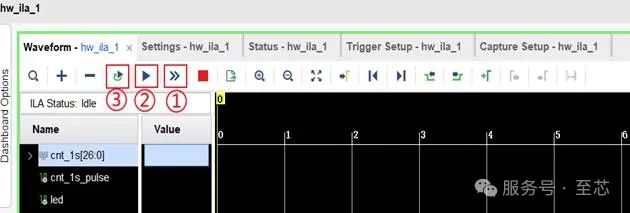

如图所示,①框是立即触发,不需要任何触发条件;②框是条件触发,满足设置的条件才会触发;③框是循环触发,满足设置的条件,会一直触发。

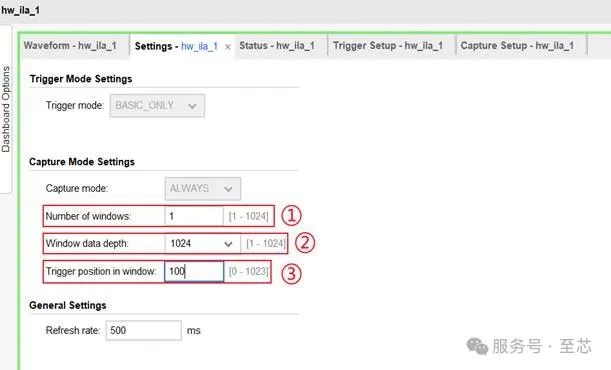

如图所示,①框是设置触发的窗口个数。②框是设置采样深度。③框是设置触发的位置。

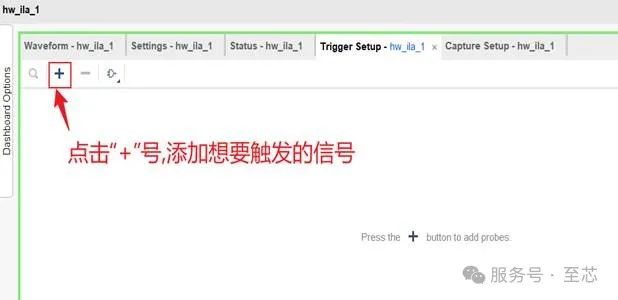

如图所示,添加想要触发的信号。

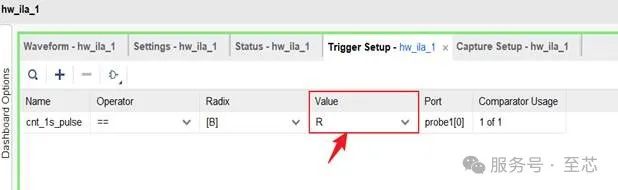

如图所示,是设置的方式,有0、1、X、R(上升沿)、F(下降沿)

如图所示,设置上升沿触发。

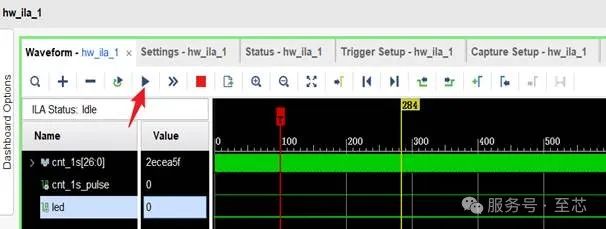

如图所示,点击条件触发。

-

FPGA

+关注

关注

1655文章

22282浏览量

630056 -

软件

+关注

关注

69文章

5296浏览量

90855 -

Vivado

+关注

关注

19文章

846浏览量

70454

原文标题:Xilinx(AMD)厂商 Vivado2018.3开发工具详细使用教程--新建工程、仿真、下板、逻辑分析仪使用

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Hbirdv2在vivado2018.3上的仿真工作

为什么不用2017.4或者2018.3呢?最稳定的vivado版本是哪一种?

vivado有哪几种常用IP核?如何去调用它们

Vivado软件仿真DDS核的过程中应该注意的问题

Vivado 2018.3 report_qor_suggestions怎么用

关于Vivado 2019.1的Dashboard功能详解

Vivado 2018.3软件的使用教程

Vivado 2018.3软件的使用教程

评论