在ZYNQ上移植UCOSIII

版本:Vivado2018.3

UCOS对Xilinx SDK适配的版本:Version1.45

注意:目前这个是Micrium官网的最新版本,该版本支持Vivado2019.1。但测试使用的是Vivado2018.3。

先看官网提供的库:

DesktopMicrium_Xilinx_Repo_1_45ucos_v1_45

将Micrium_Xilinx_Repo_1_45解压到一个固定位置(无中文路径的固定位置)

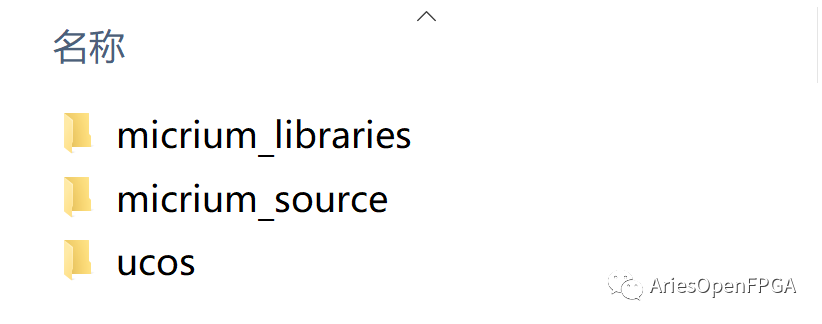

ucos_v1_45下面有三个文件夹,如图:

这三个文件夹都需要,但在SDK中仅需要定位到ucos目录下(待会会上图)

教程:

在Vivado上配置好硬件信息,因为大家用的板子不一样,需要配置的硬件信息也不一样,就不给大家工程了。

一、新建Vivado工程

建立好工程,新建BlockDesign,添加IP(搜索ZYNQ),根据自己板子配置各种信息,导出硬件信息。

二、配置SDK

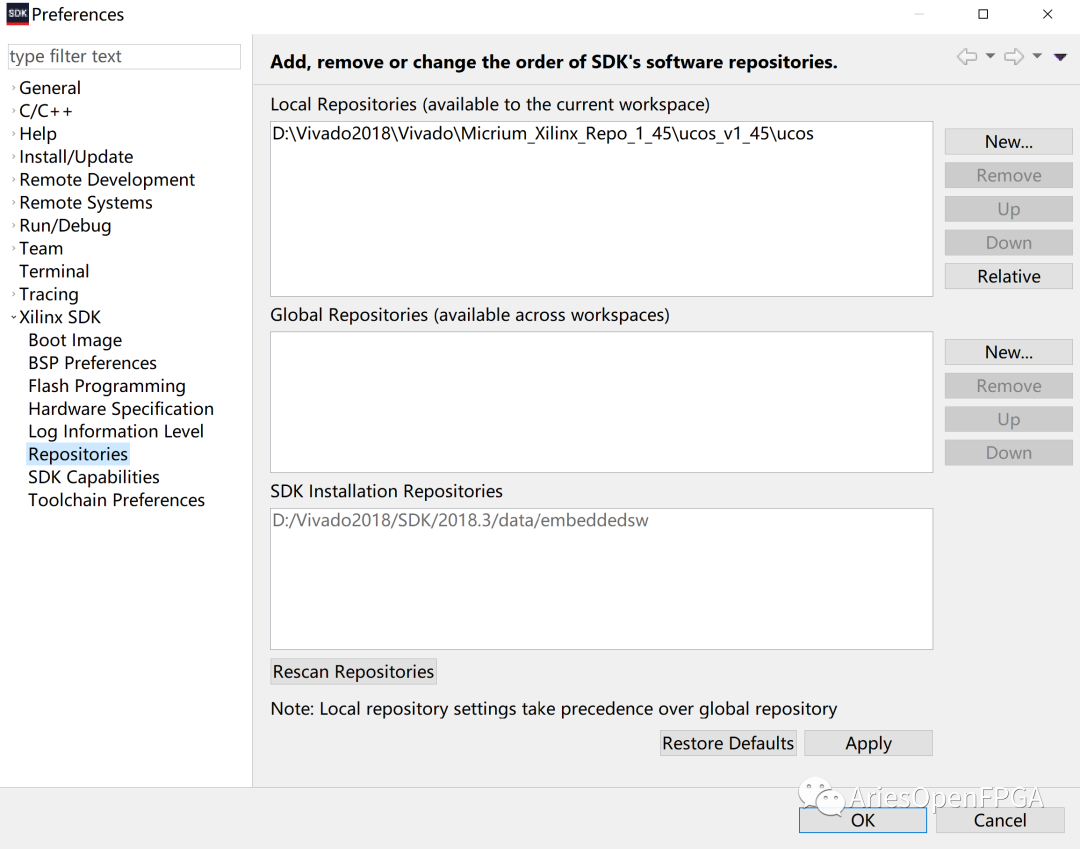

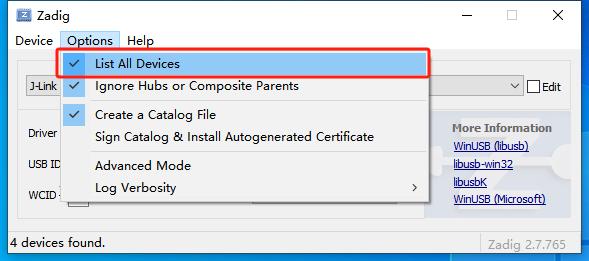

加载SDK,点击Xilinx然后点击Repositories进入如下界面

在LocalRepositories下选择new定位下载的库到ucos_v1_45ucos(你自己放文件的位置)但ucos_v1_45下的其它两个文件夹不要删除。

三、新建Application

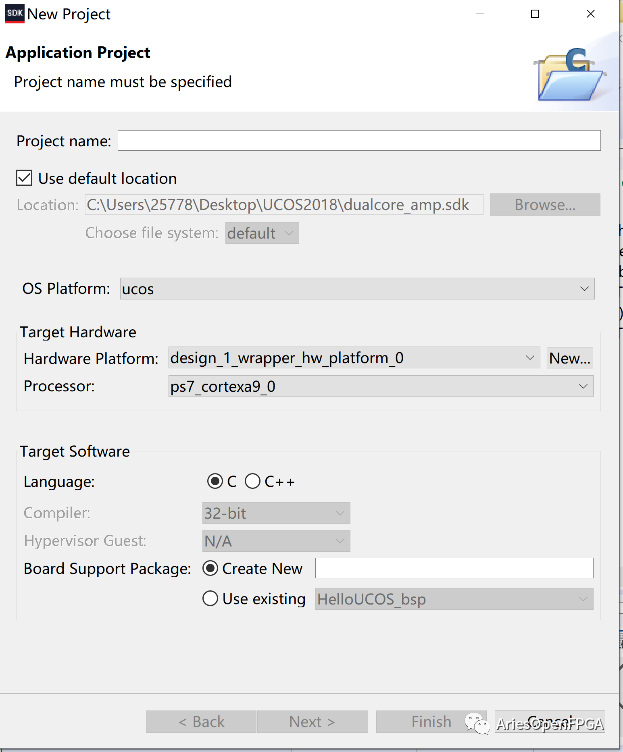

选择FilenewApplication进入如下界面

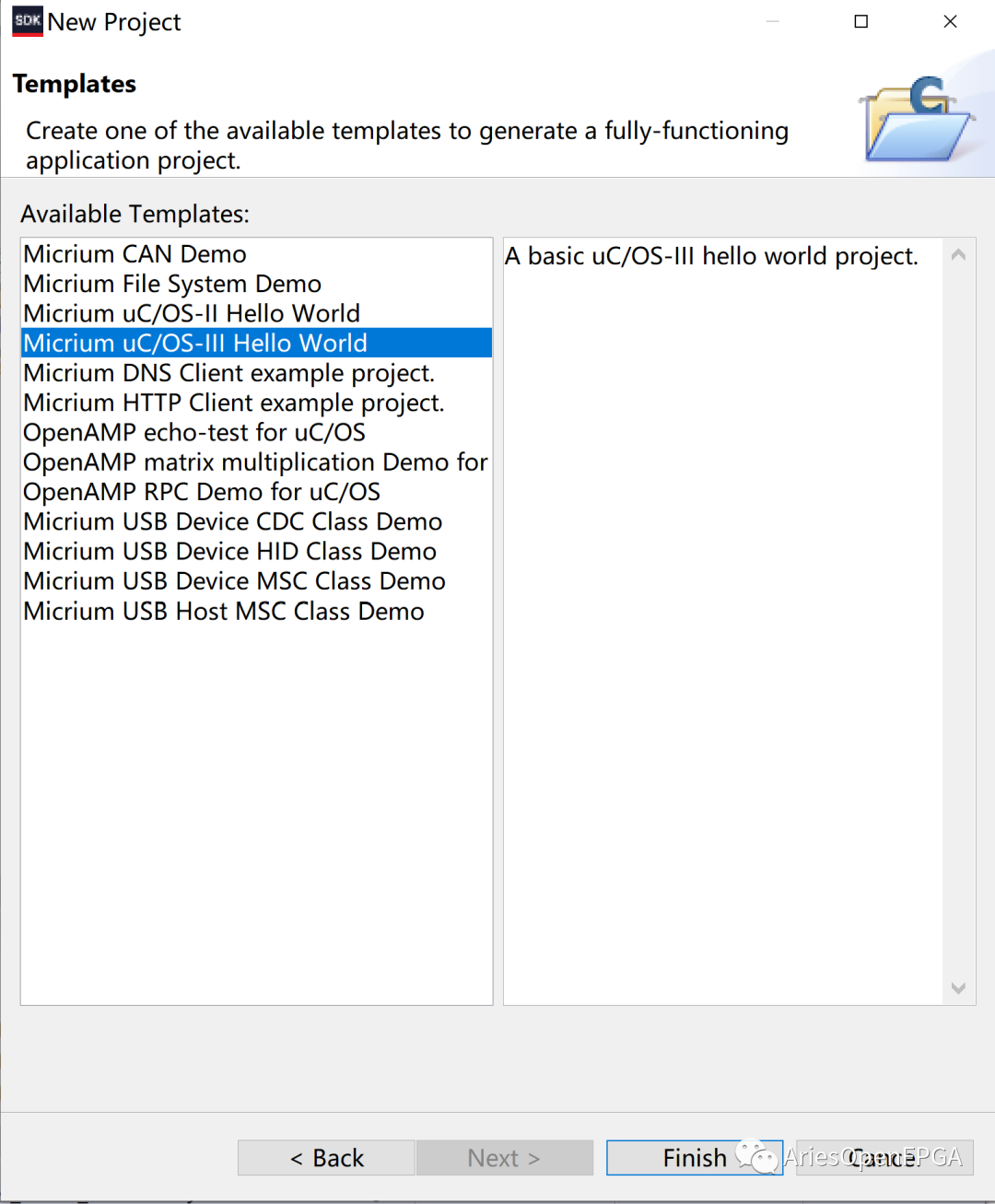

填好工程名字,在OS Platform 选择ucos,点击next进入Templates页面

点击页面中的Hello Word测试模板,点击Finish,编译即可。

这个教程是经过测试的,因为硬件平台不一致,给大家工程的意义不大,所以就不给了,这里仅给压缩的UCOS文件。

如果是新手不会自己建立Vivado工程以及硬件配置,可以参考市面上的ZYNQ教程,都很详细。使用他们ARM侧的裸机Hello Word教程,Vivado侧不用改,到SDK侧再按照我给的教程。祝大家使用UCOS顺利!

-

硬件

+关注

关注

11文章

3555浏览量

68733 -

Zynq

+关注

关注

10文章

625浏览量

49224 -

Vivado

+关注

关注

19文章

846浏览量

70454

原文标题:UCOSIII在ZYNQ上教程

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

利用 NucleiStudio IDE 和 vivado 进行软硬件联合仿真

Windows系统下用vivado将电路烧写到MCU200T板载FLASH的方法

FPNew开源浮点运算单元工程建立

vcs和vivado联合仿真

Nucleistudio+Vivado协同仿真教程

如何使用rt-thread studio中,使用 定制化的SDK建立工程?

AMD Vivado ChipScope助力硬件调试

使用DAP miniWiggle在ADS中进行对代码的工程下载以及进入调试模式进行调试,需要安装配置什么环境?

Vivado无法选中开发板的常见原因及解决方法

硬件调试:JLink 驱动配置与调试技巧

找高级硬件工程师以及硬件总监/经理

如何建立Vivado工程以及硬件配置

如何建立Vivado工程以及硬件配置

评论