Cortex-A15架构解析:它为什么这么强,今年的新手机趋势无异是全面向四核靠拢,不过同样是四核,在实际的性能上其实是千差万别。例如针对入门级主流市场的四核手机普遍采用的都是Cortex-A7以及Cortex-A9级别的CPU内核,这类内核性能、成本以及发热都会

今年的新手机趋势无异是全面向四核靠拢,不过同样是四核,在实际的性能上其实是千差万别。例如针对入门级主流市场的四核手机普遍采用的都是Cortex-A7以及 Cortex-A9 级别的CPU内核,这类内核性能、成本以及发热都会较低,因此在入门市场上大行其道。

而在高端智能手机中则出现了一些新的变化,除了去年就已经崭露头角的高通Krait系列架构四核外,ARM正统的Cortex-A15也开始走上了四核手机的舞台,例如三星的Exynos 5 Octa、NVIDIA 的Tegra 4。

Cortex-A15是ARM Cortex-A家族中目前最强劲的CPU内核架构,发布时间为2010年,德州仪器是最早(2011年)投产基于该架构处理器(型号为OMAP 5)的授权厂商。

和ARM的Cortex-A7、Cortex-A9等微架构相比,Cortex-A15有很大的不同。

A15和A9同样具备乱序执行,但是Cortex-A15具备(两倍)的指令发射端口和执行资源,指令解码能力也要高出50%,动态分支预测能力更强(采用了多层级分支表缓存),指令拾取带宽更强(128 bit vs 64 bit),这些都能让A15的流水线执行具备更高的效率。除此以外,A15采用了VFPv4浮点单元设计,能执行FMA指令以及硬件除法指令,相较而言A9的峰值向量浮点性能基本上只有A15的一半。

不过在现实中,A15 的对手应该是高通自行设计的 ARMv7A 兼容处理器架构 Krait。高通对 Krait 的架构细节透露并不是很多,大致上就是 3 个指令解码端口(和 A15 一样)、7个指令发射端口(A15 是8个)、4个发射端口(A15 是8个),具备4KB+4KB的单周期时延L0 Cache设计。

如果采用老掉牙的Dhrystone DMIPS/MHz作为性能衡量指标,Krait 是3.3,A9 是2.5,而A15则是3.5,从纸面上看Krait的确非常适合作为A15的对手。

不过Dhrystone的缺点是显而易见,它是完全可以塞进CPU的L1 cache里执行,这就意味着无法以此对L2 cache(A15是一体化设计,Krait是分离式设计,一体化设计可以减少内存交换导致的大量时延)、乱序执行的硬件效率/复杂性、内存子系统单元(A15的内存单元可以实现在一定条件下预执行一条加载指令,而Krait能否具备这样的能力尚不清楚)等诸多体系架构区别对实际性能的影响作出有价值评估。

当然,ARM采用的DMIPS指标实际上并非28年前的那个Dhrystone,而是来自EEBMC Coremark(其实 Coremark 就是前者的改善版本,主要是为了减少预优化、对测试有比较严格的规则),但是CoreMark同样可以塞进现今大多数处理器的L1 cache里,Dhrystone不能反映现今移动设备真实应用的问题在这里依然存在。

由于应用环境日趋复杂,要正确评估一个移动设备处理器的性能变得越来越复杂,因为现在的移动设备跑的网页浏览、三维游戏、音视频、人工智能等都不可能可以完全塞进L1 Cache里,因为这些应用牵涉到大量的数据处理。

这时候,人们在台式机性能评估上学到的经验和测试办法就可以在移动设备上采用了。对CPU测试来说,最合理的测试方式是采用多种计算规模的真实应用源代码以本机代码进行编译再进行测试,在这样的情况下移动设备的计算单元、内存单元都得以充分考验,测试结果最具参考价值。

能够获得业界(计算机工业、学术科研)官方认可的CPU测试当属SPEC.org的SPEC CPU,它就是采用源代码方式,让测试人员可以编译为本机代码来测试,许多处理器在研发伊始就采用SPEC CPU作为最重要的性能评估指标。

SPEC CPU的最新版本为CPU2006,但是CPU2006针对的是当前的台式机、工作站、服务器处理器应用环境,内存容量(CPU2006 支持多线程测试,因此要求的内存容量相当高,8线程处理器用16 GB内存也是有点勉强)和自身存储空间(未编译时就要数GB空间,编译后就要占用1xGB了)要求都较高,因此采用CPU2006对目前的移动设备来说是不太现实的。

SPEC CPU是每隔几年就更新一次,在CPU2006之前的旧版本为CPU2000,它的speed整数性能测试完全可以在1GB级别的移动设备上运行,在以前甚至有一些 CPU2000的测试被移植到GPU上做加速性能测试。

ARM阵营极少公布SPEC CPU测试结果,这当然也是有原因的,因为在过去的不少时间里,ARM针对的设备大都只有几百兆内存空间,塞进操作系统后,留给程序运行的空间就更少,此外由于省电先决的考量ARM处理器的性能其实真的不怎么样。

不过有意思的是,今年ARM阵营里的NVIDIA在发布Tegra 4的时候公布了CPU2000INT的测试结果:在1.9GHz 频率设定的NVIDIA参考平台里,Tegra 4的SPEC PU2000int_base 为1168。这个测试结果相当于2003年第四季度 SPEC.org 上公布的AMD K8 Sledgehammer 2GHz测试结果。

NVIDIA还进行了在小米手机2(采用高通 Snapdragon S4 Pro 即 APQ8064 1.7GHz)上的CPU2000测试,并且根据高通公布的S800相对S600在IPC(每周期指令)和频率上的变化幅度而估算出来的S800的CPU2000测试结果:

从图表来看,S600的CPUINT2000_base测试结果相当于Tegra 4的一半不到,这在很大程度上反映了Cortex-A15相对Krait系处理器的真实应用差别。

需要指出的是,双方的测试平台本身也是有一些影响的,例如小米手机2执行这个测试的时候,CPU频率是否存在降频现象,NVIDIA对此没有说明。

一般来说,像APQ8064在四核全速运行的时候,会在一段时间内由于过热而导致频率从最高的1.7GHz开始下降。当然,NVIDIA在这里公布的是speed模式下的CPU2000INT测试结果,这个模式下是单线程的测试,只有一个CPU内核会被使用。

比较遗憾的是高通对这个测试结果尚未提出异议(据说高通对于处理器性能的孰高孰低并不十分看重,他们戏称是卖基带送CPU),而CPU2000的配置对一般人来说是相当复杂的事情,所以这个测试暂时没有第三方使用同样的平台测试佐证。

威盛电子在发布Nano X2处理器的时候曾经公布过一份文件,里面也有采用CPU2000对Nano X2 1.2+GHz和Atom D525进行测试,其中gcc编译器出来的CPU2000 INT成绩分别为799和582,采用Intel编译器出来的成绩分别是955和725。

NVIDIA的Tegra 4的CPU属于ARMv7A指令集,因此编译器很可能是armcc或者gcc,NVIDIA新近收购的PGI是一家老牌编译器厂商,也许它能提供内部测试版给 NVIDIA,只是PGI过往从未发布过ARM系编译器。

-

Cortex-A15

+关注

关注

1文章

13浏览量

13427

发布评论请先 登录

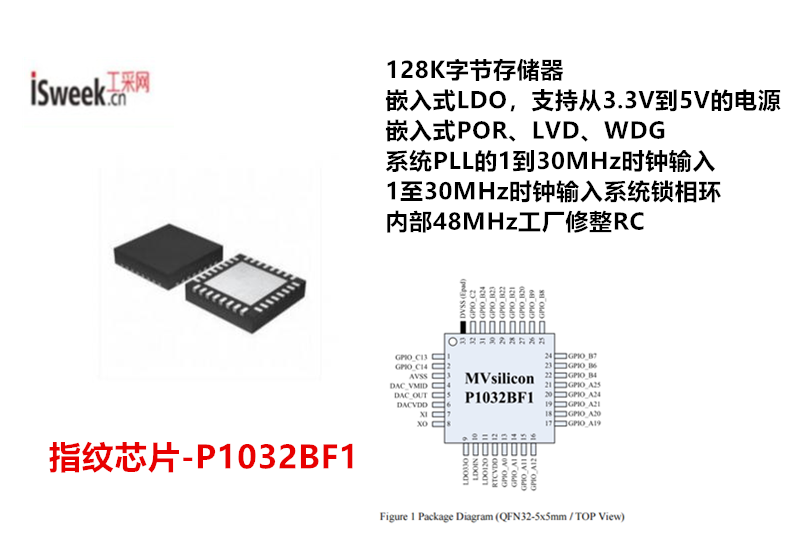

基于ARM Cortex-M3架构用于各类通用微控制器应用的指纹识别芯片-P1032BF1

onsemi FDP075N15A与FDB075N15A MOSFET深度解析

一文搞懂瑞芯微平台Trust架构:从原理到问题排查全解析

15W单输出开关电源PS - 15系列:设计与特性解析

Infineon XC2734X微控制器:16/32位架构的强劲之选

Cortex-M0和Cortex-M0+的区别

米尔RK3506核心板SDK重磅升级,解锁三核A7实时控制新架构

基于蜂鸟E203架构的指令集K扩展

迅为Hi3403V610开发板海思Cortex-A55架构核心板卡

【PZ-ZU15EG-KFB】——ZYNQ UltraScale + 异构架构下的智能边缘计算标杆

Cortex-A15架构解析:它为什么这么强

Cortex-A15架构解析:它为什么这么强

评论