概述

AD800和AD802采用二阶锁相环结构,对不归零(NRZ)数据执行时钟恢复和数据重定时。这种结构可支持20 Mbps至160 Mbps范围内的数据速率。此处所述的产品规定以标准电信比特率工作。AD800-45和AD800-52分别支持45 Mbps DS-3和52 Mbps STS-1。AD802-155支持155 Mbps STS-3或STM-1。

数据表:*附件:AD800 45或52 Mbps时钟和数据恢复IC技术手册.pdf

与其它基于PLL的时钟恢复电路不同,这些器件不需要前同步码或外部VCXO来锁定输入数据。电路利用两个控制环路采集频率和相位锁定。首先由频率采集控制环路采集输入数据的时钟频率,然后由锁相环采集输入数据的相位,并确保输出信号相位跟踪输出数据相位的变化。电路的环路阻尼取决于用户所选电容的值;它决定抖动峰值和性能,并影响采集时间。这些器件的抖动峰值为0.08 dB;当阻尼系数为5时,可以在4 X 10^5^ 位周期内锁定随机或加扰数据。

在采集过程中,鉴频器提供一个频率采集(FRAC)信号,指示器件尚未锁定输入数据。此信号是一系列脉冲,出现在输入数据与同步时钟信号之间的周跳点。一旦电路采集到频率锁定,FRAC输出就不会出现脉冲。

器件中内置经过精密调整的VCO,不需要用于设置中心频率的外部器件,从而也不需要对这些器件进行调整。无输入数据时,VCO提供器件中心频率±20%范围内的时钟输出。

取得专利的鉴相器具有出色的性能,因而AD800和AD802几乎没有码抖动。总环路抖动为20°峰峰值。抖动带宽由掩模可编程小数环路带宽决定。AD800用于90 Mbps以下的数据速率,标称环路带宽为中心频率的0.1%。AD802用于90 Mbps以上的数据速率,环路带宽为中心频率的0.08%。

所有器件均采用+5 V或-5.2 V单电源供电。

特性

- 标准产品

44.736 Mbps—DS-3

51.84 Mbps—STS-1

155.52 Mbps—STS-3 或STM-1 - 接受NRZ数据,无需前同步码

- 恢复时钟和重定时数据输出

- 锁相环型时钟恢复,无需晶振

- 随机抖动:20°峰峰值

- 码抖动:几乎消除

- 兼容10KH ECL

- 单电源供电:–5.2 V或+5 V

- 宽工作温度范围:–40°C至+85°C

特性

- 标准产品

44.736 Mbps—DS-3

51.84 Mbps—STS-1

155.52 Mbps—STS-3 或STM-1 - 接受NRZ数据,无需前同步码

- 恢复时钟和重定时数据输出

- 锁相环型时钟恢复,无需晶振

- 随机抖动:20°峰峰值

- 码抖动:几乎消除

- 兼容10KH ECL

- 单电源供电:–5.2 V或+5 V

- 宽工作温度范围:–40°C至+85°C

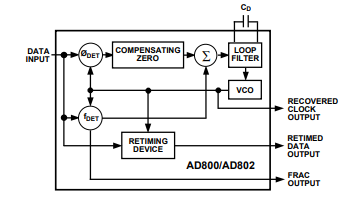

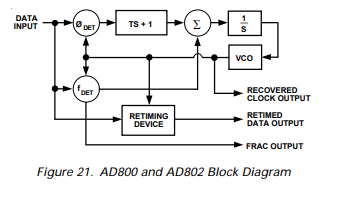

框图

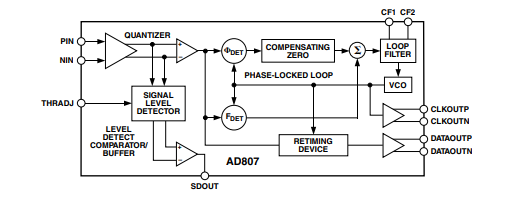

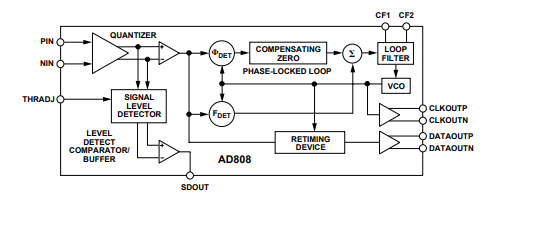

AD800 和 AD802 是用于从不归零制(NRZ)数据中恢复时钟的锁相环电路。其架构采用频率检测器来实现初始频率捕获,相关方框图见图 21。需注意,频率检测器始终处于工作状态。当锁相环(PLL)锁定时,频率检测误差为零,且频率检测器不再产生影响。由于频率检测器内置于电路中,因此无需额外的控制功能来启动捕获或改变捕获模式。

频率检测器还提供一个频率获取输出(FRAC),用于指示锁相环何时处于捕获状态。在捕获过程中,FRAC 输出是一系列宽度等于压控振荡器(VCO)周期的脉冲。这些脉冲在数据转换时出现。当 VCO 频率与最大密度(1010…)数据模式的频率匹配时,每次循环滑动都会在 FRAC 处产生一个脉冲。然而,对于随机数据,并非每次循环滑动都会在 FRAC 处产生脉冲。不过,FRAC 处的脉冲密度会随着数据转换的密度增加而增加。随着频率误差趋近于零,每个周期滑动产生脉冲的概率增加。当频率误差降为零后,FRAC 输出将不再有脉冲。此时,PLL 开始进入相位捕获阶段,在此设置下,大约需要 2000 个位周期才能保证数据恢复有效。等待 2000 个位周期后,最终的 FRAC 脉冲就会出现。

通过使用一种新的相位误差(专利技术),由数据转换密度变化(模式抖动)引起的抖动实际上被消除了。简而言之,测量得到的相位误差不会导致 VCO 相位增加,从而使平均运行速率由数据频率决定。所产生的抖动由 2ⁿ⁻¹ 伪随机码决定,其抖动幅度为 1/2 度,与随机抖动相比幅度较小。

AD802 - 155 的抖动带宽为中心频率的 0.08%。选择该参数是为了使 130 kHz 处的固有输入抖动衰减 3 dB。AD800 - 45 和 AD800 - 52 的抖动带宽分别为各自中心频率的 0.1%。AD800 或 AD802 的抖动掩码可编程范围为中心频率的 0.01% - 1%。一个具有极低带宽(0.01% 中心频率)的器件能够有效地过滤(净化)抖动定时参考。如果您的应用需要特殊的环路带宽,请咨询工厂。

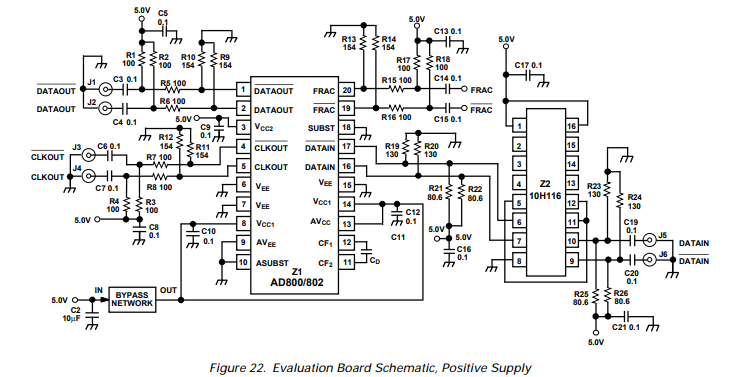

锁相环的阻尼比可通过单个外部电容器由用户编程。在 155 MHz 时,使用 0.22 μF 电容器可获得 10 的阻尼比。一般来说,阻尼比与 √(f_DATAC_D)成正比。在 155 MHz 时,使用 2.2 nF 电容器可获得 1 的阻尼比。较低的阻尼比允许更快的频率捕获;通常,捕获时间与电容值直接成比例。然而,当阻尼比接近 1 时,捕获时间不再直接与电容值相关。捕获时间包含两个部分:频率捕获和相位捕获。频率捕获始终与电容值成比例,但相位捕获由锁相环带宽决定,且与阻尼比无关。因此,0.08% 的锁相环带宽可设定最小捕获时间为 15000 个位周期。注意,阻尼因子为 1 时的捕获时间规定为 15000 个位周期,其中 13000 个位周期用于频率捕获,2000 个周期用于相位捕获。将此与阻尼比为 5 时规定的 400000 个位周期的捕获时间进行比较;此时完全是频率捕获,相位捕获的 2000 个位周期可忽略不计。

虽然较低的阻尼比可加快捕获速度,但它也会增加抖动传输响应(抖动峰值)。例如,对于阻尼比为 10 的情况,抖动峰值为 0.02 dB,但对于阻尼因子为 1 的情况,抖动峰值为 2 dB。

-

定时

+关注

关注

1文章

124浏览量

26290 -

时钟

+关注

关注

11文章

1953浏览量

134532 -

数据恢复

+关注

关注

10文章

688浏览量

18790

发布评论请先 登录

AD800 45或52 Mbps时钟和数据恢复IC

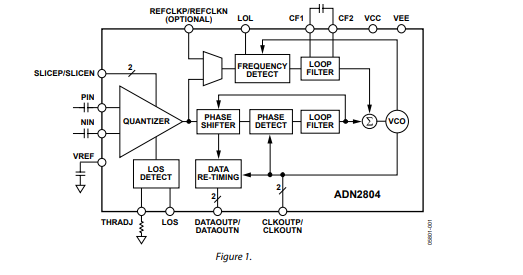

ADN2804:带集成限幅放大器的622 Mbps时钟和数据恢复IC产品说明书

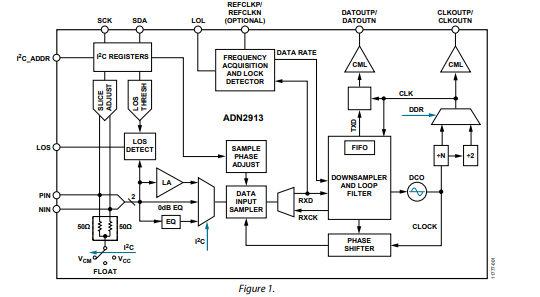

ADN2913:连续速率6.5 Mbps至8.5 Gbps时钟和数据恢复IC,集成限幅放大器/均衡器数据表

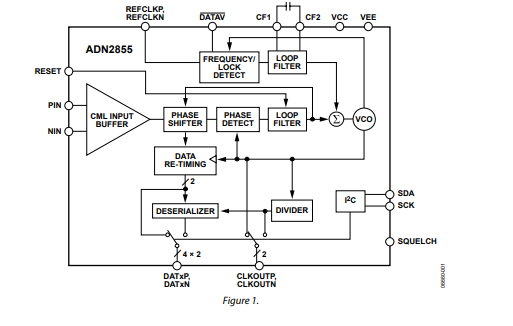

ADN2855:多速率155 Mbps/622 Mbps/1244 Mbps/1250 Mbps突发模式时钟和数据恢复IC,带解串器产品手册

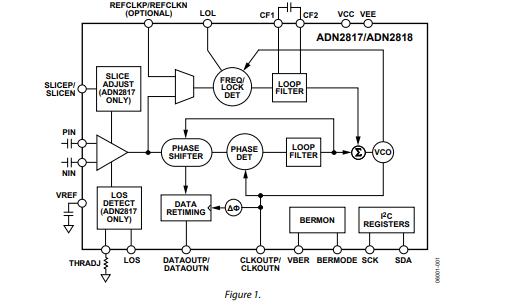

ADN2817/ADN2818:连续速率10 Mbps至2.7 Gbps时钟和数据恢复IC数据表

ADN2913连续速率6.5 Mbps至8.5 Gbps时钟和数据恢复IC,集成限幅放大器/均衡器技术手册

ADN2855多速率155 Mbps/622 Mbps/1244 Mbps/1250 Mbps突发模式时钟和数据恢复IC技术手册

ADN2817连续速率10 Mbps至2.7 Gbps时钟和数据恢复IC技术手册

AD800 45或52 Mbps时钟和数据恢复IC技术手册

AD800 45或52 Mbps时钟和数据恢复IC技术手册

评论