多年来,封装技术并未受到大众的广泛关注。但是现在,尤其是在AI芯片的发展过程中,封装技术发挥着至关重要的作用。2.5D封装以其高带宽、低功耗和高集成度的优势,成为了AI芯片的理想封装方案。

在2.5D封装领域,英特尔的EMIB和台积电的CoWoS是两大明星技术。众所周知,台积电的CoWoS产能紧缺严重制约了AI芯片的发展,这正是英特尔EMIB技术可以弥补的地方。本文我们将以英特尔EMIB为例,深入解析2.5D封装之所以能成为AI芯片的宠儿的原因。

为何EMIB是AI领域的理想选择?

2.5D封装并不是一个全新的概念,但它在AI芯片领域的应用却焕发出了新的生命力。简单来说,2.5D封装是一种通过硅中介层(Silicon Interposer)或嵌入式桥接技术(如英特尔的EMIB)将多个芯片水平连接起来的技术。与传统的2D封装相比,它允许在单一封装内集成更多功能单元,比如CPU、GPU、内存(HBM)和I/O模块;而与复杂的3D堆叠相比,它又避免了过高的制造难度和热管理挑战。这种“不上不下的中间状态”恰恰为AI芯片提供了完美的平衡。

AI芯片的一个显著特点是需要高带宽和低延迟的芯片间通信。例如,训练一个深度学习模型时,GPU需要与高带宽存储器(HBM)快速交换数据,而传统的封装技术往往受限于互连带宽和功耗。2.5D封装通过在芯片间引入高密度互连通道,显著提升了数据传输效率,同时保持了相对简单的制造流程。这使得它特别适合AI加速器和数据中心处理器等高性能应用。

“我经常被问到一个问题:为什么EMIB是AI领域的理想选择?是什么让这项技术对这些应用如此适合?”英特尔先进系统封装与测试事业部副总裁兼总经理Mark Gardner表示。他通过一张图详细解析了EMIB作为AI加速器理想封装技术的优势,并总结了EMIB的五大关键优势:

第一,成本更低。EMIB采用小型硅桥连接芯片,一个晶圆上就能生产数千个桥接单元,极大提高了利用率。相比之下,传统晶圆级封装在制造复杂结构(如含12个HBM堆叠和多个光罩芯片的大型封装)时,成品率低且浪费严重。而EMIB不仅提升了良率,还能在HBM数量增加时,展现出成本优势的指数级增长。

第二,更高良率。与其他2.5D技术相比,EMIB减少了复杂的工艺步骤。传统晶圆级封装需要“芯片对晶圆”(Chip-on-Wafer)流程,涉及模具、凸点等多重工序,增加了出错风险。EMIB简化了这些步骤,自然带来了更高的生产稳定性。

第三,更快生产周期。更少的工艺步骤不仅提升良率,还缩短了生产时间。与动辄数天的传统流程不同,EMIB能将周期缩短数周。在AI市场瞬息万变、上市时间至关重要的背景下,提前几周拿到加电测试数据、硅片验证数据对客户意义重大。

第四,更强扩展性。EMIB将硅桥嵌入基板,而基板制造通常基于大型方形面板。这种设计大幅提高了基板利用率,特别适合需要集成更多HBM或复杂工作负载的大型封装。对于AI客户来说,这意味着更强的适应性和性能潜力。

第五,为客户提供更多选择。英特尔代工致力于为客户提供多样化的选项。市场上已有既定的行业解决方案,而EMIB技术为客户提供了一种替代方案。在某些情况下,客户可以选择多源供应,也可以选择单一来源,关键是EMIB为他们提供了灵活性和选择权。EMIB技术已经在生产中应用了近十年,拥有成熟的供应链。这些因素共同构成了EMIB作为AI领域(尤其是加速器)理想平台的原因。

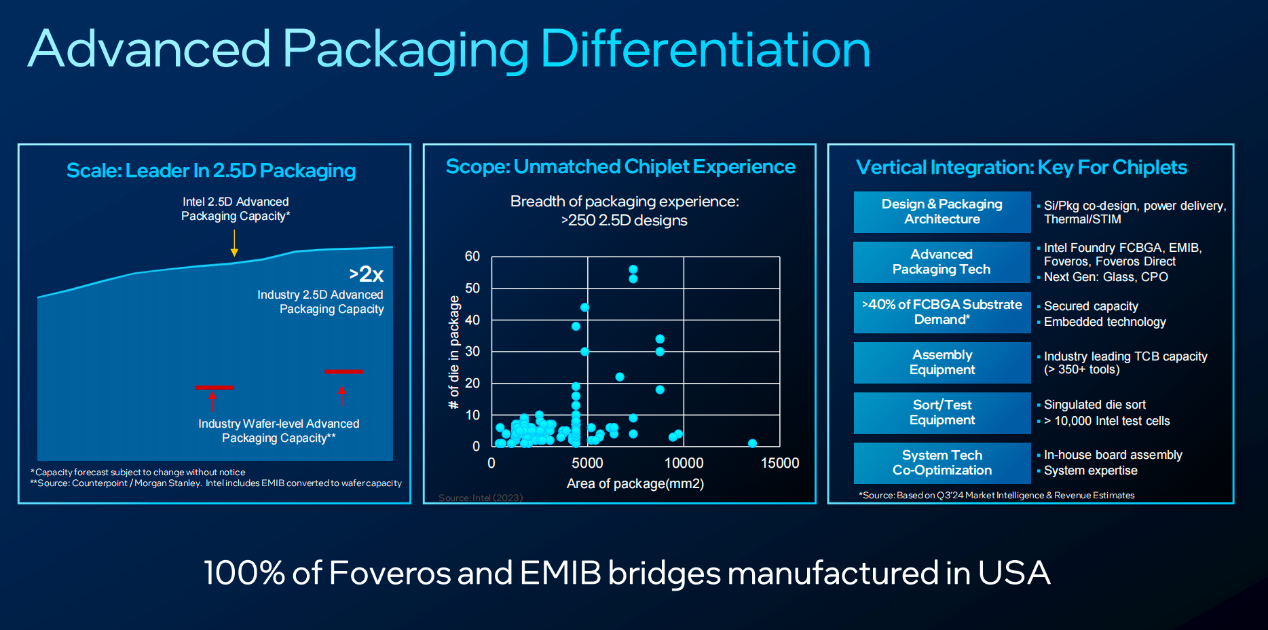

近年来,2.5D封装产能一直面临限制,特别是在某些市场需求不断增长的情况下,封装产能不足问题愈发显著。然而,英特尔的EMIB技术在这一领域具有明显的产能优势。通过结合Foveros 2.5D和EMIB 2.5D,英特尔的综合产能已经超过行业水平的两倍,对于那些担心需求波动或增长无法得到满足的客户,英特尔的解决方案无疑具有巨大的吸引力。据英特尔透露,AWS和Cisco在数据中心服务器和AI加速器产品领域就采用了英特尔的先进封装技术。

英特尔领衔封装技术数十年

作为封装技术的先锋,英特尔在过去五十多年里一直处于行业领先地位。从早期的引线键合架构(Wire-Bond)到倒装陶瓷芯片(Flip-Chip Ceramic)和多芯片(Multi-Chip)封装技术,英特尔不断推动封装技术的发展。如今,它通过与生态系统伙伴合作制定标准,带领整个行业迈入先进封装的新时代,包括2.5D、3D乃至3.5D技术。以英特尔EMIB 2.5D为例,其首个产品已量产近十年,这些成果并非一蹴而就,而是长期积累的结晶。

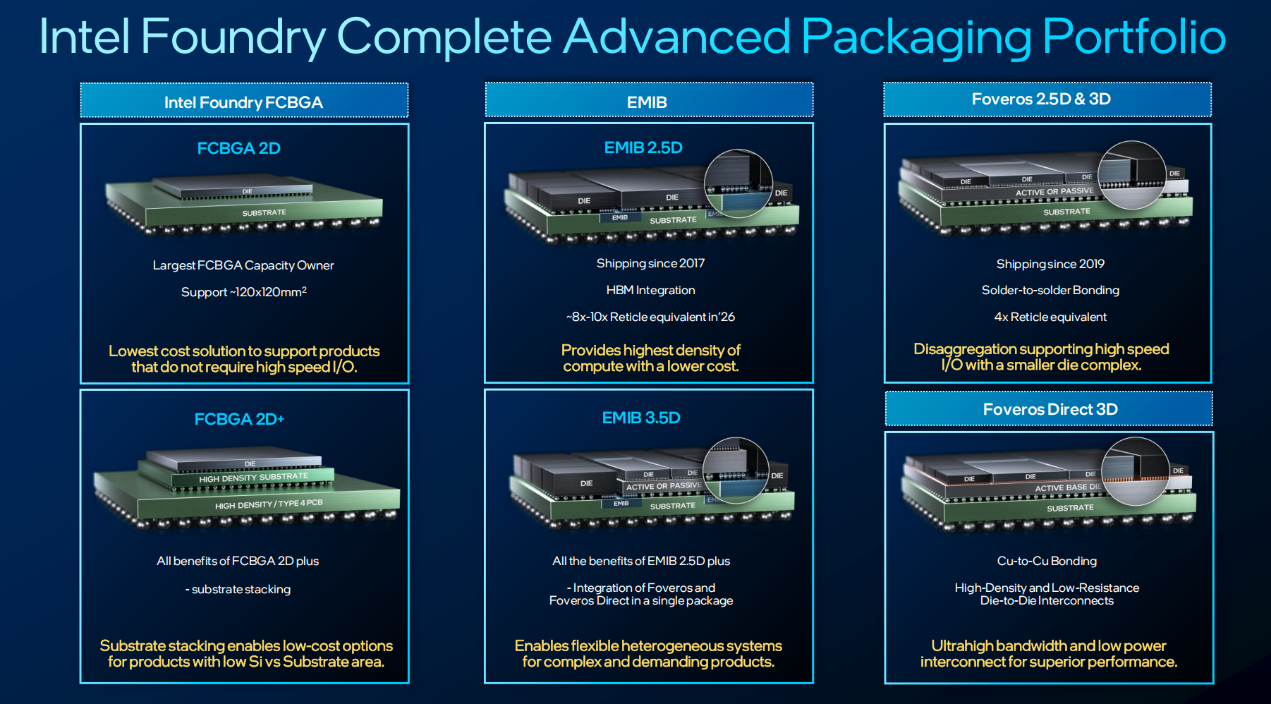

目前,英特尔代工提供了一套完整的先进封装产品组合,满足从低成本到高性能的多样化需求:

首先,成本低廉的FCBGA。FCBGA(Flip-Chip Ball Grid Array)分为两种版本:FCBGA 2D和FCBGA 2D+。FCBGA 2D是传统的有机封装技术,至今仍在量产。它成本低廉,适合I/O需求少、不需要高速连接的产品,是许多细分市场的理想选择。而FCBGA 2D+在FCBGA 2D基础上加入了基板层叠技术(Substrate Stacking),针对主板连接尺寸大但芯片复杂度不高的场景,能有效降低客户为高密度基板支付的额外成本。这种技术在网络和交换设备领域尤其受欢迎。

接着,EMIB系列主打高性能。EMIB(嵌入式多芯片互连桥接)包括EMIB 2.5D和EMIB 3.5D两种。EMIB 2.5D通过基板中的微型硅桥连接单层芯片或HBM堆叠,实现高密度、低功耗的芯片间通信。虽然它也用于消费类产品,但在AI和高性能计算(HPC)领域表现尤为出色。EMIB 3.5D与EMIB 2.5D类似,都采用嵌入基板中的硅桥技术。不同之处在于EMIB 3.5D引入了3D堆叠技术,将芯片叠放在有源或无源基板上。这不仅保留了EMIB的连接优势,还增加了垂直堆叠的灵活性。某些IP更适合垂直堆叠,而不是水平连接。此外,由于封装的复杂度较高,客户希望利用EMIB技术将这些堆叠连接起来,而不是使用大型的无源或有源中介层。

最后则是Foveros技术,Foveros技术分为Foveros 2.5D和Foveros 3D。Foveros 2.5D采用焊料连接芯片与晶圆,适合将高速I/O与小型芯片组分离的场景。而Foveros Direct则使用铜-铜直接键合,提供最高带宽和最低功耗的互连,性能无可匹敌。在AI和HPC应用中,这些技术还能灵活组合——比如Foveros Direct 3D搭配HBM,再融入EMIB 3.5D,形成一个多技术融合的封装方案。

英特尔代工的新招

半导体行业正迎来一个全新的发展阶段,传统的芯片设计与制造模式已不足以应对AI和高性能计算带来的复杂需求。在这一转型期,系统级代工厂(Systems Foundry)和系统技术协同优化(System Technology Co-Optimization)的重要性日益凸显。作为代工厂或服务提供商,英特尔认为,通过这些协同优化策略,可以更好地满足客户需求,打造更强大的产品。

在这一背景下,英特尔不仅专注于传统封装技术,还扩展到了系统级架构和设计服务。比如,热建模与优化、功耗建模与优化,这些都是英特尔多年来与内部产品部门合作积累的技术成果,并广泛应用到各种产品中。一个典型的例子是几年前推出的英特尔数据中心 GPU Max 系列。这款产品把近50块芯片集成到一个封装里,这些芯片基于五种不同的制造工艺,有些来自英特尔,有些来自第三方代工厂。要实现这样的产品,光靠技术本身还不够,还需要硅芯片与封装的协同设计,再加上热管理、功率传输等环节的优化,才能让这么多芯片在一个封装里高效工作。

说到复杂封装,英特尔还在细节上下足了功夫。比如在大型封装中,芯片和基板可能会因为尺寸大而出现翘曲问题。英特尔通过优化工艺流程和主板设计,解决了这些翘曲边缘的管理问题,确保即使在高复杂度下,产品性能依然稳定可靠。

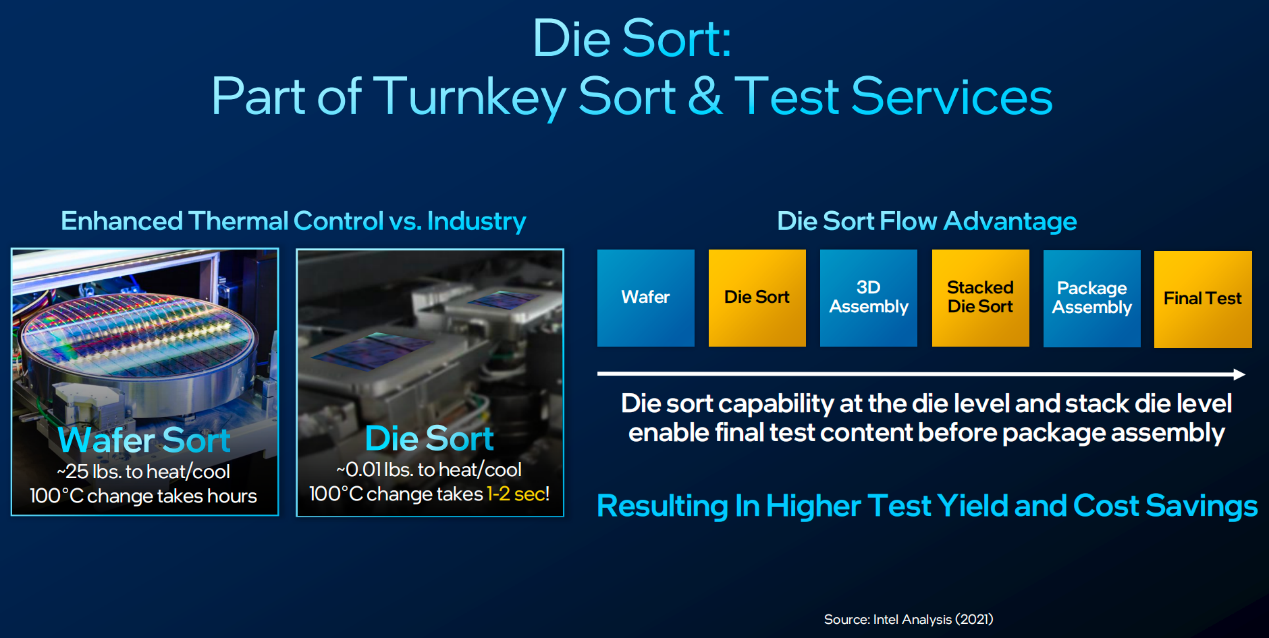

当然,好封装离不开好测试。芯片测试是确保封装质量的关键一环,尤其是要保证进入封装的芯片都是“已知良品”(Known Good Die,简称KGD)。如果一个封装里只有一块芯片,测试还算简单。但像现在这样,一个封装可能包含50块不同功能的芯片,比如GPU、I/O单元和HBM堆叠,只要有一块坏芯片,整个封装就可能报废。所以,提前检测出问题芯片,避免浪费其他好芯片,显得特别重要。

为此,英特尔开发了“裸片测试”(Die Sort)技术,这项技术已经在生产中用了十多年。它的做法是先把整片晶圆切成单个裸片,然后在组装到基板之前进行测试。因为裸片很小,热量控制非常精准,甚至可以在1秒内让温度变化100摄氏度。这种高精度的测试能提前发现缺陷,比如GPU或计算单元的问题,从而提高生产效率和良率。过去,这种提前检测已经很有价值,但现在,当一个封装的材料和芯片成本高达几千美元时,它的重要性就更加凸显了。尤其在如今的产品中,可能包含10片、20片甚至50片芯片,良品管理成了重中之重。通过在制造的早期加入测试环节,英特尔能确保每一步都用的是好芯片,避免后期更大的损失。

与此同时,英特尔的代工服务也在变得更灵活。Mark Gardner提到,客户现在可以根据需要自由选择服务:比如只用英特尔的EMIB封装技术,芯片则交给其他代工厂生产;或者只用英特尔的裸片测试能力。这种“按需定制”的模式也延伸到了晶圆制造层面,让客户能专注于对自己最重要的环节,获得最有价值的服务。

英特尔已完成超过250个2.5D设计项目,涵盖消费电子、FPGA、服务器数据中心和AI加速器等多领域应用,2.5D技术已广泛投入生产。英特尔还提供增值服务,帮助客户优化产品设计,包括硅与封装协同设计、功率传输、热管理等方面,凭借丰富的经验与技术积累,协助客户提升产品性能。

值得一提的是,英特尔还跟其他代工厂,比如台积电和三星,保持长期合作。他们制定了兼容的设计规则,确保这些代工厂生产的晶圆能无缝适配英特尔的封装技术。这不仅给了客户更多选择,也让不同供应商的技术能自由组合,满足多样化的市场需求。

未来展望:更大封装与玻璃基板的应用

展望未来,英特尔正在积极推动封装技术的进一步发展,特别是在封装尺寸和材料选择上。Gardner透露,英特尔正在研发120毫米×120毫米的超大封装尺寸,并计划在未来一到两年内实现量产。这一技术的推进将进一步拓展AI加速器的封装能力,满足更大规模计算需求。

此外,英特尔对玻璃基板和玻璃核心技术的投资也在不断加大。随着封装尺寸的增大,传统材料的局限性变得愈加明显,玻璃基板因其出色的性能和扩展性,逐渐成为未来封装技术的重要组成部分。Gardner认为,玻璃基板将在未来几年成为主流,将推动封装技术的持续扩展和创新。

结语

随着AI技术的不断进步和应用场景的不断扩展,封装技术的创新将成为推动产业变革的重要动力。英特尔通过EMIB、Foveros等多项先进封装技术,不断突破技术瓶颈,提供高效、灵活的解决方案,引领着封装技术的未来方向。

审核编辑 黄宇

-

芯片

+关注

关注

463文章

54463浏览量

469578 -

英特尔

+关注

关注

61文章

10326浏览量

181119 -

封装

+关注

关注

128文章

9339浏览量

149062 -

AI

+关注

关注

91文章

41295浏览量

302669

发布评论请先 登录

基于 HT 的 2.5D 组态可视化技术方案与场景实现

BK7259 具备边缘AI能力的高级音视频Wi-Fi +蓝牙SOC芯片/规格书/原理图

AI Agent发展浪潮下,芯片级安全为何成为关键?主流芯片厂商如何布局?

台积电如何为 HPC 与 AI 时代的 2.5D/3D 先进封装重塑热管理

先进封装成破局,博通率先落地3.5D,6000mm²超大集成

2D、2.5D与3D封装技术的区别与应用解析

浅谈2D封装,2.5D封装,3D封装各有什么区别?

Socionext推出3D芯片堆叠与5.5D封装技术

3D封装的优势、结构类型与特点

华大九天推出芯粒(Chiplet)与2.5D/3D先进封装版图设计解决方案Empyrean Storm

2.5D封装为何成为AI芯片的“宠儿”?

2.5D封装为何成为AI芯片的“宠儿”?

评论