一、填空

1.PCB上的互连线按类型可分为()和() 。

2.引起串扰的两个因素是()和()。

3.EMI的三要素:()。

4.1OZ铜 的厚度是()。

5.信号在PCB(Er为4)带状线中的速度为:()。

6.PCB的表面处理方式有:()。

7.信号沿50欧姆阻抗线传播.遇到一阻抗突变点.此处阻抗为75欧姆.则在此处的信号反身系数为()。

8.按IPC标准.PTH孔径公差为:()NPTH孔径公差为:()。

9.1mm宽的互连线(1OZ铜厚)可以承载()电流。

10.差分信号线布线的基本原则:()。

11.在高频PCB设计中,信号走线成为电路的一部分,在高于500MHz频率的情况下,走线具有()特性。

12.最高的EMI频率也称为(),它是信号上升时间而不是信号频率的函数。

13.大多数天线的长度等于某一特定频率的λ/4或λ/2(λ为波长)。因此在EMC规范中,不容许导线或走线在某一特定频率的λ/20以下工作,因为这会使它突然变成一根高效能的天线,()会造成谐振。

14.铁氧体磁珠可以看作()。在低频时,电阻被电感短路,电流流向();在高频时,电感的高感抗迫使电流流向()。在高频时,使用铁氧体磁珠代替电感器。

15.布局布线的最佳准则是()。

二、判断

1.PCB上的互连线就是传输线. ( )

2.PCB的介电常数越大.阻抗越大.( )

3.降底PP介质的厚度可以减小串扰.( )

4.信号线跨平面时阻抗会发生变化.( )

5.差分信号不需要参考回路平面.( )

6.回流焊应用于插件零件.波峰焊应用于贴片零件.( )

7.高频信号的回路是沿着源端与终端两点距离最短路径返回.( )

8.USB2.0差分的阻抗是100欧姆.( )

9.PCB板材参数中TG的含义是分解温度.( )

10.信号电流在高频时会集中在导线的表面.( )

三、选择

1、影响阻抗的因素有( )

A.线宽

B.线长

C.介电常数

D.PP厚度

E.绿油

2.减小串扰的方法( )

A.增加PP厚度

B.3W原则

C.保持回路完整性;

D.相邻层走线正交

E.减小平行走线长度

3.哪些是PCB板材的基本参数( )

A.介电常数

B.损耗因子

C.厚度

D.耐热性

-

pcb

+关注

关注

4391文章

23742浏览量

420759

发布评论请先 登录

人工智能工程师高频面试题汇总:循环神经网络篇(题目+答案)

用30道电子工程师面试题来拷问堕落的你...

作为一名PCB质检工程师,我为什么在用手持式面铜测试仪?

每周推荐!硬件设计指南+无刷电机原理图大全+工程师面试题库汇总

最全的硬件工程师笔试试题集

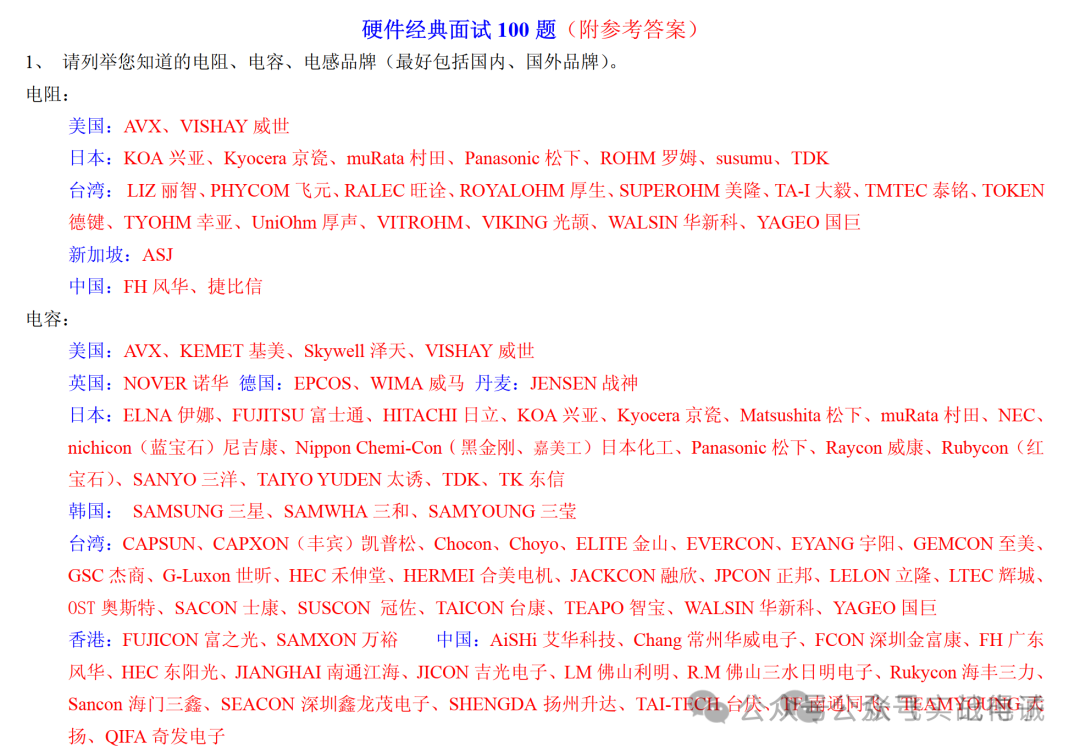

硬件工程师面试/笔试经典 100 题

硬件工程师面试必看试题(经典)

长沙怎么这么难招硬件工程师呀

【面试题】人工智能工程师高频面试题汇总:概率论与统计篇(题目+答案)

电子工程师的PCB设计经验

【面试题】人工智能工程师高频面试题汇总:机器学习深化篇(题目+答案)

【面试题】人工智能工程师高频面试题汇总:Transformer篇(题目+答案)

PCB工程师面试题_这些你是否都会

PCB工程师面试题_这些你是否都会

评论