文章来源:学习那些事

原文作者:赵先生

本文介绍了影响集成电路可靠性的Cu/low-k互连结构中的电迁移问题。

概述

在集成电路尺寸朝着深亚微米级不断微缩的进程中,金属互连引发的诸如RC延迟(RC delay)、信号串扰以及功耗等一系列问题,给芯片性能的提升带来了极为严峻的挑战。图1清晰呈现出栅延迟和互连延迟与工艺节点之间的关联情况。为了成功攻克这些难题,推动集成电路持续向前发展,业界主要从以下三个关键方面展开了改进工作:其一,选用电阻率更低的金属材料,以铜替代铝;其二,采用低介电常数(low-k)材料来替换二氧化硅;其三,增加布线层数,从0.13um工艺时的7至8层,逐步增加到如今的十几层,例如Intel的10nm工艺便包含13个互连层。

图1:栅延迟和互连延迟与工艺节点的关系

铜互连

互连技术在初始阶段所采用的金属材料为铝。然而,当工艺发展至0.13um及其以下尺度时,铝逐渐被铜所取代。这一替换使得RC延迟得以显著降低,大约减小了40%。当工艺节点进入到28nm及以下时,通常会添加少量的Mn元素,以此来提升铜的EM(电质迁移性能)。与铝相比,铜具备诸多显著优势:其一,铜的电阻率较低,其电阻率数值为1.67uΩ·cm,而铝的电阻率为2.66uΩ·cm;其二,铜的抗电迁移能力较强,铜发生电迁移的电流密度上限能够达到5.5X10⁶A/cm²,而铝在电流密度仅达到2.5X10⁶A/cm²时就会出现迁移现象;其三,铜具有熔点较高的特性,其散热能力良好,并且载流能力远远强于铝。不过,在铜互连工艺的发展历程中,也遭遇了两大棘手的挑战:其一是铜污染问题;其二是沉积问题。

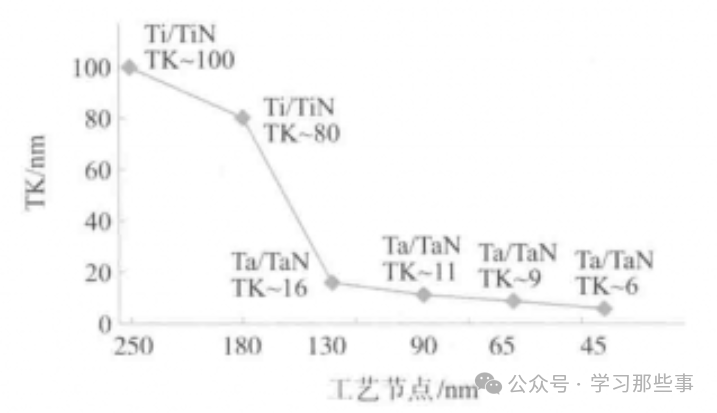

所谓铜污染,指的是铜原子(离子)在介电质层中具有较强的扩散倾向,这种扩散会对介电质层造成污染,进而导致铜互连线之间出现电压衰减的情况,严重时甚至会引发互连层间的电压击穿现象。为有效应对这一问题,人们研发出了阻挡层工艺,通过采用氮化钽/钽(TaN/Ta)结构对铜进行包裹,以此来阻挡铜原子(离子)的扩散。在这一结构中,Ta对铜能够起到良好的黏附作用,同时具备出色的定型效果;而TaN不仅对铜有着良好的阻挡能力,而且与介电层之间的黏附性也十分优良。图2展示的便是铜互连的示意图。由此可见,铜互连的电阻值实际上是由铜本身的电阻以及阻挡层TaN/Ta的电阻共同构成。由于铜的电阻率为1.67uΩ·cm,钽的电阻率为30uΩ·cm,氮化钽的电阻率为210μΩ·cm,所以互连线的阻值大致可表示为R≈R铜+R阻挡层 ,图2同时给出了铜互连电阻的等效图。倘若想要降低铜互连的电阻,可行的方法主要有两种:一种是降低金属线本身的电阻;另一种则是减小阻挡层的电阻。而最为直接的做法便是减小TaN/Ta阻挡层的厚度。从图3中可以清晰地看到不同工艺节点下阻挡层厚度的变化情况。随着工艺的不断发展,阻挡层厚度持续变薄,这一变化导致台阶覆盖性逐渐变差,同时对铜的黏附力也会相应地减弱。此外,随着特征尺寸不断微缩,深宽比逐渐增大,在进行沟槽和通孔的填充过程中,极易产生空洞,这些空洞的出现会对器件的可靠性造成严重影响。基于此,目前业界主要借助一些新工艺(如原子层沉积)来改善填充效果。然而,需要注意的是,阻挡层厚度不能无限制地减薄,它必须保持一定的厚度,才能够充分发挥出良好的阻挡作用。因此,在10nm及以下工艺节点,业界开始采用新材料钴作为阻挡层材料。

图2:铜互连示意图及电阻等效图

图3:不同工艺节点下阻挡层厚度的变化

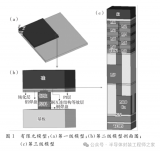

在以往铝的沉积过程中,是通过铝与氯气反应所产生的氯化物来实现对铝互连线的刻蚀,从而获得期望的图形。但铜的氟化物和氯化物在低温环境下都难以挥发,这就使得传统的干法刻蚀工艺无法应用于铜的刻蚀。为解决这一难题,人们发明了大马士革工艺和化学机械平坦化抛光研磨工艺(CMP)。具体操作方法为:首先沉积介质层,接着刻蚀出铜互连线的图案,随后进行铜的填充,最后通过CMP工艺将表面磨平。大马士革工艺一般可分为单大马士革工艺和双大马士革工艺。其中,单大马士革工艺相对较为简单,就是先对介质层进行刻蚀,然后进行金属填充,例如后段互连中的第一层金属(M1)就采用这种方式;而双大马士革工艺则需要刻蚀出通孔(via)和沟槽(trench),之后再进行金属填充,M1之后的金属层大多采用该方式。在双大马士革工艺发展的初期,又可细分为先通孔(via first)和先沟槽(trench first)两种方式。如图4(a)所示为先通孔方式,即先进行通孔的刻蚀,然后再进行沟槽刻蚀。这种方法能够较好地对通孔的尺寸进行控制,但其存在一些缺点:①沟槽的深度控制难度较大;②通孔中填充介质的高度需要进行精密控制,否则会导致上部介质形貌变差;③整个过程需要进行两次刻蚀动作,容易形成等离子体损伤。如图4(b)所示为先沟槽方式,即先进行沟槽刻蚀,之后再进行通孔刻蚀。这种方法的制程相对较为简单,但也存在一些不足之处:①对光刻工艺的套准精度要求较高;②通孔底部尺寸很难控制;③沟槽的深度控制难度比较大;④同样需要进行两次刻蚀,容易形成等离子体损伤。

图4:双大马士革工艺的两种流程

随着器件尺寸的不断微缩,大马士革工艺面临着如何精准控制沟槽尺寸以及降低介质层损伤的严峻挑战。为解决这一问题,业界开发出了如图5所示的金属硬掩模层一体化刻蚀工艺(hard mask all-in-one)。该工艺的具体操作方法是:首先将沟槽图案转移到硬掩模上,然后通过光刻定义出通孔形貌,并通过一体化刻蚀形成通孔和沟槽,最后进行金属填充和CMP平坦化处理。金属硬掩模层一体化刻蚀工艺具有以下显著优点:①由于只需将沟槽图案转移到硬掩模上,无需在刻蚀介质层中刻出沟槽,所以使用的光刻胶(PR)厚度较薄,这使得光刻分辨率能够得到显著提高;②相较于光刻胶,硬掩模与介质层之间的选择比更高,能够更为有效地控制关键尺寸,使刻蚀形貌更加理想;③采用一体化刻蚀方式,能够有效地避免等离子体损伤。

图5:金属掩膜层一体化刻蚀工艺流程示意图

Low-k材料

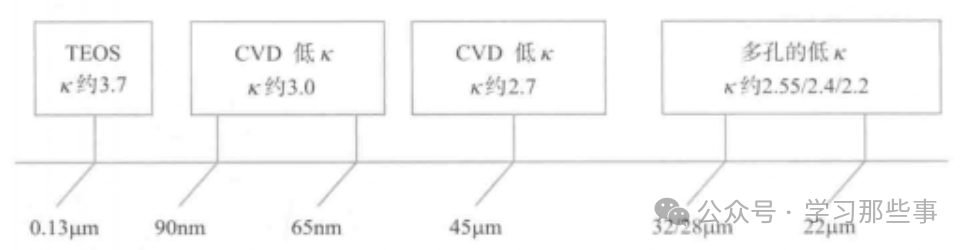

在铜互连技术体系里,互连层之间的电容模型呈现于图6。鉴于电容大小与介电常数成正相关关系,业界为减小互连层间电容,进而改善RC延迟,采用了介电常数(κ值)低于传统二氧化硅的low-k材料。图7展示了不同工艺节点下互连介质层的κ值变化情况。

图6:互连线寄生电容示意图

图7:不同工艺节点的k值

当下,low-k材料的制备方式主要涵盖三种:其一,在材料中掺入氟、碳、氢等强电负性元素,以此降低材料极性,进而减小材料的κ值,像氟硅酸盐玻璃(FSG)、掺碳氢氧化硅(SiCOH)等较为常见,它们在0.13um至45nm工艺中得到广泛应用;其二,借助多孔技术,降低材料的分子密度来实现κ值降低,例如多孔SiO₂、多孔SiCOH等;其三,运用气隙(airgap)技术,将超低κ值的空气隙嵌入互连介质层,这同样能显著降低介电常数。在32/28nm及以下工艺中,由于对降低RC延迟所需的κ值要求更低,故而常运用多孔和气隙技术来制备超low-k介质层 。

Cu/low-k互连的电迁移问题

伴随大规模集成电路持续发展,特征尺寸不断缩小,金属导线所通入的电流密度急剧上升。与此同时,芯片集成度提高,单位面积功耗增大,致使Cu/low-k互连结构中的电迁移问题,已成为影响集成电路可靠性的关键因素之一。在金属导线内,沿电场反方向运动的电子与金属离子发生动量交换,致使金属离子顺着电子流方向移动,这种现象被称作电迁移,它可能引发金属线开路或断路。尽管铜材料自身抗电迁移能力强于铝,但双大马士革工艺使得铜的电迁移问题变得复杂。其中,通孔工艺、阻挡层质量以及铜表面处理等诸多方面,均会对铜互连电迁移产生影响。

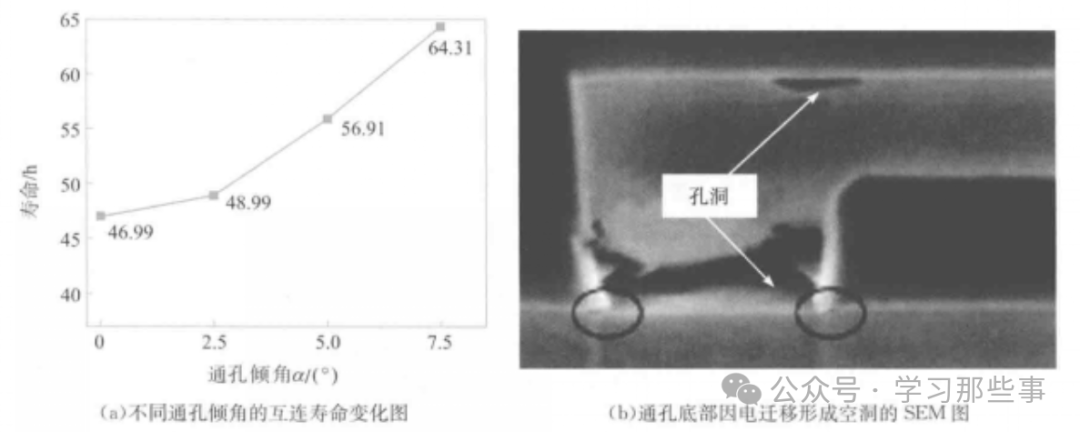

对于铜互连结构而言,通孔因深宽比高、台阶覆盖性欠佳、内部电流密度大以及应力集中等因素,相比沟槽互连线,更易出现电迁移失效情况。其中,通孔的倾斜角和通孔底部的形貌是两大主要影响因素。具有一定倾斜角度的通孔结构,相较于垂直结构,更便于后续阻挡层和金属铜的填充,能使台阶及侧壁覆盖性更佳,从而提升互连线的可靠性。图8(a)所示为不同通孔倾角下互连寿命的变化情况。通孔底部是整个通孔工艺中最为薄弱之处,也是最易失效的部位。通孔底部刻蚀形貌的均匀程度、阻挡层TaN是否实现完全反溅射,以及后续铜填充的形貌等,都会对电迁移产生重大影响。图8(b)展示的是通孔底部因电迁移形成的空洞。其中,阻挡层TaN的完全反溅射(re-sputter)是工艺难点。该过程通过轰击通孔底部的阻挡层TaN,使底部TaN溅射到侧壁上,以达到增加侧壁阻挡层厚度、减薄底部厚度的目的。由于阻挡层电阻率远大于铜,若反溅射不完全,会导致通孔底部接触电阻增大,电流流经此处时,因电阻不均匀致使局部电流密度不一致,进而产生空洞,引发电迁移失效。阻挡层肩负着阻止铜扩散,以及确保介质层与铜界面具备良好黏附性的双重职责。良好的黏附性能减缓沿铜阻挡层界面的铜扩散速度。

图8:不同通孔倾角的互连寿命变化图及电迁移所形成的空洞的SEM图

铜互连的另一个电迁移失效高发区域是铜的表面,因为沿表面的铜扩散速度快于沿晶粒间界的扩散速度。为解决这一问题,业界在铜CMP之后,会在铜线上沉积一层覆盖层。该覆盖层可有效阻止铜扩散,增强抗电迁移能力,且两者间黏附性越强,效果越显著。对铜表面进行处理是提升铜线与覆盖层黏附性的有效手段,一般采用H等离子体对铜表面进行处理,以此改善铜与覆盖层的黏附性。

-

芯片

+关注

关注

463文章

54463浏览量

469523 -

集成电路

+关注

关注

5464文章

12695浏览量

375777 -

工艺

+关注

关注

4文章

720浏览量

30398 -

互连

+关注

关注

0文章

26浏览量

10596

原文标题:Cu/low-k互连的电迁移问题

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Low-K材料在芯片中的作用

AL-CU互连导线侧壁孔洞形成机理及改进方法

直接互连结构在数据交换中的应用分析

Scratch Testing of Low-k Diele

什么是直接互连结构(direct interconnecti

直流和脉冲电镀Cu互连线的性能比较

电子封装微互连中的电迁移

可延展电子金属导线通用互连结构研究

高速BGA封装与PCB差分互连结构设计

一文了解晶圆级封装中的垂直互连结构

芯片越小,挑战越大:半导体电迁移如何决定芯片寿命?

Cu/low-k互连结构中的电迁移问题

Cu/low-k互连结构中的电迁移问题

评论