文章来源:老千和他的朋友们

原文作者:孙千

一个复杂的处理器可能包含数亿甚至数十(百)亿个晶体管,这些晶体管通过细金属线彼此互联。芯片的制造过程极其复杂,需要经历数百个精确控制的步骤。

1、FinFET

1999年,加州大学伯克利分校的胡正明(Chenming Hu)教授、Tsu-Jae King Liu教授以及Jeff Bokor教授共同研发了鳍式场效应晶体管(FinFET)技术,这项突破性创新为半导体技术注入了新活力。

Tsu-Jae King Liu教授形象地将FinFET比喻为“垂直晶体管,就像一座座摩天大楼”。相较于传统的金属氧化物半导体场效应晶体管(MOSFET),后者是以平坦、低矮的形式制造在硅晶圆表面,FinFET则通过沿晶圆表面刻蚀出狭窄的垂直鳍侧壁来制造。这种设计不仅优化了空间利用效率,还让每块芯片可容纳多达一万亿个晶体管。

FinFET技术最初被称为"DELTA(fully DEpleted Lean-channel TrAnsistor)"晶体管,后来才改名为FinFET。这项发明在2000年首次发表在IEEE电子设备会议(IEDM)上,论文题目为"《Sub 50-nm FinFET: PMOS》"。2011年,英特尔公司成为第一个将FinFET技术商业化的公司,在其22纳米制程中使用了这项技术,称之为"3D晶体管"。

FinFET的独特之处在于其能够将栅极长度(即源极与漏极之间的距离)缩小至不足10纳米。栅极长度的减小,不仅使晶体管整体尺寸进一步微型化,还能以更高的电流密度实现快速切换。

值得一提的是,在五纳米工艺节点中,FinFET的设计已经被证明是切实可行的,且不需要对制造工艺进行大幅调整。然而,Tsu-Jae King Liu教授坦言:“当栅极长度缩小至五纳米以下时,可能会面临量子力学隧穿效应和其他限制效应。这意味着,在制造中哪怕是微小的变化,也可能对晶体管性能造成显著影响。”

通过其独特的三维结构,FinFET有效解决了平面FET因短沟道效应而导致的可扩展性瓶颈(参见图1)。这不仅延续了摩尔定律的生命力,也为未来更高性能、更小尺寸的半导体器件铺平了道路。

图

1 传统平面场效应晶体管(Planar FET)和鳍式场效应晶体管(FinFET)的结构对比。主要区别在于FinFET采用了垂直的鳍状结构,而Planar FET则是平面结构。

Planar FET → 平面场效应晶体管 FinFET → 鳍式场效应晶体管

Gate → 栅极 Drain → 漏极Source → 源极 Oxide → 氧化层 Silicon substrate → 硅衬底

2、集成电路的设计

集成电路(IC)的发明可以追溯到1958年,由杰克·基尔比首次提出。这一革命性技术催生了多种类型的集成电路,使现代电子设备的普及成为可能。例如,微处理器是一种逻辑芯片,主要用于计算任务,如运行二进制代码、逻辑门操作和布尔代数计算。

存储芯片则用于存储数据,其中最常见的是NAND(非与门)存储器。此外,模拟芯片可以在连续信号范围内运行,可进一步细分为线性IC和射频IC,用于不同的信号处理功能。而数字信号处理器(DSP)则负责在模拟信号和数字信号之间进行转换。特定应用集成电路(ASIC)则是根据特定需求定制的芯片,广泛应用于汽车电子、电视、数码相机以及各种家用电器领域。

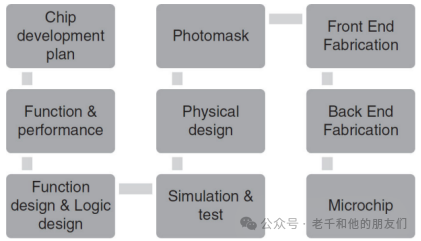

集成电路的设计和功能取决于多个关键因素,如用途、功耗、芯片面积、成本以及上市时间。在开发过程中,这些因素需要被充分考虑,并决定芯片设计的逻辑电路结构。在逻辑设计阶段,首先需要绘制逻辑电路图,用以定义实现目标功能所需的特定电子电路。一旦电路图完成,工程师会对其进行多次模拟,通过测试来验证电路的运行是否符合设计要求。

图2 集成电路设计与制造

3、集成电路的制造过程

一个复杂的处理器可能包含数亿甚至数十(百)亿个晶体管,这些晶体管通过细金属线彼此互联。芯片的制造过程极其复杂,需要经历数百个精确控制的步骤。

集成电路的基材是硅,这种材料由于其独特的分子结构被称为半导体。硅能够在特定条件下导电,而在其他条件下则表现为绝缘体。这一特性使其成为晶体管的核心构件,通过栅极控制电流通过与否,从而实现“开/关”或二进制的1/0功能。

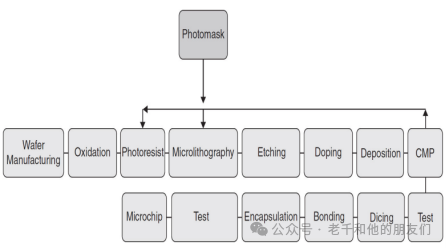

制造集成电路的过程可以划分为三个主要阶段:(1)晶圆制造;(2)前端工艺处理;(3)后端工艺处理。在前端工艺处理中,经过数百次重复操作后,集成电路结构最终在晶圆上形成(见图3)。

图3 晶圆制造、光罩、前道工艺和后道工艺

IC的生产高度依赖先进的制造技术,包括材料处理自动化、计算机集成制造、先进工艺控制以及制造执行系统等。制造过程中,晶圆作为IC结构的基底,经过复杂的工序,如氧化、光刻、刻蚀、掺杂以及各种材料的沉积。每一阶段还需进行严格的检测和测试。最终,芯片被切割、封装、测试,进入可供使用的状态。

3.1 晶圆制造

晶圆,也称为晶片或基板,是一种由硅或其他半导体材料(如砷化镓)制成的薄圆片,其厚度约与信用卡相当。硅,是地球上仅次于氧的第二丰富元素,广泛存在于沙子中。在用于半导体制造之前,硅必须被提纯至接近100%的纯度。

半导体制造的起点是硅锭的生长。硅锭一般通过两种方法制造:直拉法(Czochralski,CZ)和区熔法。由于区熔法受限于生长过程中表面张力的影响,其晶圆直径通常不超过150毫米。相比之下,大多数硅锭更常见于通过直拉法生长。

在直拉法中,以一块称为“种子”的硅晶体为起点,将其放入几乎100%纯的熔融硅中。种子和容器以相反方向旋转,同时在氩气环境下,将纯化硅加热至约1200°C。随后,将种子从熔融硅中缓慢拉出,硅原子逐渐附着在种子上,最终形成一根长晶体棒,称为硅锭。在对温度、气体环境和压力的严格控制下,硅锭的直径通常达到200毫米或300毫米。通过此工艺,生产出电子级硅,其纯度高达99.9999999%,完全符合半导体制造的质量标准。

晶圆制造工艺是通过一系列操作用于将硅锭加工成硅晶圆。

裁切、研磨、切片:单晶硅锭的两端使用单刃金刚石锯片和水冷却液进行裁切。随后,硅锭被研磨至均匀直径,并对两端进行倒角处理,以减少硅锭破裂的可能性。通过X射线衍射确定晶体结构。通过湿式研磨在硅锭上制作一个纵向平面,用于指示硅锭的晶体方向。硅锭被切割成圆片,也称为基板。

研磨:切片后,晶圆在压力下进行机械研磨,以实现平整度和平行度。研磨操作会去除切片过程中损坏的表面硅,并将晶圆研磨至所需厚度。通过使用湿式自动研磨机对单个晶圆的边缘进行倒圆处理。

腐蚀:切片和研磨会破坏硅表面的晶体结构,因此需要用含有硝酸、醋酸或氢氟酸的溶液对晶圆进行腐蚀,以去除受损的外表面并减少晶圆厚度。腐蚀操作可以在手动腐蚀槽或自动腐蚀机中完成。

抛光:腐蚀后,晶圆被抛光至超平整、无瑕疵且镜面光滑的表面,表面粗糙度仅在原子级别。抛光过程通常分为两到三步完成。晶圆被安装在一个金属载体板上,通过真空固定在抛光机上。抛光过程结合了机械压力和化学作用,使用如氧化铝(Al2O3)、二氧化硅(SiO2)或氧化铈(CeO2)等精细抛光浆料。

清洗:最后,晶圆被清洗以去除抛光后表面的任何颗粒,从而使晶圆无残留。清洗过程中可使用多种超纯化学品,包括氨水、过氧化氢、氢氟酸、盐酸和去离子水。

3.2 前端工艺(FEOL)

在晶圆上构建电路是一个极其复杂且精确的过程。该过程包括数百个精确控制的步骤,可能包含多达30层复杂电路。芯片的制造需要10到30天甚至更长时间,按照特定的模式和工艺配方在每片300毫米晶圆上生产数百或数千个芯片。

制造集成电路芯片的过程称为“制造工艺”。制造芯片的工厂被称为“制造厂”或“晶圆厂”。在晶圆厂中,有洁净室用于批量制造晶圆。由于灰尘颗粒会破坏芯片上的复杂电路,洁净室内的空气被不断净化和循环。在ISO 1级洁净室中,每立方米空气中含有的颗粒数不超过10个,颗粒直径为0.1微米(百万分之一米)。晶圆厂的技术人员穿着特制的“兔子服”,以防止污染物在制造过程中接触到晶圆。

以下是前端工艺(FEOL)中的操作步骤:

外延生长

外延生长是制造半导体器件的基本工艺之一。外延生长是指在基底晶体(衬底)上有序地沉积一层晶体(外延薄膜)。要求外延薄膜相对于衬底具有特定的取向。外延薄膜和衬底可以是相同或不同的材料。外延生长分为三种类型:液相外延、气相外延和分子束外延。

氧化

二氧化硅(SiO2)作为一种电绝缘体,是集成电路的重要组成部分。氧化层的生长可以通过干法氧化或湿法氧化实现。氧化是一个扩散过程。首先将硅晶圆加热,并在扩散炉中暴露于超纯氧气的高温环境下。在炉内通过精确控制条件,从SiO2/硅界面生长出均匀厚度的二氧化硅薄膜(干法氧化)。

Si + O2 → SiO2

湿法氧化相较于干法氧化更适合快速生长较厚的氧化层。湿法氧化通过将晶圆暴露于超高纯水蒸气中,或通过燃烧氢气和氧气形成超高纯水蒸气,在氧化炉中进行。

Si + 2H2O → SiO2 + 2H2

光刻

光刻是将特定的集成电路设计图案印刻到晶圆上的过程。在进行光刻工艺之前,需要准备光掩模(掩模板)。光掩模上绘制了电路图案的副本,以不透明图案的形式呈现在石英板上。石英板首先经过高精度抛光,然后在石英基板上通过溅射涂覆一层对紫外线波长不透明的铬材料。随后,将一种称为光刻胶的光敏化学物质旋涂在铬光掩模坯料上。然后通过电子束光刻将电路设计图案转录到铬膜上。曝光、显影和蚀刻后,光掩模坯料成为具有电路图案副本的光掩模。

光刻胶涂覆:晶圆被涂覆上一种对光敏感的液体,称为光刻胶。通过将少量光刻胶倒在晶圆中心,同时让晶圆高速旋转,材料会均匀地覆盖整个表面,形成一层薄而均匀的涂层。光刻胶对“光”敏感,并且“抗拒”某些用于去除光刻胶下方材料的化学物质。

光掩模与曝光:光刻机精确对准涂覆光刻胶的晶圆与光掩模。光掩模作为模板,包含要成像到晶圆上的图案。光刻机通过光掩模和光学缩小镜头将光投射到晶圆上。这使得光刻胶在未被掩模保护的区域受到光的曝光。对于正性光刻胶,曝光区域发生化学反应,使光刻胶在碱性溶液(显影剂)中可溶解。负性光刻胶在曝光区域变得不溶解。曝光工具在晶圆上重复该过程,以在整个晶圆上形成相同的图像。光刻室内需要使用黄色照明,以防止光刻胶受到人工光线的意外曝光。

光刻胶显影与硬烤:曝光后,晶圆使用氢氧化钠或氢氧化钾的水溶液进行显影。显影剂通过浸泡、喷涂或雾化的方式施加,溶解并去除光刻胶的曝光区域。这会留下与光掩模上图案相似的光刻胶图案。显影后,还需进行额外的烘烤工艺,称为“硬烤”,以硬化剩余的光刻胶。此时,光刻胶可以保护下层材料免受蚀刻过程的影响。

蚀刻

蚀刻工艺根据掩模图案去除硅、二氧化硅、多晶硅或金属层。蚀刻可以通过化学溶液(湿法蚀刻)或等离子体(干法蚀刻、反应离子蚀刻)完成。

湿法蚀刻:湿法蚀刻是一种简单的技术。通过将晶圆浸入化学浴中完成。湿法蚀刻通常是各向同性的,蚀刻在所有方向上均匀进行,这会导致掩模层的下切深度与目标区域相同。因此,选择性是一个重要的考虑因素。选择性是指两种蚀刻速率的比率:目标层的蚀刻速率与掩模层的保护速率。

干法蚀刻:干法蚀刻是半导体制造中最常用的工艺之一。干法蚀刻可能是各向异性的(方向依赖性),通过使用化学反应性气体或氩原子的物理轰击,有效地蚀刻目标表面或层。

反应离子蚀刻(RIE)是一种结合化学和物理蚀刻的干法蚀刻技术。晶圆被放置在真空腔反应器中。通过向含有化学反应性元素蚀刻剂(如氟基或氯基气体)的气体施加射频能量,等离子体释放出带正电的离子。这些离子垂直撞击或轰击晶圆表面,蚀刻或去除材料,随后通过真空系统移除。

蚀刻完成后,光刻胶已完成其作用,可以通过氧等离子体从蚀刻后的晶圆上去除。

掺杂

本征半导体(如硅)可以通过掺杂外来原子来提高其导电性。掺杂可以通过离子注入或扩散来实现。

离子注入用于掺杂本征半导体的材料通常是硅的离子化原子或分子,硅具有4价电子,而掺杂材料通常具有3或5价电子,如硼或磷。掺杂剂在强电场中被加速到从亚keV到多个meV的能量范围,并轰击晶圆表面,未被掩膜或蚀刻工艺暴露的区域。掺杂剂撞击晶圆后,会嵌入晶体材料的不同深度和精确位置,从而改变材料的主要载流子浓度为p型(空穴)或n型(电子)。离子注入会对晶体基板造成损伤,因此需要进行高温退火步骤(800至1200°C,持续数秒至30分钟),以恢复晶体结构并进一步将掺杂原子整合到晶格中。

扩散是指通过炉子将掺杂剂引入、定位和/或激活到半导体中的过程。掺杂剂可以是气态、液态或固态形式。气态掺杂剂最为常用,包括砷烷(AsH3)、硼烷(BH3)、磷烷(PH3)等。掺杂剂在半导体中由于浓度梯度而移动。菲克扩散定律是描述掺杂剂扩散性、浓度、温度和时间如何决定硅中掺杂剂分布的方程。掺杂剂的扩散限制了更先进集成电路(IC)集成的热预算和处理温度。

沉积

薄膜沉积工艺将硅氮化物、二氧化硅、硅或金属等薄而均匀的材料沉积到晶圆上。硅层形成绝缘体,金属层用于电路布线。一些常用的薄膜沉积方法包括物理气相沉积(PVD)、化学气相沉积(CVD)或电化学沉积(ECD)。

物理气相沉积(PVD)是一种溅射法,在高真空室中进行。源材料(溅射靶材)和晶圆基板连接到高压电源。当溅射气体(如惰性气体氩气)进入腔室时,氩气被电离,并在溅射靶材和晶圆之间形成等离子体。氩离子被加速并轰击溅射靶材,从而撞击靶材并击出原子或分子。这些原子或分子穿过真空到达晶圆表面,形成所需的薄膜。

蒸发是另一种PVD工艺。首先,将晶圆放置在真空腔中,利用真空泵清除腔内气体。当腔室内没有残余气体后,加热源材料(金属)使其蒸发。蒸发的分子分散并沉积在晶圆上,形成所需的薄膜。

化学气相沉积(CVD)是一种化学工艺,可以在真空环境(低压CVD或LPCVD)中完成,以生产高质量、高性能、大面积的薄膜。CVD通常用于在沟槽墙壁和底部提供高度一致的薄膜涂层,尤其是在这些特征尺寸不断缩小时。反应气体或前驱体被引入含有晶圆的反应腔中。在热壁反应器或等离子环境中,反应物种在反应器壁或等离子体中生成,然后扩散到晶圆表面,在那里进行薄膜生长。这被称为均相过程,因为反应物种在气相中形成。在冷壁反应器中,反应能量通过加热晶圆提供,反应物种通过与晶圆表面的相互作用生成——这是一个异相过程。

原子层沉积(ALD)是CVD的一种特殊形式,在严格控制的工艺中每次沉积一层薄膜。

电化学沉积(ECD)用于沉积薄金属层,这些金属层将形成集成电路中连接各种器件的互连(集成导线)。ECD是一种电镀工艺。基板浸没在电解液中,并作为阴极(电源的负极)。铜电极作为阳极(电源的正极)通过电解液形成电路。铜离子在阴极或基板上被还原并形成薄膜。

化学机械平坦化

集成电路(IC)加工需要平坦的表面,例如光刻操作。有几种方法可以进行平坦化。化学机械平坦化(CMP)通过应用含有磨料的化学浆料和机械力(抛光垫)是最好的平坦化技术之一,能够去除之前工艺中多余的材料,并平坦化不平整的表面以创建平坦表面。深度要求可达到埃级别。

重复步骤

制造集成电路通常需要超过350个工艺步骤。通过光刻、蚀刻、掺杂、沉积、CMP等步骤逐层重复,直到最后一层形成。包含晶体管和互连的晶圆被转移到

3.3 后端工艺阶段

后端工艺(BEOL)从测试包含晶体管和互连的晶圆开始。自动化计算机驱动的电气测试系统会检查晶圆上每个芯片的功能性。未通过测试的芯片会被标记为废品。随后,晶圆被切割成单个芯片。单个芯片会通过引线键合组装、测试,最后封装。

研磨(减薄)和切割

晶圆首先通过保护胶带(称为背面研磨胶带)附着,以保护晶圆的器件层。晶圆被翻转,晶圆背面被研磨(减薄)至适合组装和封装的厚度。

切割或分离是将半导体晶圆切割成单个芯片的过程。在减薄后,晶圆被安装在带有器件面朝上的切割胶带框架上。带有金刚石颗粒的圆盘刀片将晶圆切割成单独的芯片。切割过程可以通过金刚石刀片、激光烧蚀或隐形切割完成。

引线键合

引线键合是将IC连接到基板的工艺。引线键合使用非常细的金线或铜线,通过超声波或热超声技术将芯片连接到基板或引线框架。球焊是最常用的互连方法。球焊的形成从芯片上的焊点开始,经过线圈,最终连接到基板上的焊点。引线键合机是一种全自动化设备,配备高速高精度伺服系统、用于键合操作的超声换能器以及用于设备对齐的自动视觉系统。

封装与组装

IC封装或封装是将半导体材料封装在支撑壳体或封装中的过程,封装材料主要是模塑树脂。封装的目的是通过保护IC免受恶劣环境的影响、处理热管理并为基板提供可靠的互连来支持IC性能。基板通常是印刷电路板(PCB),它结合了多个IC和无源元件以构建微电子系统。有单芯片封装,也有多芯片封装(称为MCM,多芯片模块)或系统封装(SiP)。在封装之后,会通过激光在封装表面或芯片背面打印或雕刻产品信息。大多数封装通过焊接或粘合到基板上。

3.4 最终测试

封装完成后的IC芯片看似已准备好投入使用,但在实际应用前仍需克服诸多潜在问题。例如,芯片在组装过程中可能出现破裂,引线键合可能存在连接不良,亦或因静电放电处理不当而受损等。因此,必须对每片IC芯片进行单独测试。

测试过程中,芯片会被置于测试仪上,按照预先为每种IC类型专门制定的测试程序进行严格检测。这些测试涵盖功能性、性能以及功耗等方面,旨在确保芯片达到设计规范的要求。此外,在许多情况下,这些测试程序与早前晶圆测试中所使用的程序为经过改进的版本,以更全面地验证芯片的可靠性。

-

处理器

+关注

关注

68文章

20339浏览量

255352 -

集成电路

+关注

关注

5465文章

12695浏览量

375855 -

半导体

+关注

关注

339文章

31279浏览量

266787 -

晶体管

+关注

关注

78文章

10443浏览量

148705 -

芯片制造

+关注

关注

11文章

736浏览量

30539 -

FinFET

+关注

关注

12文章

262浏览量

92375

原文标题:半导体入门:FinFET与芯片制造工艺

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

集成电路制造技术的应用

集成电路设计基础.ppt(山东大学教程)

集成电路设计分工

CMOS集成电路制造工艺的详细资料说明

国产EDA“夹缝”生存 集成电路设计和制造流程

集成电路设计与制造过程

集成电路设计与制造过程

评论