【编者按】

IEEE国际电子器件会议 (IEDM) 是全球领先的微电子器件制造和材料技术论坛,展现最前沿的半导体和电子器件技术、设计、制造、物理材料领域的技术突破。IEDM会议议题涉及纳米级CMOS晶体管技术、先进存储、显示、传感、MEMS、新型量子和纳米级器件、光电子、能量采集器件、高速器件以及工艺技术和设备建模和仿真等领域。

2024 IEDM会议的焦点主要有三个:逻辑器件的先进工艺技术包括TSMC N2节点、CFET技术突破、三星2D材料、英特尔硅沟道扩展技术;存储技术包括存算一体、Meta 3D堆叠内存实现;先进封装技术包括英特尔EMIB-T 2.5D技术和台积电SoIC 3D混合键合技术。

本文编译自SemiAnalysis对IEDM 2024会议的总结,分为三部分连载,欢迎感兴趣的朋友关注和分享。

【内容目录】

1.TSMC N2

2.CFET

3.Memory

4.Meta 3D Stacked Memory

5.Intel EMIB-T

6.TSMC SoIC

7.Nvidia System Co-Optimization Of GPUs

8.2D Materials

9.Intel 6nm Gate Length

10.Expert Panel: Breakthroughs Needed

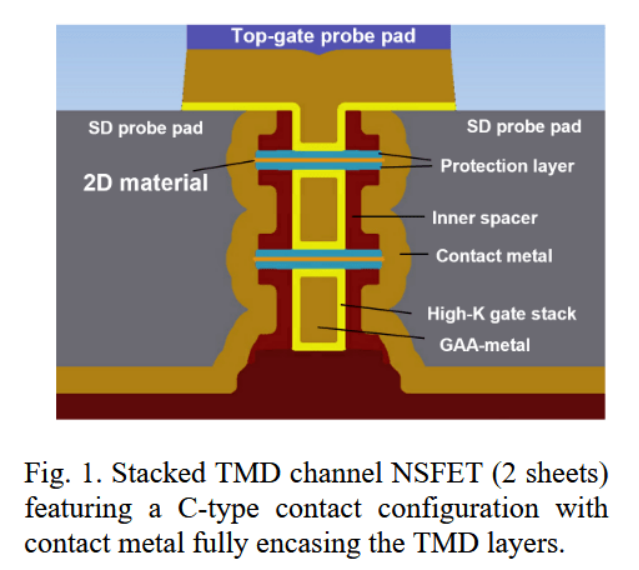

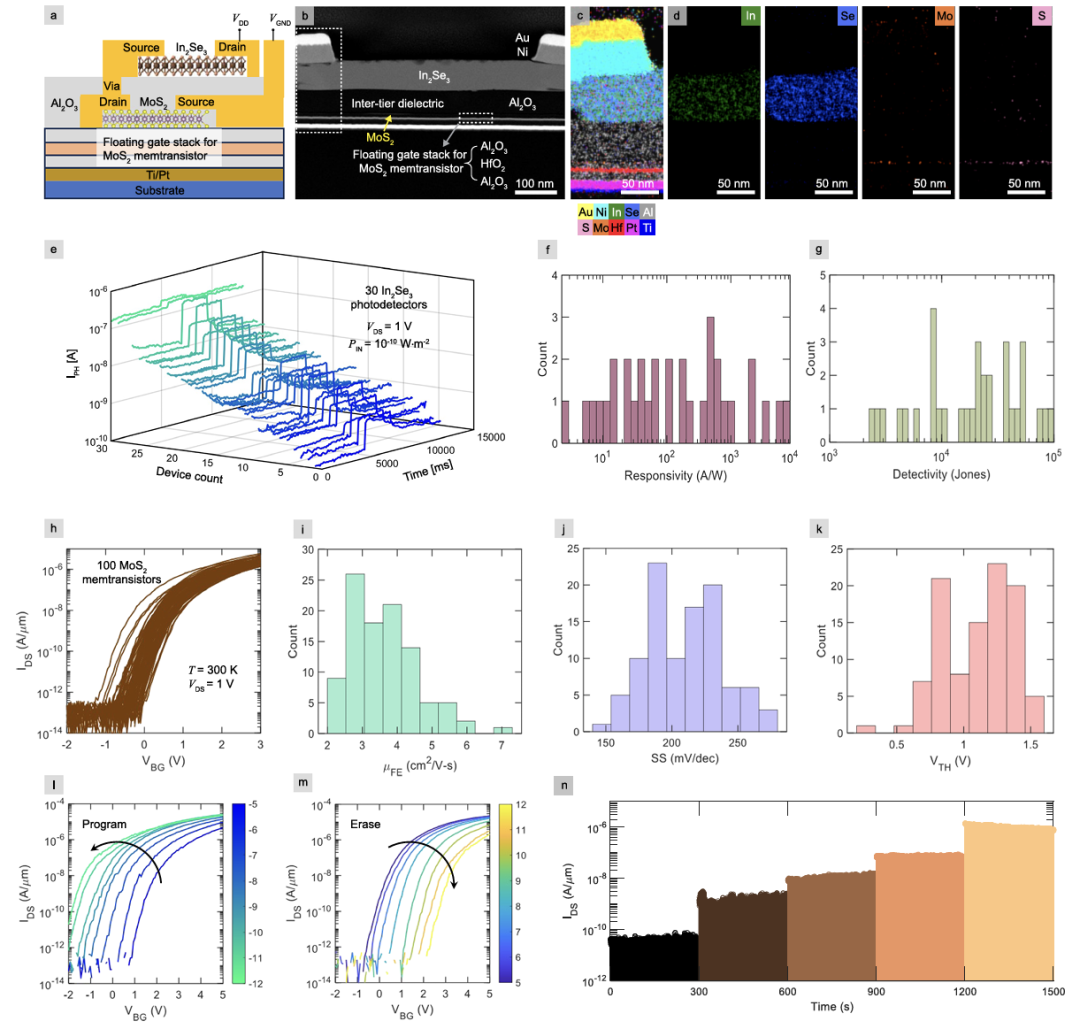

2D材料有望替代硅基晶体管沟道,沟道负责在晶体管源极和漏极之间传导电流,其导电性由接触或环绕沟道的栅极控制。在硅基器件中,当沟道长度(通常称为栅极长度或Lg)缩小至约10纳米以下时,由于漏电流过高会导致晶体管效率低下且难以关断,因此被认为不具备实用价值。而2D材料构成的沟道具有更优的操控性,且不易产生硅基器件常见的漏电流机制。鉴于尖端器件的栅极长度已进入10-20纳米区间,2D材料已被纳入2030年代多个技术路线图,但目前距商业化应用仍有距离。英特尔的一篇论文将主要挑战归纳为三类:

1. 材料生长

2. 掺杂与接触成型

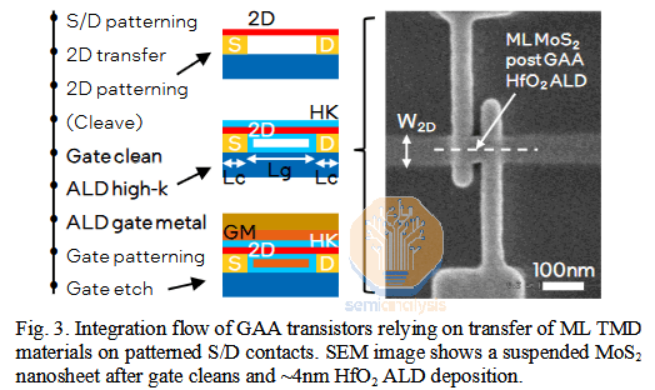

3. 全环绕栅极(GAA)堆叠/高K金属栅极集成

其中掺杂与接触成型涉及在晶体管有源区形成源漏极的掺杂工艺,以及构建与上层金属互连的低阻接触。GAA堆叠则需要在2D沟道周围沉积多层材料以形成晶体管控制栅极。继去年实现2D沟道材料集成(N型器件采用MoS₂,P型器件采用WSe₂)后,在掺杂、接触和栅极成型方面取得进展:

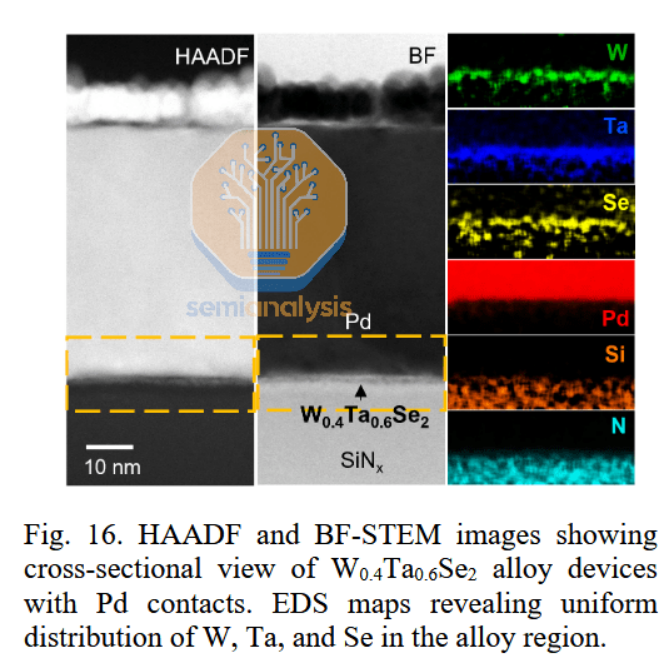

台积电成功演示了P型器件接触工艺,该突破填补了关键技术空白,此前仅有N型晶体管接触工艺得到验证。接触结构负责建立金属互连层与晶体管源极、漏极或栅极的电气连接,其核心性能指标在于接触电阻,这对数十纳米尺度的现代器件尤为关键。技术难点源于源漏极由半导体材料(本例中为WSe₂)构成,本征电阻较高。若直接将互连金属沉积在源漏极表面,界面处会形成高阻态肖特基势垒,且金属与硅的粘附性通常较差。

硅基器件的常规解决方案是硅化工艺:通过沉积与退火在硅源漏区表面形成高导电性硅化物(如NiSi),再于硅化物上构建金属互连,实现从有源区到电路互连的低阻连接。由于不含硅元素,传统硅化工艺无法适用与2D材料。优选方案是采用退化掺杂——向2D材料晶格引入特定杂质,使其从半导体态转变为导体态。但WSe₂的掺杂工艺面临严峻挑战,晶格结构易遭破坏,且难以实现掺杂剂均匀分布。台积电在大会上的展示表明,他们的研究团队已经成功攻克了这一难题,2D材料接触方案的突破取得了重大进展。

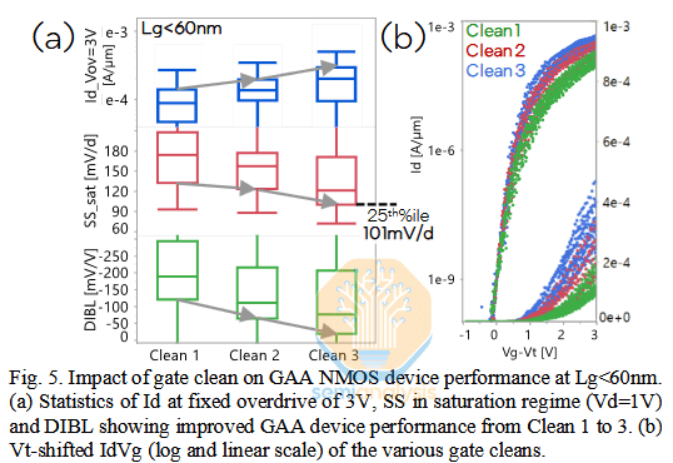

栅极氧化物质量是2D材料商业化的另一关键挑战。如台积电N2工艺论文所述,栅极氧化物质量直接决定晶体管控制能力。若无法实现有效控制,逻辑制程将失去可行性。英特尔展示了高质量栅极氧化物的制备工艺,成功制造出具有优异控制特性的晶体管器件。其DIBL(漏致势垒降低)和亚阈值摆幅(SS)指标表现优异(分别对应低漏电流和陡峭的开关特性),同时具备高饱和漏电流,充分证明其静电控制能力。该突破主要源于工艺优化,特别是预清洗与氧化物沉积环节的改进。

尽管在掺杂、接触和栅极成型方面取得突破,2D材料生长技术仍进展缓慢。我们在去年综述中指出:“生长工艺是2D材料的根本性难题。”目前多数研究采用转移技术:先在蓝宝石衬底上生长材料,再机械转移至硅晶圆。这种实验室手段难以满足量产需求,直接在12英寸硅晶圆上进行外延生长才是最具商业化潜力的技术路径。

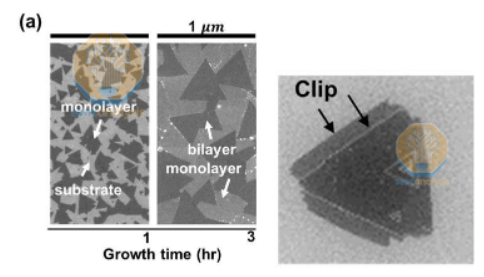

该领域最新进展陷入停滞。三星曾在8英寸测试平台上演示晶圆级生长,但材料附着性欠佳。其解决方案是在各晶体边缘制作“固定夹”以承受后续工艺应力,成功制备出功能性晶体管(采用顶/底栅结构而非GAA架构)。然而该工艺不具备可扩展性:演示器件的沟道长度达500纳米(超出需求两个数量级),且固定夹结构会抵消短沟道带来的尺寸优势。真正需要突破的是无需辅助结构即可在整片晶圆上生长高质量材料。

台积电展示了完整二维FET反相器——将N型与P型晶体管连接构成基础逻辑单元。该研究侧重集成探索,器件采用平面结构而非GAA架构,且尺寸较需求大1-2个数量级。实验发现若干重要现象:

首先尝试采用WSe₂制备同质N/P型晶体管。主流方案采用异质集成(NMOS使用MoS₂沟道),若能用单一材料实现双极器件将显著降低成本。但台积电发现WSe₂ NFET性能严重劣于PFET,无法匹配应用需求。

其次,标准湿法工艺会影响既有PFET性能。在PFET有源区进行图形化时采用常规湿法工艺(光刻胶、蚀刻等)——这些本应对底层器件无影响的成熟工艺,却导致阈值电压(晶体管开启电压)显著偏移。这种非直观现象预示:随着2D材料集成复杂度提升,可能涌现更多意外挑战。

二维FET的阈值电压易受标准湿法工艺影响。

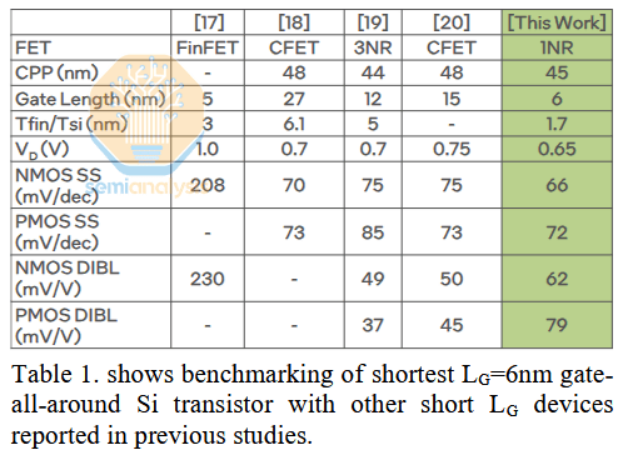

实现量产仍需长期努力。当前尖端技术仅能在较短沟道下制备单个优质晶体管,距离单晶圆集成数十亿晶体管、年产能十万片以上的目标相差约15个数量级。更糟糕的是,硅基器件理论最小栅长10纳米的传统认知已被打破。英特尔成功演示单纳米带GAA晶体管,栅长仅6纳米。

传统认为10纳米以下将面临量子隧穿等根本性障碍:在极端尺度下,载流子穿越栅极势垒的概率不可忽略,导致漏电流激增。漏电严重的晶体管将造成芯片能效低下与可靠性问题。但英特尔的实验证明量子隧穿效应可被有效抑制,虽然器件性能尚未完美,但已展现足够优化空间——亚阈值摆幅接近室温理论极限60 mV/dec,DIBL指标约为台积电N2工艺的两倍,虽需改进但已属研发突破。

需注意:此前5纳米栅长FinFET器件性能极差(DIBL与SS值过高),而本次6纳米GAA器件性能显著提升。

英特尔的突破可能延后2D材料的路线图定位。若无技术必要性,芯片制造商不会轻易转向复杂的新材料体系。

尽管计算设备持续进步,但现有发展模式不可持续。若无底层器件革新,计算需求与能耗的指数增长将难以为继。斯坦福大学Tom Lee教授推演显示:按当前增速,2050年AI计算能耗将超过地球接收的太阳光子总量,百年后更需捕获太阳全部辐射能量——这凸显技术变革的紧迫性。IEDM专家小组强调:半导体器件需要革命性突破,而非寄望于戴森球等科幻方案。论坛闭幕时,学界发出行动倡议:器件技术的渐进式改良已不足够。Lee教授指出,在各类“AI指数”中,能源终将成为关键制约因素。“我们无法用线性武器战胜指数级敌人。”

-

工艺

+关注

关注

4文章

720浏览量

30391 -

2D

+关注

关注

0文章

67浏览量

15959

原文标题:IEDM 2024先进工艺焦点(三):2D材料技术的进展与挑战

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

CoWoS(Chip-on-Wafer-on-Substrate)先进封装工艺的材料全景图及国产替代进展

从“不可能三角”到原子级沉积:安德科铭李建恒解读先进制程下薄膜材料的突围之路

TechWiz LCD 2D:液晶透镜模拟

多芯光缆技术进展与挑战

从3D堆叠到二维材料:2026年芯片技术全面突破物理极限

英特尔半导体制造技术突破:2D 材料晶体管、新型电容器、12吋硅基氮化镓

浅谈2D封装,2.5D封装,3D封装各有什么区别?

X-ray设备2D/3D检测金属材料及零部件裂纹异物的缺陷

IEDM 2024先进工艺探讨(三):2D材料技术的进展及所遇挑战

IEDM 2024先进工艺探讨(三):2D材料技术的进展及所遇挑战

评论