人工智能、自动驾驶汽车等技术正迅速发展,市场对定制可扩展处理器的需求也随之不断攀升。RISC-V开放标准指令集架构(ISA)以其模块化设计和协作社区,引领了处理器设计新潮流,助力实现技术愿景。相应的,机器组件、URL、HTML和HTTP互联网协议等基础构件的标准也正随着技术创新而加速发展。标准RISC-V ISA使开发者能够创建高效的处理器,同时节省软件开发时间,从而加快上市步伐。

标准架构通过通用规范实现定制设计,但对于特定应用,可能还需要在标准之外进行额外的定制。RISC-V社区认识到这一需求,并评估了许多此类定制任务,以便重新纳入标准。结合RISC-V定义的矢量扩展(RVV)与定制DSP指令来开发处理器IP,有望为需要信号处理功能的低功耗嵌入式应用带来显著优势。对于特别注重权衡功耗、性能和面积的微控制器(MCU)来说更是如此。

微控制器的演变

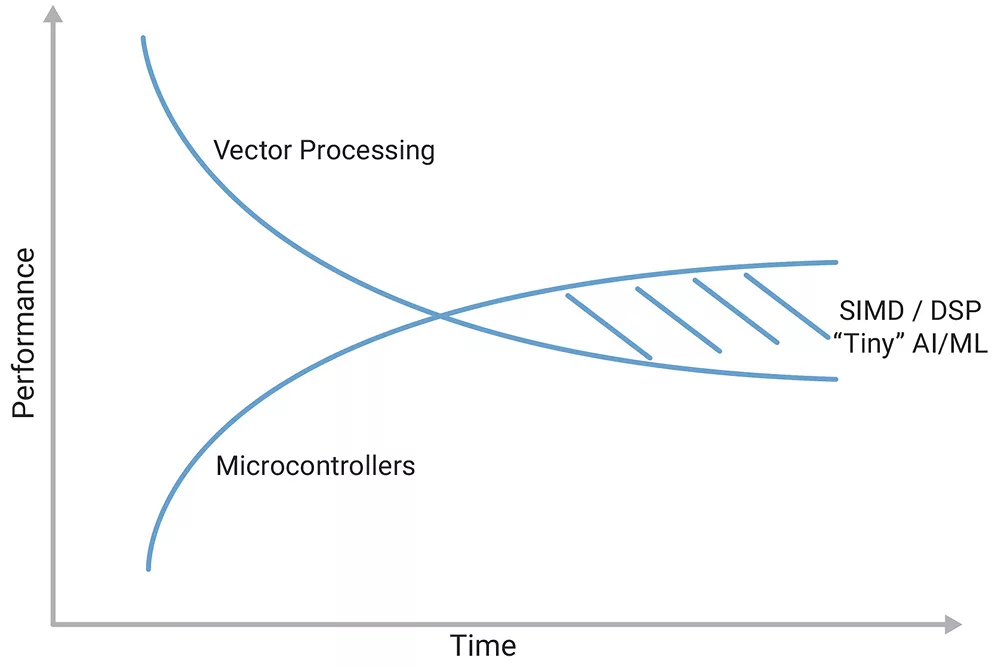

在过去几十年里,MCU已经从简单的嵌入式系统发展成为复杂的互联设备。上世纪90年代末,模数转换器(ADC)、计时器和UART逐渐集成到单个芯片上,MCU的性能和能效得到了显著提升。在2010年代,MCU将Wi-Fi、蓝牙和Zigbee等无线连接技术以及安全模块集成到硬件中,推动了物联网热潮。供应商现在提供通用CPU的DSP增强版本,可在现场进行编程。图1为矢量处理的融合进程。矢量处理渐渐从用于超级计算机演变为集成到MCU中,能够高效执行控制导向型任务。

▲图1 结合通用功能与SIMD/DSP功能的微控制器的演变过程

矢量处理器设计用于处理一维数组,其中包括单指令、多数据(SIMD)。应用处理器中常见的SIMD扩展包括英特尔的MMX、SSE和AVX、Arm的Neon和摩托罗拉-飞思卡尔的Altivec for PowerPC。这种通用+SIMD/DSP混合架构也扩展到MCU领域。

相比于同时执行不同计算的并发工作负载,SIMD针对不同的数据同时执行完全一样的指令。常见的例子包括调整数字图像的对比度或数字音频的音量。基本架构包括一个单独的标量寄存器文件(整数和/或浮点数)和一个矢量寄存器文件。通常,矢量内的SIMD最小元素宽度为8位。因此,64位矢量寄存器可以提供各种可编程选项:1x64位、2x32位、8x8位和4x16位。这种灵活性使开发者能够根据应用情况,以最小的字宽选择所需的精度水平。

最近,MCU集成或应用了越来越多的先进数据技术,例如SIMD指令和AI/ML矢量化操作,为神经网络提供支持。在这些情况下,单个MCU负责传感器数据的前端数字信号处理,例如过滤和传感器融合,同时其后端可以运行AI/ML模型来支持语音触发、对象检测和其他低功耗AIoT应用。例如,新思科技ARC EMxD处理器结合了高效的DSP和AI/ML处理,可降低功耗、简化设计、复用软件并节省系统成本。

MCU是第一类采用RISC-V的处理器,对RISC-V在汽车和消费市场中的增长起到了关键的推动作用。MCU大大受益于RISC-V的模块化和简单设计,可以在成本敏感、低功耗且多样化的嵌入式应用中实现更高的效率和灵活性。

RISC-V和开放标准模型的兴起

RISC-V开放指令集架构(ISA)为全球围绕开源软硬件开发而展开的密切合作指明了加速技术进步的方向。与可免费获取实际代码的“开源”软件不同,RISC-V是一个开放的规范,社区可以参与讨论并为规范的更新做出贡献。

RISC-V处理器的核心优势包括一系列设计属性,有助于实现处理器设计可配置性、可扩展性和软件兼容性,形成了一个丰富的生态系统。

RISC-V生态系统目前有4300多名成员,涉及物理硬件、IP、片上系统(SoC)、开发板、从工具链到操作系统的完整软件堆栈、工具供应商、调试供应商、仿真器和模拟器、验证服务和教育材料等领域。目前市场上的RISC-V内核数量超过100亿,全球有数万到数十万的开发者正在从事RISC-V相关工作。

RISC-V矢量规范为微控制器带来的矢量处理优势

RISC-V矢量规范版本1.0(RVV 1.0)是经批准对RISC-V ISA进行的矢量处理扩展。矢量处理通过并行处理来提高性能。常见的处理类型包括图像和音频信号处理、渲染图形、动画和游戏物理、数据压缩和加密(如加密操作)以及用于推理、特征提取和数据预处理等任务的边缘机器学习。

RVV 1.0将高效的控制面与高性能的数据平面相结合,在设计时充分考虑了软件开发的需求。其可调矢量长度范围从32位到2048位不等,开发者可根据具体性能要求动态配置其设计。此外,开发者可以利用RVV的内置效率和性能增强功能(如矢量链式操作)来进一步改进设计。应用软件开发者可以编写与矢量长度无关的代码,而不用管硬件的实际矢量长度,从而充分实现软件复用。RVV的简化设计侧重于优化代码大小,而非内存利用率。例如,每个矢量都使用由矢量长度定义的相同数量的元素,无论这些元素是否全部被使用。这种方法可以减少执行代码时所需的指令,从而也提高了电源效率。此外,受益于丰富的软件开发环境,RVV还使其他开源工具链(如LLVM和GCC)能够支持自动矢量化,进一步简化了矢量处理应用的开发。

使用定制DSP指令增强RVV,实现高效信号处理

越来越多的SoC开发者倾向于选择针对特定应用的可选定制扩展。尽管RVV已经可以支持一些定点运算,但增加针对信号处理应用(如FFT、FIR和矩阵乘法)和多媒体处理应用(包括音频、视频和图像处理)的DSP指令还能进一步优化处理器的功耗、性能和面积(PPA)。

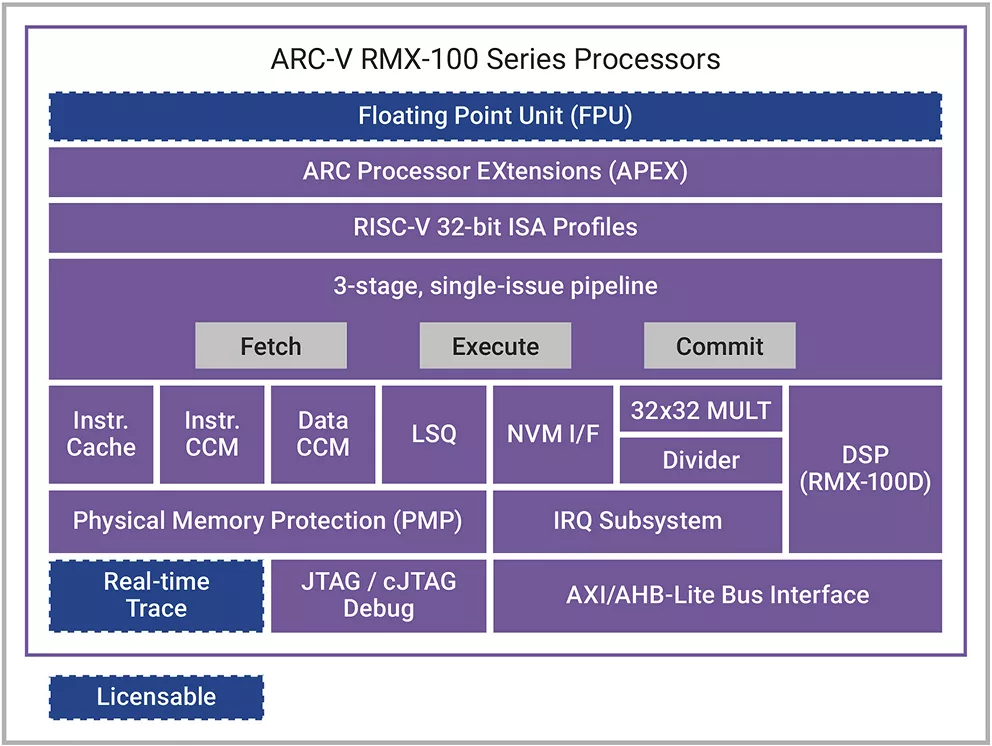

新思科技ARC-V RMX-100D系列处理器(图2)将RVV1.0标准与定制DSP指令相结合,为低功耗嵌入式应用创建高度优化且经济实惠的解决方案,实现高效的信号处理。通过集成DSP和RVV功能,可以显著改善周期数性能和能效。

▲图2 新思科技ARC-V RMX-100D处理器IP框图

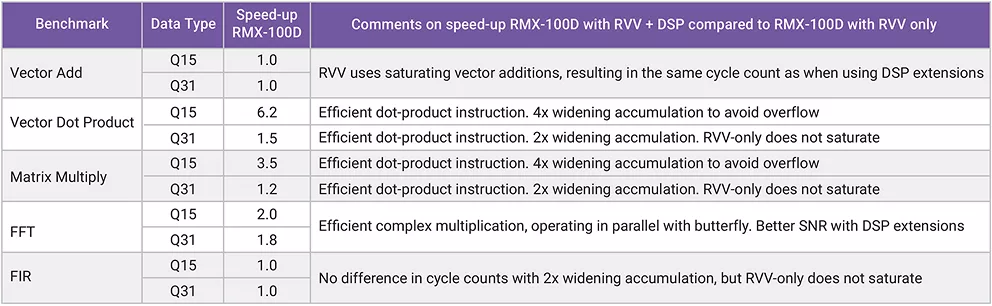

图3中的数据表明,信号处理中常用算法的周期数、性能和效率得到显著改善,具体包括:矢量加法、矢量点积、矩阵乘法、快速傅里叶变换(FFT)和有限脉冲响应(FIR)。与仅限RVV的标准实现相比,结合RVV与DSP指令的新思科技ARC-V RMX-100D处理器可以实现更多增强功能。

▲图3使用RMX-100D处理器增加定制DSP指令时,速度与RVV相比有所提升

结论

RISC-V指令集架构(ISA)支持模块化和可扩展的设计实现,为低功耗嵌入式应用提供了理想的基础。通过使用DSP功能扩展RVV,基线RISC-V实现可显著提高周期数性能和能效,同时保持向后兼容性并充分实现软件复用,以满足各种信号处理工作负载的需求。新思科技的ARC-V RMX-100D和RMX-500D系列处理器结合了RVV1.0与定制DSP指令,为需要高级信号处理的低功耗嵌入式应用提供高度优化且经济实惠的解决方案。

-

mcu

+关注

关注

147文章

19128浏览量

403978 -

嵌入式系统

+关注

关注

41文章

3823浏览量

133887 -

新思科技

+关注

关注

5文章

979浏览量

52989 -

RISC-V

+关注

关注

49文章

2948浏览量

53552

原文标题:RISC-V+DSP:嵌入式系统创新的超级组合!

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

新思科技ImperasDV解决方案让RISC-V处理器验证效率翻倍

新思科技VC Formal解决方案在RISC-V验证中的应用

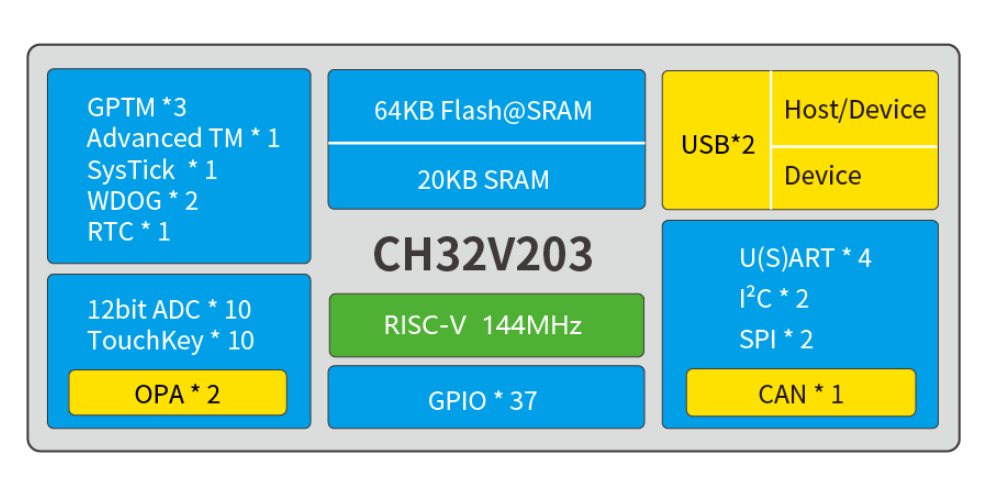

CH32V203系列RISC-V增强低功耗MCU单片机

新思科技ARC-V处理器驱动RISC-V市场无限机遇

重磅合作!Quintauris 联手 SiFive,加速 RISC-V 在嵌入式与 AI 领域落地

Andes晶心科技推出全新32位RISC-V处理器D23-SE

新思科技全栈工具链助力RISC-V设计高效进阶

RISC-V如何变革嵌入式系统设计

为什么RISC-V是嵌入式应用的最佳选择

PIC64GX1000 RISC-V MPU:一款面向嵌入式计算的高性能64位多核处理器

2025新思科技RISC-V科技日活动圆满结束

【好书推荐】RT-Thread第18本相关书籍!RISC-V嵌入式系统设计 | 技术集结

新思科技RISC-V处理器助力低功耗嵌入式应用

新思科技RISC-V处理器助力低功耗嵌入式应用

评论