近期,Arm控股有限公司宣布其芯粒系统架构(CSA)正式推出了首个公开规范。这一举措旨在进一步推动芯粒技术的标准化进程,并有效减少行业碎片化现象,为芯片设计领域注入新的活力。

芯粒技术作为当前半导体行业的热门话题,其在提升芯片性能、降低功耗以及增强系统灵活性方面展现出巨大潜力。然而,随着芯粒技术的快速发展,行业碎片化问题也日益凸显。为了解决这一难题,Arm积极推出CSA公开规范,以统一的标准引领芯粒技术的未来发展。

据悉,目前已有超过60家行业领先企业积极参与了CSA的相关工作。这些企业涵盖了半导体制造、EDA工具开发、IP供应商等多个领域,包括ADTechnology、Alphawave Semi、AMI、楷登电子、云豹智能、Kalray、Rebellions、西门子和新思科技等知名公司。通过积极参与CSA项目,这些企业不仅为芯粒技术的标准化贡献了自己的力量,还得以在统一的标准下制定各自领域的芯片战略,从而加速技术创新和市场拓展。

展望未来,Arm将继续携手全球合作伙伴,共同推动芯粒技术的标准化进程,为半导体行业的持续发展注入新的动力。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ARM

+关注

关注

135文章

9588浏览量

393673 -

CSA

+关注

关注

0文章

62浏览量

21104 -

芯片设计

+关注

关注

15文章

1172浏览量

56780

发布评论请先 登录

相关推荐

热点推荐

芯自主・板可靠:视美泰国产化主板,ARM 架构 + 瑞芯微芯片+国产操作系统领跑信创落地

、瑞芯微解决方案为算力核心,搭载国产操作系统,成为信创项目、行业数字化、智能终端国产化替代的优选品牌。视美泰国产化主板全线采用ARM架构,依托瑞芯

奇异摩尔参编人工智能加速器互联芯粒技术要求团体标准发布

近日,中国电子工业标准化技术协会批准并发布了《人工智能超节点服务器技术要求》等28项团体标准。其中由中国移动研究院牵头、奇异摩尔产品市场&研发部门主要参编的《人工智能加速器互联芯粒技术要求

UCIe协议代际跃迁驱动开放芯粒生态构建

在芯片技术从 “做大单片” (单片SoC)向 “小芯片组合” (芯粒式设计)转型的当下,一套统一的互联标准变得至关重要。UCIe协议便是一套芯粒芯片互联的 “通用语言”。

面向芯粒设计的最佳实践

半导体领域正经历快速变革,尤其是在人工智能(AI)爆发式增长、对更高处理性能及能效需求持续攀升的背景下。传统的片上系统(SoC)设计方案在尺寸与成本方面逐渐触及瓶颈。此时,Multi-Die设计应运而生,将SoC拆分为多个称为芯粒

AppGallery Connect(HarmonyOS 5及以上) --公开测试创建并发布测试版本(一)

“公开测试”,填写“版本描述”,点击“确定”。

5.系统自动进入版本信息配置页面,您可以开始配置版本基础信息。

6.配置发布国家或地区。

在“发布国家或地区”栏,勾选应用需要

发表于 09-26 17:24

借助Arm芯粒技术构建计算未来

在我们近期与业界伙伴的多次交流中,明显发现芯粒时代的大幕已徐徐拉开,行业已经不再抱存对芯粒的质疑态度,而是正在合作解决如何借助芯

奇异摩尔助力OISA全向智感互联IO芯粒技术白皮书发布

在今日举行的2025开放数据中心委员会(ODCC)峰会期间,中国移动主导的《OISA全向智感互联IO芯粒技术白皮书》正式发布,并荣获2025 ODCC 年度卓越成果奖。作为AI网络全栈式互联解决方案

技术资讯 I 基于芯粒(小晶片)的架构掀起汽车设计革命

的通信能力的支持,以提升车辆性能、舒适性和安全性。芯片行业的关键进展之一是芯粒(小晶片)技术的横空出世。芯粒(小晶片)具有灵活、可扩展且经济高效的特点,能将多种技术集

中科曙光发布国内首个开放架构AI超集群系统

9月5日,在2025重庆世界智能产业博览会上,中科曙光发布了国内首个基于AI计算开放架构设计的产品——曙光AI超集群系统。该系统以GPU为核

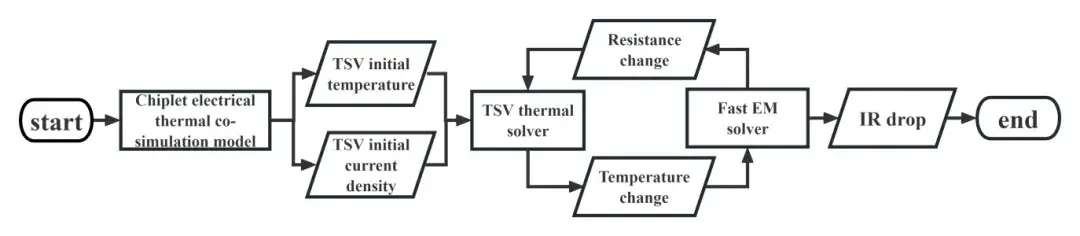

微电子所在芯粒集成电迁移EDA工具研究方向取得重要进展

随着高性能人工智能算法的快速发展,芯粒(Chiplet)集成系统凭借其满足海量数据传输需求的能力,已成为极具前景的技术方案。该技术能够提供高速互连和大带宽,减少跨封装互连,具备低成本、高性能等显著

奇异摩尔出席第三届芯粒开发者大会AI芯片与系统分论坛

多名行业同仁齐聚一堂。由奇异摩尔承办的“第三届芯粒开发者大会 - AI芯片与系统分论坛”在无锡成功举行。

Arm正式发布芯粒系统架构首个公开规范

Arm正式发布芯粒系统架构首个公开规范

评论