提要

本期课堂,我们将继续深入CMOS逻辑IC的使用注意事项,介绍如何应对电路中的危害、亚稳态、锁存以及ESD防护等问题。

Q

危害的问题

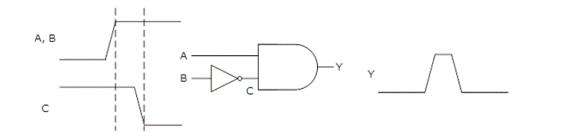

如果是由OR(或)、AND(与)和其它门组成的多输入组合逻辑,输入信号变化时序的微小差异会导致短暂的须状脉冲,这即是所谓的危害。

让我们看一下危险是如何因信号延迟的差异而发生的。在下方所示的电路图中,假设A和B同时发生信号上升沿。施加到B的信号通过反相器到达AND(与)门。由于从B进入AND(与)门的信号因反相器而延迟,AND(与)门将在不同的时序接收到输入信号A和C,所以可能会在Y输出处产生高脉冲。

A

危害的对策

组合逻辑的设计应确保避免从输入的同步变化产生所需的输出值。使用触发器调整输出时序也有助于消除危害。除了信号时序差异外,缓慢变化的输入也可能导致危害。使用带有施密特触发器输入的逻辑门,可以防止因缓慢变化的输入引起的危害。

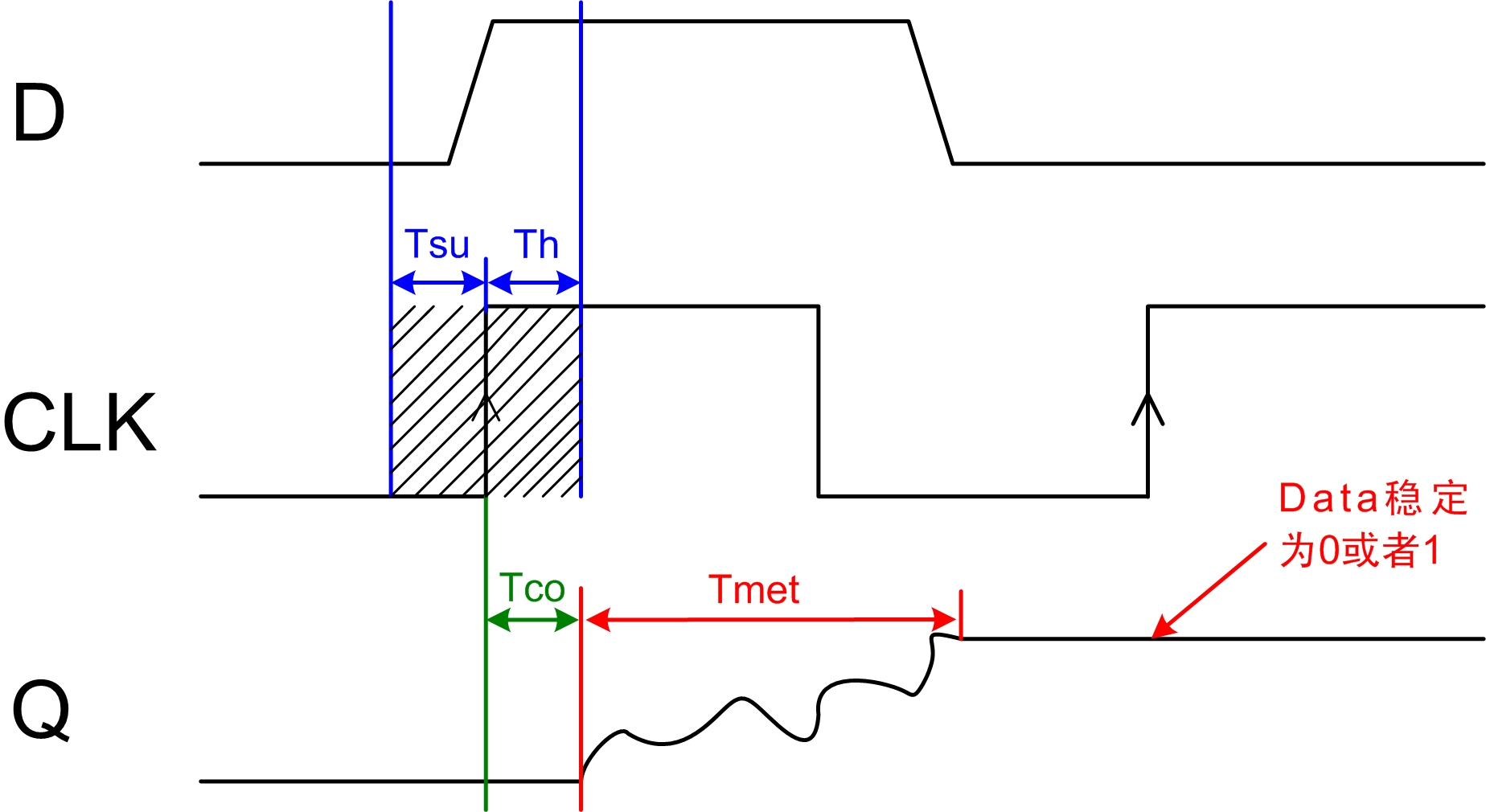

亚稳态的问题

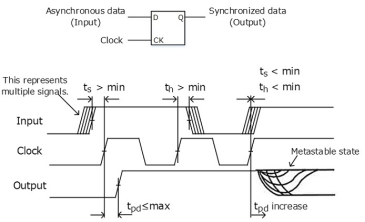

同步时序电路的输出有可能会维持一种称为亚稳态的不稳定平衡状态,具体将取决于将被锁存的数据信号相对于时钟信号的时序。当不满足数据表中显示的输入建立和保持时间(ts和th)要求时,时序电路将进入亚稳态。

当有源输入(如时钟信号)和无源输入(如数据信号)彼此异步时,可能发生亚稳态。为防止时序电路进入亚稳态,必须满足数据表中所示的推荐时序条件。

例如,当CK和D输入异步时,它们可以如下所示进行同步。但在这种情况下,应注意CK的周期和传播延迟。如果它们接近,数据信号可能不会传播到第二个触发器。

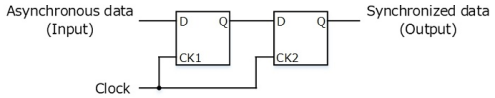

下图所示的同步器由两个触发器组成。第一个触发器将防止tpd增加并防止危害转移到第二个触发器的输出。即使在这种情况下,当CK1和CK2之间的相位差接近第一个触发器的CK至Q延迟(tpd)时,仍需注意。

注:如果两个触发器不能根据同样的时钟进行工作,可以创建与CK1同步的反相时钟并将其用作CK2(如CK2=/CK1)以避免亚稳态。

Q

锁存的问题

锁存是由可控硅整流器(SCR)产生的CMOS集成电路的特有现象。

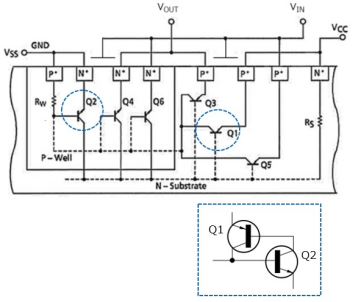

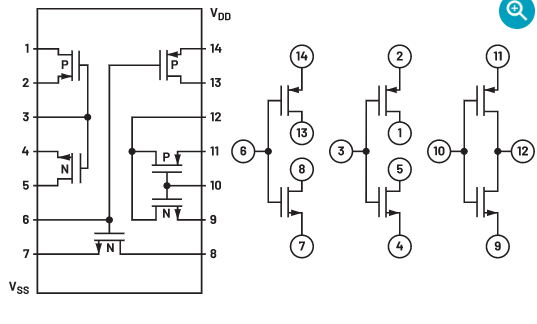

让我们以n基板上形成的CMOS逻辑IC为例进行说明。CMOS逻辑IC具有各种寄生双极晶体管(Q1至Q6),内部将形成双向可控硅电路。锁存的一个常见原因是CMOS IC输入或输出引脚上的噪声、浪涌电压或浪涌电流过大。另一个原因是供电电压发生急剧变化。在这种情况下,内部双向可控硅电路将导通,导致即使在触发信号断开时仍有过大的电流继续在VCC和GND之间流动,最终导致IC损坏。

下面简要介绍导致锁存的过程。

下图显示了包含寄生结构的CMOS电路的等效电路。在n沟道MOSFET侧的p阱中形成NPN晶体管(Q2),而在p沟道MOSFET侧的n基板中形成PNP晶体管(Q1)。寄生电阻(RS和RW)也存在于IC引脚之间。寄生元件(Q1和Q2)形成晶闸管。

例如,如果电流由于外部原因流入n基板,则n基板中的电阻器RS将发生电压降。结果,Q1导通,使得电流从VCC经由p阱中的电阻器RW流向GND。流过RW的电流在RW上产生一个电压差,这使得Q2导通,使电流流过RS。由于这将进一步增加RS上的电压差,所以Q1和Q2保持导通。因此,电流继续增加。如上所述,当p阱中的RW和n基板中的RS都发生电压差时,CMOS IC将出现锁存问题。

A

锁存的对策

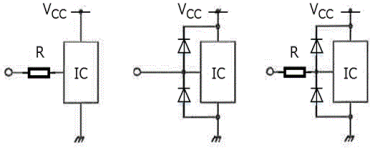

在额定条件下使用。如果对IC施加过大的浪涌,建议如下图所示在IC接口增加一个保护电路。

ESD防护的问题

CMOS逻辑IC提供符合国际标准的静电放电(ESD)抗扰度。接触较高的静电放电可能会导致CMOS逻辑IC故障或永久性损坏。因为CMOS逻辑IC输入门的氧化膜非常薄(几百至几千埃),所以它可能会被几百到几千伏特的ESD损坏。

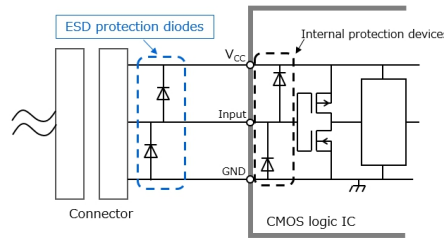

为防止这种情况,每个输入引脚通常提供ESD保护电路。但这种保护有限。对可能接触过度ESD的输入端插入外部ESD保护二极管(例如,连接到电路板外部接口的输入端)。

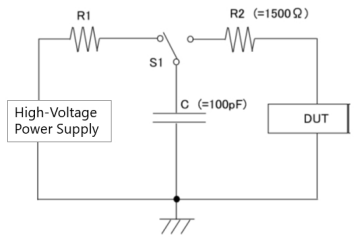

东芝提供多种ESD模型。其中,人体模型(HBM)最为常见,该模型的特点是易受人体可能产生的ESD损害的影响。关于人体电容有许多讨论。对于静电放电抗扰度测试,将使用一个100 pF电容器和一个1500 Ω放电电阻器模拟带电人体。在测试过程中,电容器充满电,然后通过电阻器放电。

HBM测试电路

至此,关于CMOS逻辑IC使用注意事项的内容就全部结束啦!希望通过这几篇文章,能够助您在电路设计中突破难关、提升工作效率。未来随着技术的不断进步,新的材料、新的IC设计和制造技术将不断涌现,芝子期待与您一起探索电子设计的新边界,共同创造更加智能、高效和可靠的电子系统。

关于东芝电子元件及存储装置株式会社

东芝电子元件及存储装置株式会社是先进的半导体和存储解决方案的领先供应商,公司累积了半个多世纪的经验和创新,为客户和合作伙伴提供分立半导体、系统LSI和HDD领域的杰出解决方案。

东芝电子元件及存储装置株式会社十分注重与客户的密切协作,旨在促进价值共创,共同开拓新市场,期待为世界各地的人们建设更美好的未来并做出贡献。

-

CMOS

+关注

关注

58文章

6233浏览量

243389 -

ESD

+关注

关注

50文章

2422浏览量

180403 -

锁存

+关注

关注

0文章

25浏览量

21123 -

东芝半导体

+关注

关注

1文章

109浏览量

15156 -

逻辑IC

+关注

关注

0文章

38浏览量

7040

原文标题:芝识课堂【CMOS逻辑IC的使用注意事项】——深入电子设计,需要这份指南(四)

文章出处:【微信号:toshiba_semicon,微信公众号:东芝半导体】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

利用IDDR简化亚稳态方案

FPGA触发器的亚稳态认识

在FPGA中,同步信号、异步信号和亚稳态的理解

一种消除异步电路亚稳态的逻辑控制方法

CMOS逻辑IC使用时如何应对电路中的危害、亚稳态、锁存以及ESD—东芝半导体带你深入电子设计

CMOS逻辑IC使用时如何应对电路中的危害、亚稳态、锁存以及ESD—东芝半导体带你深入电子设计

评论