第二期

智多晶DDR Controller介绍

最后一期我们主要介绍智多晶DDR Controller使用时的注意事项。

03智多晶DDR Controller使用注意事项

3.1 DDR BANK 布局

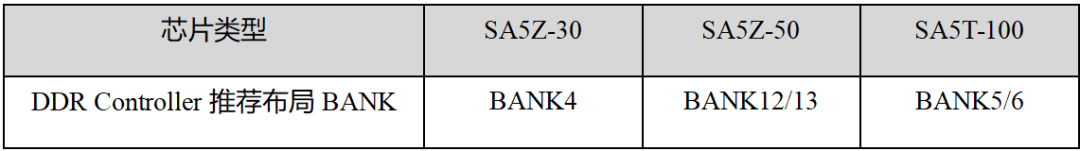

DDR Controller是硬核资源,位置是固定的,而phy是IO逻辑资源,与所在bank关联,设计PCB的时候需要选择与DDR Controller硬核位置,更接近的IO BANK作为DDR IO BANK,才能获得最佳的性能表现。下表列出了各系列芯片DDR Controller硬核靠近的BANK。

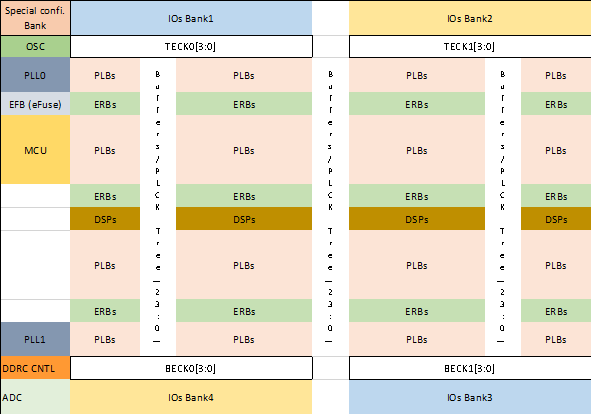

从图三、SA5Z-30 器件布局规划,可以看出DDR Controller硬核靠近BANK4的IO,所以应该将外挂的DDR引脚放置在BANK4上。

图三、SA5Z-30 器件布局规划

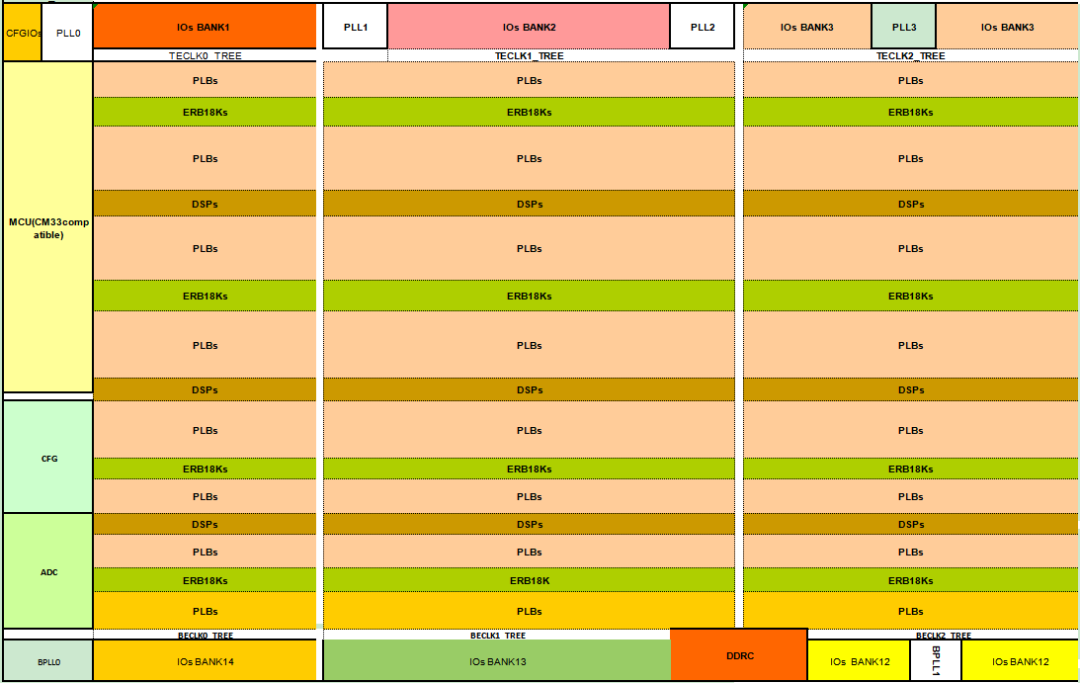

从图四、SA5Z-50 器件布局规划,可以看出DDR Controller硬核靠近BANK12/13的IO,所以应该将外挂的DDR引脚放置在BANK12或BANK13上。

图四、SA5Z-50 器件布局规划

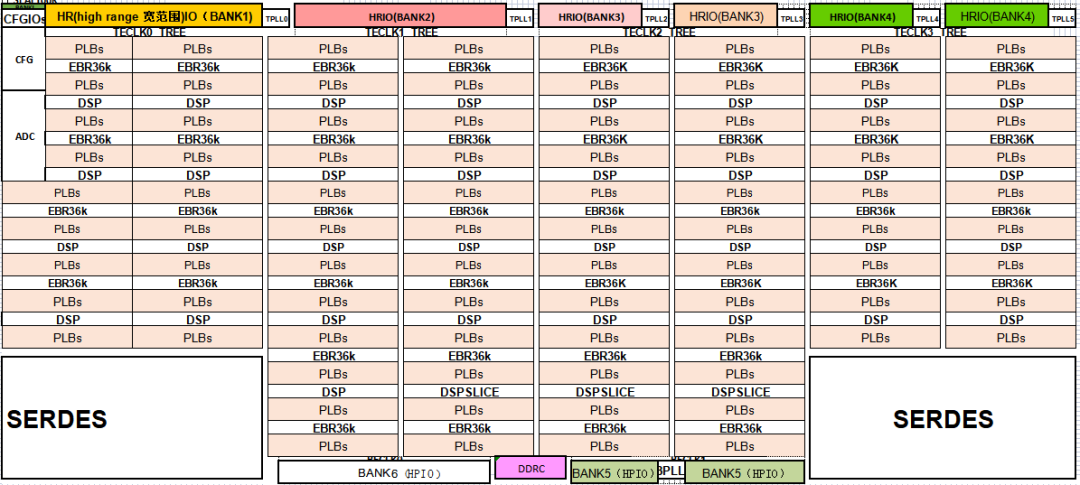

从图五、SA5T-100 器件布局规划,可以看出DDR Controller硬核靠近BANK5/6的IO,所以应该将外挂的DDR引脚放置在BANK5或BANK6上。

图五、SA5T-100 器件布局规划

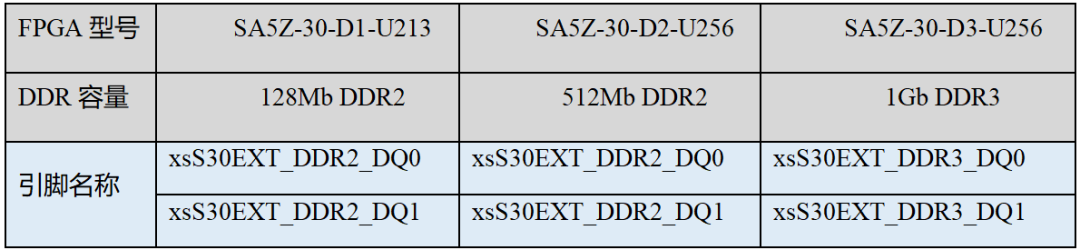

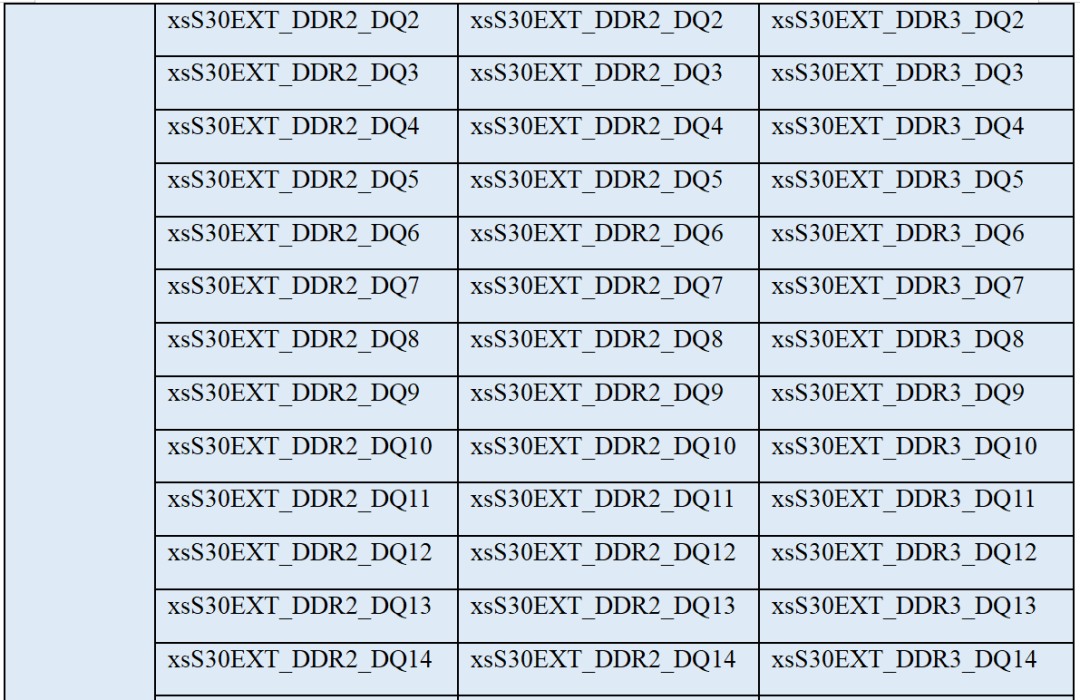

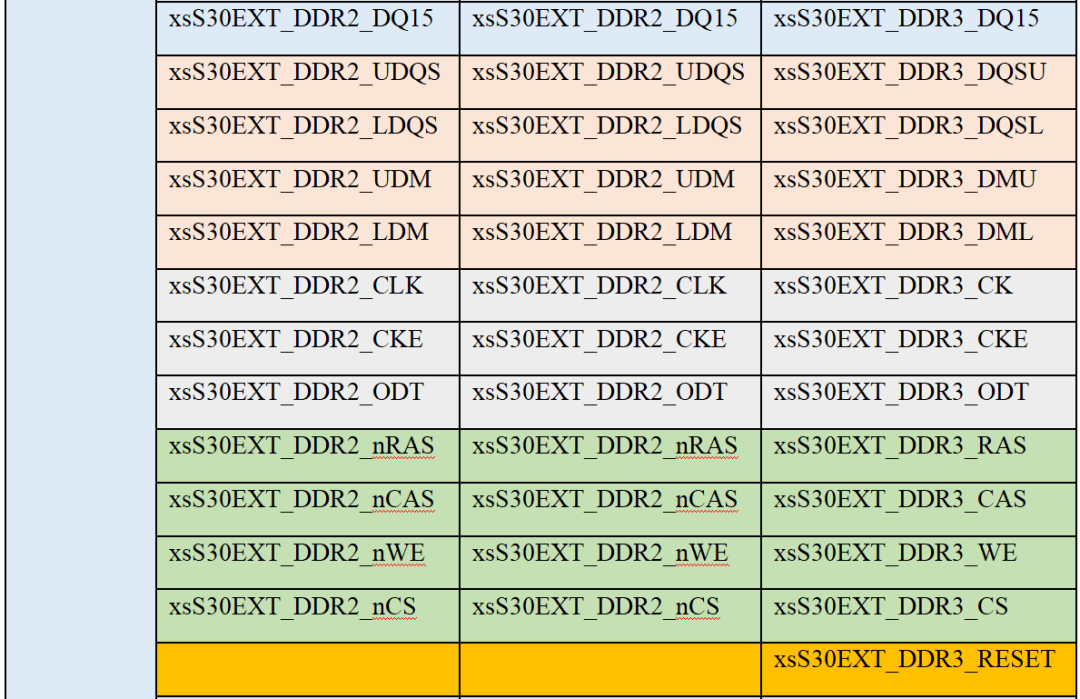

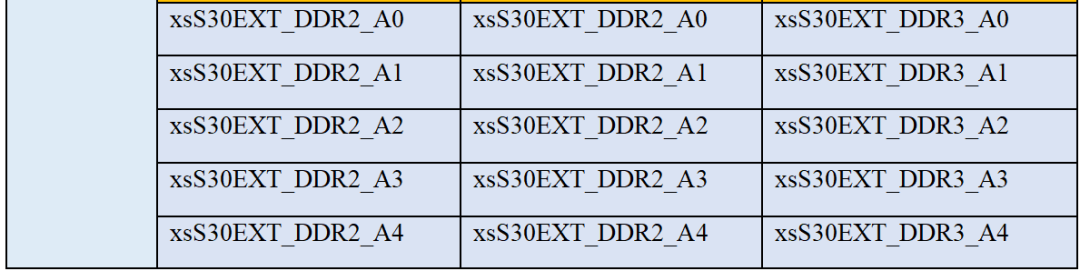

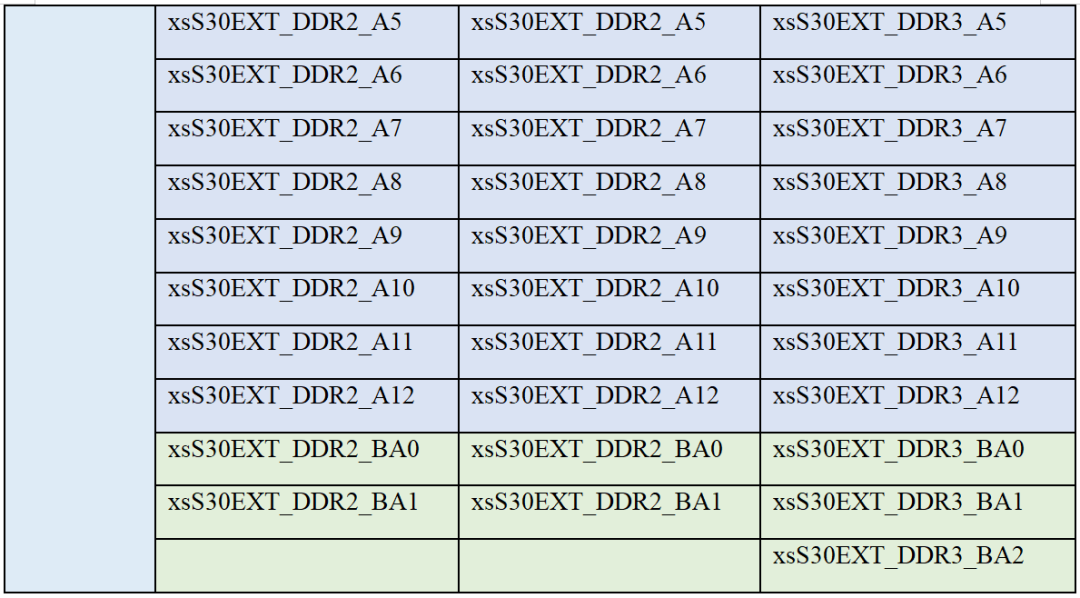

3.2合封DDR引脚命名

合封DDR2和DDR3的引脚名称是专用的,必须在设计的top层,按照以下表格的命名显式的指定出来。下表列出了现有的三种合封DDR引脚名称:

外挂DDR引脚命名没有特殊要求,只需用户设计的TOP命名和UPC引脚约束名称保持一致即可。

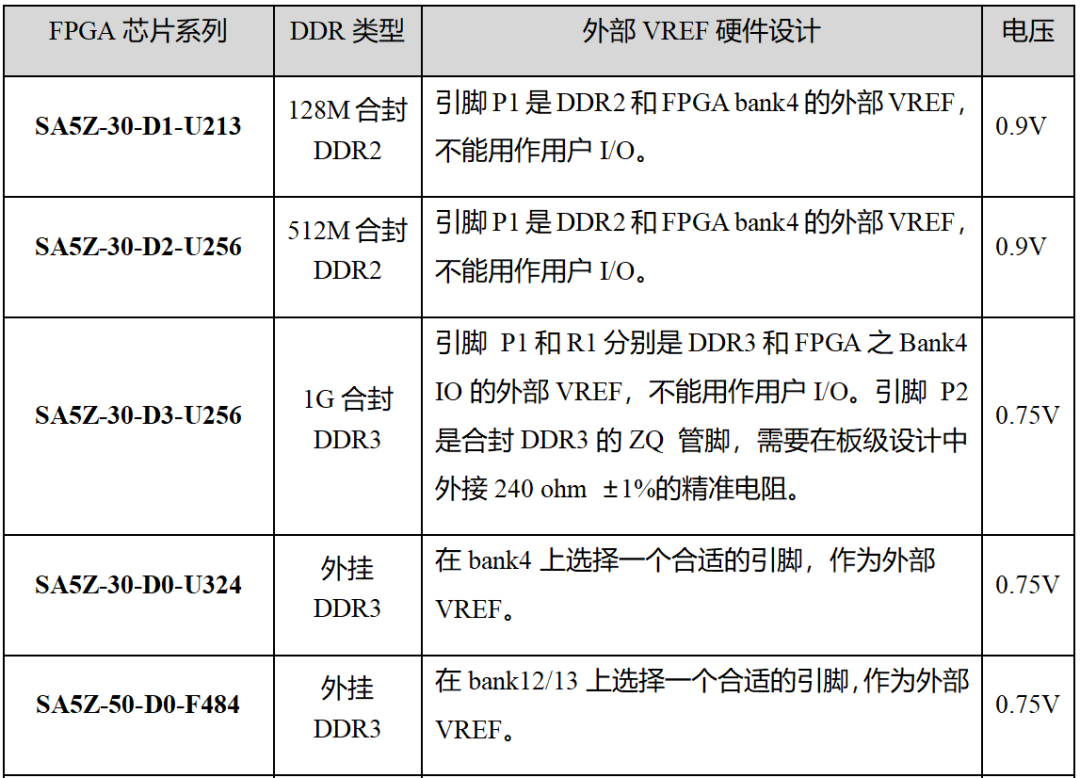

3.3外部VREF硬件设计

3.4DDR Controller CLK要求

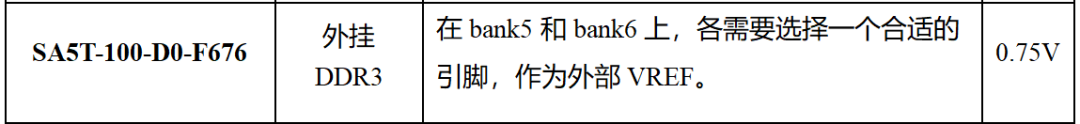

DDR Controller用户侧共有四类时钟,分别是stable_clkin、ddr_work_clkin、usr_cmd_clk、usr_data_clk;

stable_clkin要求是来自晶振或一个低速的时钟源,该时钟不能被关闭或复位,例如由PLL生成的50MHz的时钟。

ddr_work_clkin是供给硬核和phy的时钟,即phy_clk。该时钟在SA5Z-30系列器件上会被2分频,在其余器件上会被4分频,分频后得到sclk。

usr_cmd_clk和usr_data_clk是用户时钟,即usr_clk。将这两个时钟连接到相同的用户时钟即可,当用户时钟的频率和sclk一样时,可以达到最大的读写带宽。用户在实际使用中,如果对带宽要求比较高,可以将DDR控制逻辑跑到200MHz。

推荐的DDR Controller CLK组合:

注:当SA5Z-30系列FPGA 的phy_clk和usr_clk为2:1时,可以达到最大带宽。其余系列FPGA 芯片的phy_clk和usr_clk为4:1时,可以达到最大带宽。

3.5 VREF约束和调整

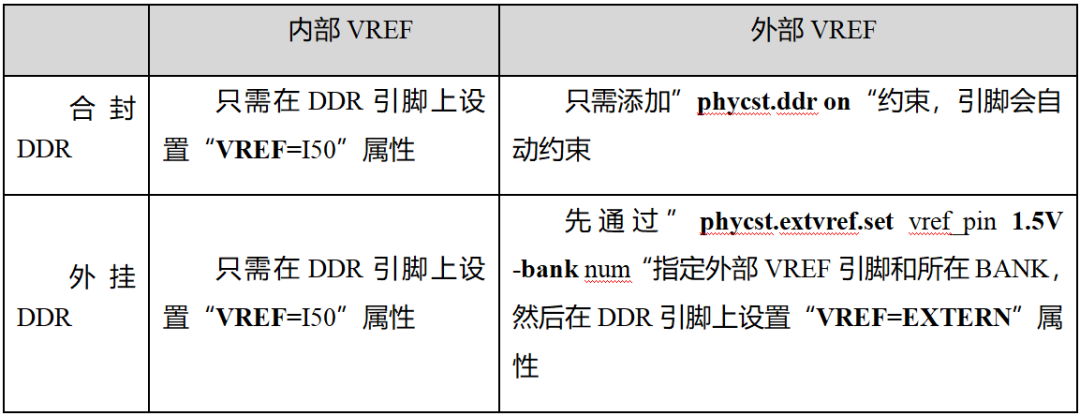

VREF有两种指定方式:内部VREF或外部VREF,具体指定方式见下表;

注1:”phycst.extvref.set vref_pin 1.5V -bank num“,vref_pin为设计中指定外部VREF引脚名称,num为DDR Controller引脚所连接的bank号。

注2: 推荐使用外部VREF。

3.5.1 合封DDR

采用内部VREF时,通过在引脚上添加“VREF=I50”属性,使能内部VREF;I50表示设置为内部VREF的50%电平。共有I45、I50、I55三个等级可供调整,对应的内部参考电平百分比为45%、50%、55%。在调试过程中,通过调整VREF电平百分比,获得最佳的判决电平。

采用外部VREF时,只需要在UPC文件中加入”phycst.ddr on“约束,即可使能外部vref和DDR Controller引脚。通过调整指定的外部VREF引脚输入的电平值,来达到最佳的判决电平。

3.5.2外挂DDR

采用内部VREF时,通过在引脚上添加“VREF=I50”属性,使能内部VREF;I50表示设置为内部VREF的50%电平。共有I45、I50、I55三个等级可供调整,对应的内部参考电平百分比为45%、50%、55%。在调试过程中,通过调整VREF电平百分比,获得最佳的判决电平。

采用外部VREF时,首先通过”phycst.extvref.set vref_pin 1.5V -bank num“指定硬件设计的VREF,再在每个引脚上添加“VREF=EXTERN”引脚属性。通过调整指定的外部VREF管脚输入的电平值,来达到最佳的判决电平。

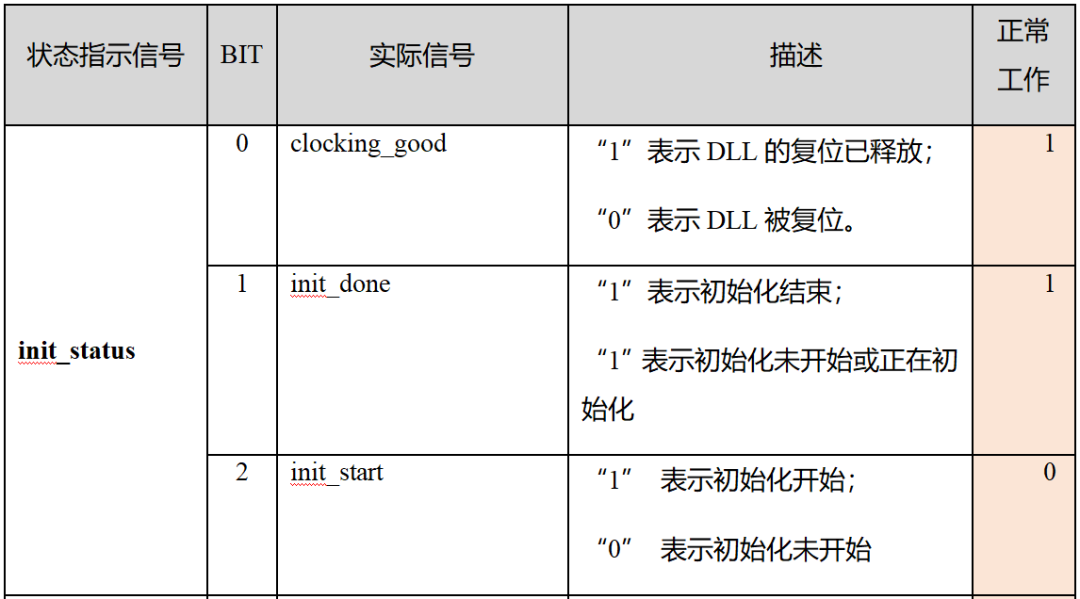

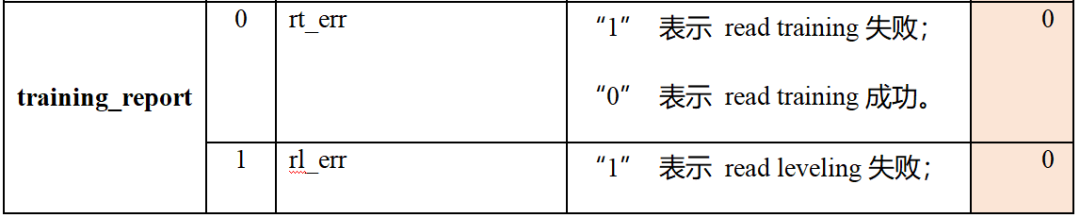

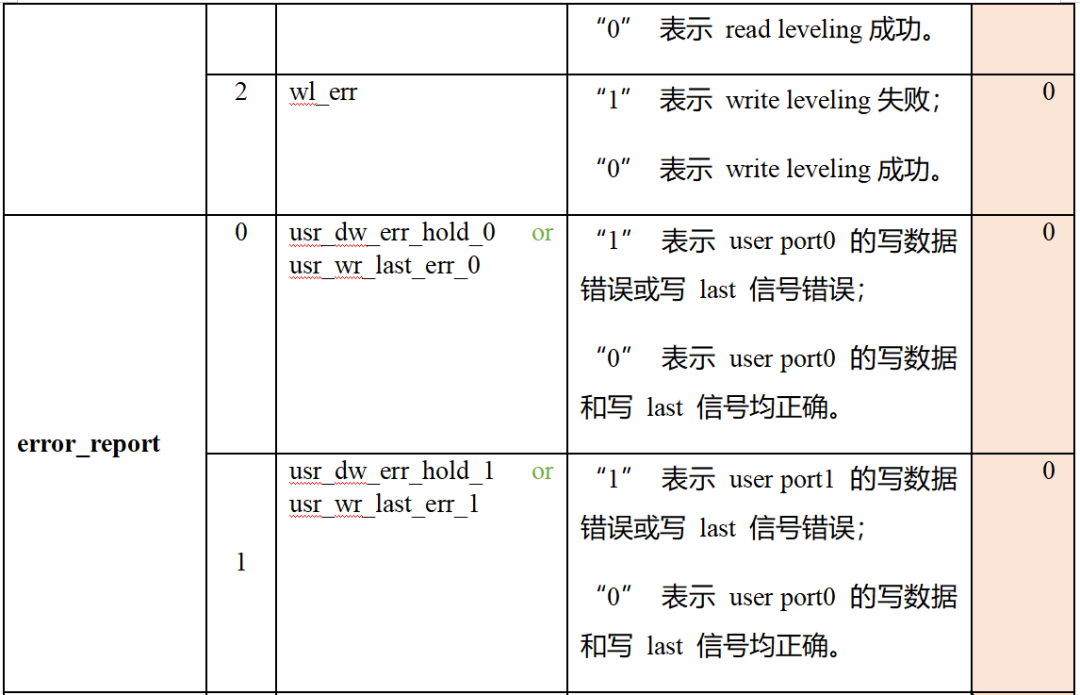

3.6状态指示信号含义

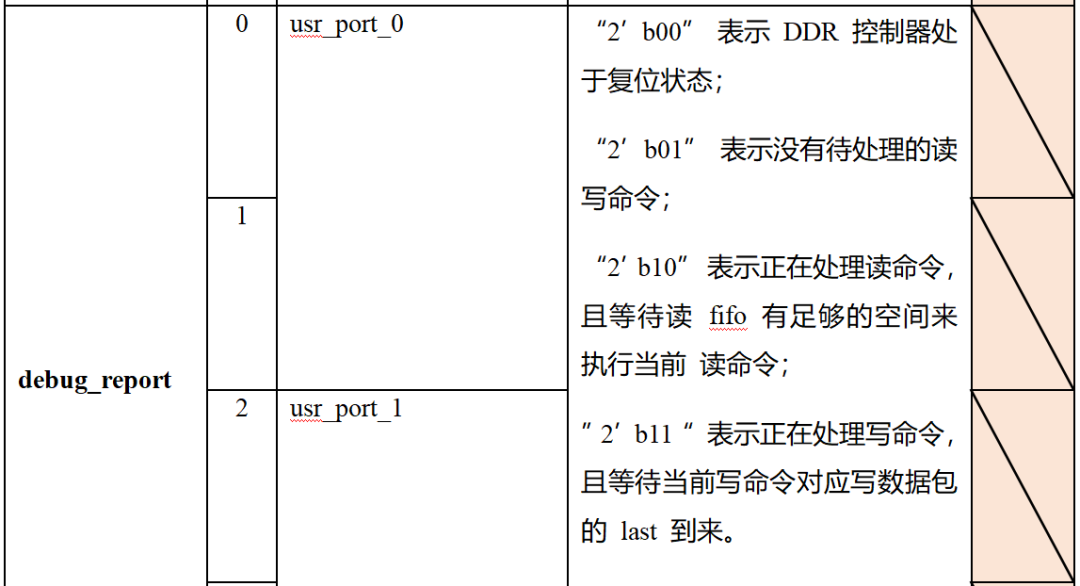

DDR Controller共有init_status、training_report、error_report、debug_report四个状态指示信号,其含义见下表:

调试过程中,在初始化阶段优先查看”init_status、training_report”状态指示信号是否正常,这两组信号受硬件板卡性能,DDR Controller配置参数,VREF等影响较大。在读写数据阶段看“error_report”信号是否正常,这组信号主要和用户读写控制逻辑相关。

3.7DDR写端

由于命令缓存FIFO深度和数据缓存FIFO深度都是有限的,用户读写数据时要特别注意,防止出现FIFO溢出或读空的现象,下表列出的不同系列DDR Controller 的FIFO深度。

DDR Controller的写端最好使用预读FIFO来缓存要写入的数据,当PHY_CLK和USR_CLK不匹配时,会出现写端有效信号不连续的问题。需要特别注意DDR Controller的ready信号的反压,否则会出现个别数据未写入问题或者重复写入的现象。同时采用预读FIFO可以保证读写效率。

04智多晶DDR Controller总结

智多晶的DDR Controller是其SEAL 5000系列FPGA芯片中的重要功能模块,广泛应用于工控、通信、消费电子和汽车电子等领域。它通过高可靠性和精准时序控制能力,满足了各领域对数据处理的严格要求,同时降低了设计难度和系统功耗。

工控领域:用于PLC等设备,快速响应传感器信号,实现精准控制。通信领域:支持高速数据缓存和传输,适用于基站、交换机和路由器。消费电子领域:提升手持设备的运行速度和续航能力。汽车电子领域:处理自动驾驶辅助系统中的图像识别和传感器数据融合。

智多晶Seal 5000系列FPGA内置DDR Controller,支持DDR2和DDR3颗粒,部分型号支持DDR4。支持多种突发长度和位宽拼接,优化数据传输效率。通过优化时序控制和电源管理,实现低功耗的目的。

使用智多晶的DDR Controller需要注意以下事项:

1 BANK布局:DDR Controller硬核位置固定,设计时需将DDR引脚放置在靠近硬核的BANK。

2 引脚命名:合封DDR引脚名称专用,需在设计中显式指定。

3 VREF设计:支持内部和外部VREF,推荐使用外部VREF以获得更好的性能。

4 时钟要求:用户侧时钟需满足特定频率要求,以实现最大带宽。

5 状态指示信号:通过状态指示信号监控初始化、训练和错误状态。

6 FIFO管理:写端需注意FIFO深度和反压问题,避免数据溢出或读空。

智多晶DDR Controller凭借其高性能、低功耗和灵活的配置能力,为各领域的复杂应用提供了可靠的解决方案,同时简化了设计流程,提升了系统的整体性能和竞争力。

-

芯片

+关注

关注

463文章

54432浏览量

469393 -

pcb

+关注

关注

4417文章

23966浏览量

426180 -

DDR

+关注

关注

11文章

761浏览量

69566 -

Controller

+关注

关注

0文章

398浏览量

58455 -

引脚

+关注

关注

16文章

2120浏览量

56025

原文标题:“芯”技术分享 | 智多晶DDR Controller介绍第二期

文章出处:【微信号:智多晶,微信公众号:智多晶】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

智多晶PLL使用注意事项

智多晶DDR Controller使用注意事项

智多晶DDR Controller使用注意事项

评论