本文将分享 MathWorks 参与中国集成电路设计业高峰论坛暨展览会 ICCAD-Expo的展台展示以及发表主题演讲《MATLAB 加速数字和模拟芯片设计--高效实现 HLS、UCIe 和UVM》。 在当前全球科技竞争加剧的背景下,中国集成电路设计行业迎来了前所未有的机遇与挑战。为了更好地应对快速变化的市场需求,增强自主创新能力,并提升国际竞争力,行业内正积极寻求新的突破和发展路径。 作为致力于“加速科学与工程”的技术先锋,MathWorks 于 2024 年 12 月 11-12 日在上海参与了 ICCAD-Expo 展览会。在这场汇聚了业内顶尖专家和创新者的盛会上,MathWorks 在 EDA 与 IP 设计服务(一)分会场上分享了题为《MATLA B助力数字与模拟芯片设计:高效实现 HLS、UCIe 和 UVM》的主题演讲:

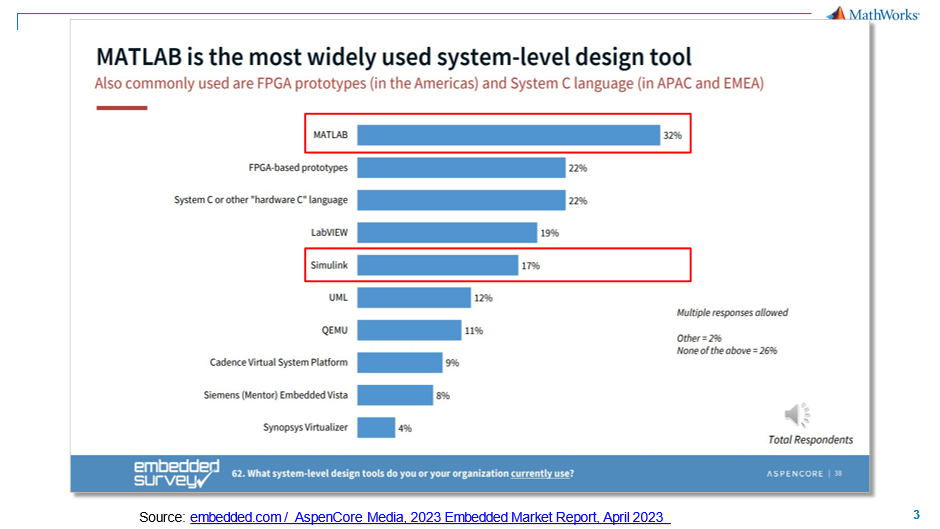

(一)MATLAB 是最广泛使用的芯片系统建模工具

MATLAB 和 Simulink 是全球芯片设计工程师最青睐的系统建模工具,广泛应用于高效且高质量的芯片研发。MATLAB 提供基于语言的简洁建模环境,支持无时钟限制的算法开发,而 Simulink 则提供图形化建模平台,支持多速率模块、状态机以及其他复杂的建模结构。MATLAB 代码可以整合到 Simulink 模型中,您可以灵活地为芯片各个子系统选用最佳的建模工具。

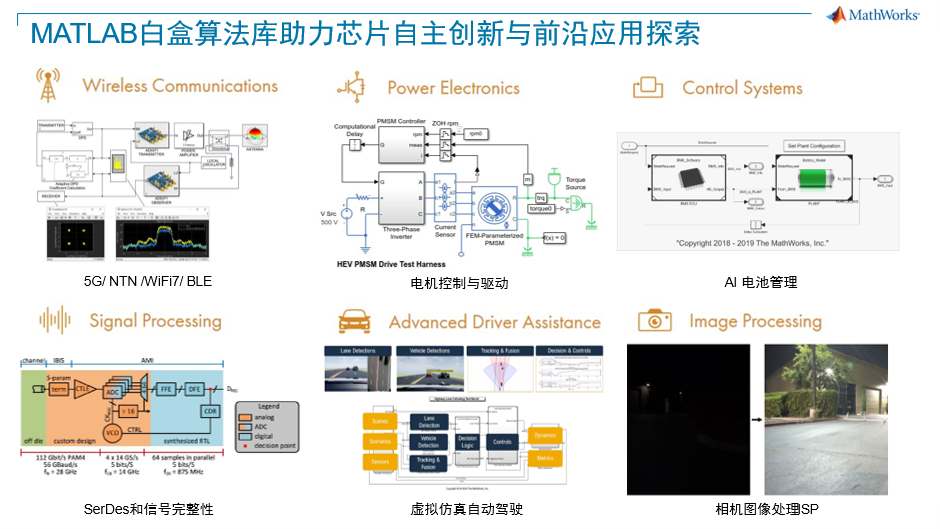

MATLAB 丰富的白盒算法库为芯片系统工程师和算法设计师提供了加速系统架构设计和算法开发的有力工具。无论是研究人员探索新的芯片设计可能性,还是技术支持工程师开发面向客户的芯片应用示例,都能在 MATLAB 的算法库中找到丰富且适用的支持资源。涵盖的内容包括但不限于:

符合 5G/WiFi/NTN/Bluetooth 等无线通信标准的物理层算法和信道模型;

新能源汽车及储能系统中的电池参数估计及电池管理系统(BMS)算法;

UCIe/Ethernet/DDR5/PCIe6/USB 等 SerDes 接口并生成 IBIS-AMI 模型;

车道级自动驾驶虚拟验证环境,以及多传感器融合及路径规划控制算法;

用于拍照、高清显示和触控等应用场景的图像处理和 AI 算法。

通过利用这些算法库,工程师们可以更迅速地进行原型设计和验证,确保芯片产品既符合最新的行业标准,又能满足特定的应用需求。

▼

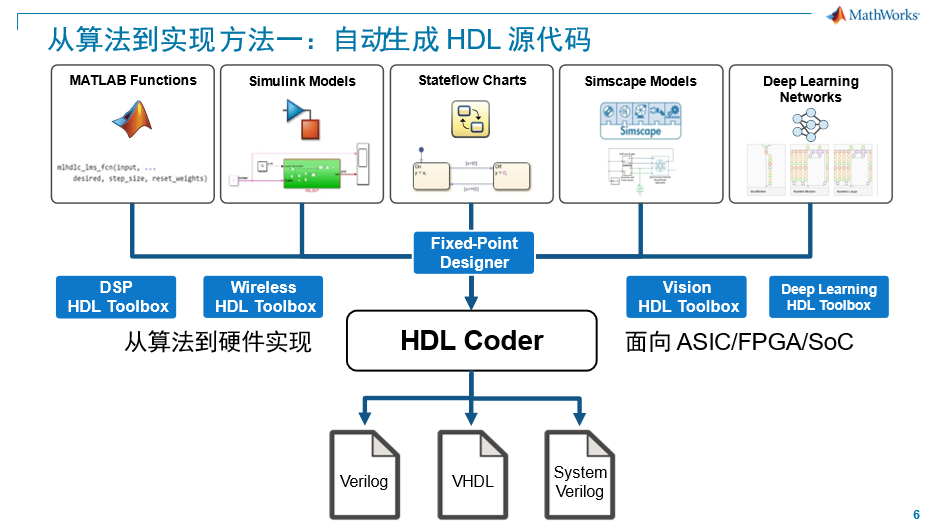

(二)无缝链接芯片算法设计与 HDL 实现

在 MATLAB 和 Simulink 中完成算法开发后,芯片设计师们可以利用 Fixed-Point Designer 工具自动将浮点算法转换为适合RTL实现的定点算法,从而优化芯片面积和性能。接下来,借助 HDL Coder,能够快速地将这些算法模型生成为白盒的 Verilog 或 VHDL 代码,确保了从算法设计到硬件实现的平滑过渡。 MATLAB 还提供了一系列专为 RTL 优化的算法模块库,覆盖数字信号处理、无线通信、计算机视觉和深度学习等领域。通过调用这些预优化的模块,用户可以迅速构建并优化其应用,并且通过自动化代码生成直接转换为白盒的 HDL 代码。

此外,MATLAB 还支持生成 C/C++、SystemC 和 IBIS-AMI 等多种语言和标准文件,适配不同的应用场景,加速芯片原型设计、实现的过程。

▼

(三)验证左移提高芯片设计质量

随着算力需求的不断增长,芯片系统的复杂性也随之增加,这使得降低设计风险成为关键挑战。验证左移作为一种有效的方法论,正逐渐受到业界的广泛关注,旨在通过在设计早期阶段引入全面的验证措施,提高最终产品的可靠性和质量。 MATLAB 和 Simulink 不仅在其平台内提供了丰富的测试覆盖率分析、形式化验证、故障注入与分析等验证功能,还为 EDA 生态系统集成了多种验证接口,例如:

与 HDL 仿真器的联合仿真:自动执行验证过程,在早期阶段高效地检测和修正差异,确保 RTL 实现的正确性;

与 FPGA 硬件的协同仿真和调试:在 FPGA 硬件中测试算法实现,提供实时性能反馈,加速迭代过程;

生成 UVM 测试框架:重用 MATLAB 和 Simulink 模型作为黄金参考模型、激励生成器或经过验证的测试平台,简化复杂的验证环境搭建,提高测试效率。

通过将验证过程前置并集成到设计流程中,MATLAB 和 Simulink 帮助芯片工程师们更早地识别潜在问题,减少后期修正的成本和时间,确保产品能够更快、更可靠地推向市场。

▼ 综上所述,MATLAB 为芯片工程师提供了一套全面的自顶向下研发工具,涵盖了从架构设计、算法仿真、定点化、HDL 代码生成、IBIS-AMI 模型生成、UVM 框架生成等关键工作流程。 MathWorks 一直坚定支持中国集成电路设计行业,致力于推动本地技术创新,助力工程师们加速将概念转化为实际产品,从而推动整个行业的快速发展与进步。 今年,MathWorks 中国推出了加速器计划和初创企业计划,旨在为预算有限、资源有限、时间有限的初创客户提供更多支持和帮助,敬请点击前方链接垂询。

-

MATLA

+关注

关注

0文章

13浏览量

13632 -

UVM

+关注

关注

0文章

183浏览量

19943 -

HLS

+关注

关注

1文章

133浏览量

25598 -

UCIe

+关注

关注

0文章

52浏览量

1993

原文标题:资源下载 | MathWorks 参与中国集成电路设计业高峰论坛暨展览会 ICCAD-Expo 2024

文章出处:【微信号:MATLAB,微信公众号:MATLAB】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

模拟前端芯片是做什么的(什么是模拟前端芯片)

UCIe协议代际跃迁驱动开放芯粒生态构建

AFE模拟前端芯片是什么(模拟前端芯片作用)

NVMe高速传输之摆脱XDMA设计23:UVM验证平台

新思科技UCIe IP解决方案实现片上网络互连

NVMe高速传输之摆脱XDMA设计18:UVM验证平台

泰克MSO64B示波器使用一个探头同时测量模拟和数字信号的方法

如何使用AMD Vitis HLS创建HLS IP

MATLA B助力数字与模拟芯片设计:高效实现HLS、UCIe和UVM

MATLA B助力数字与模拟芯片设计:高效实现HLS、UCIe和UVM

评论