Chiplet技术简介

Chiplet技术,就像用乐高积木拼搭玩具一样,将芯片的不同功能模块,例如CPU、GPU、内存等,分别制造成独立的小芯片。然后,通过高速互联技术将它们连接在一起,形成一个完整的芯片。比如说NVIDIA最新发布的DGX B200,就是Chiplet技术下的产物。这也是NVIDIA第一款Chiplet GPU芯片,凭借 NVIDIA Blackwell 架构在计算方面的进步,DGX B200 的训练性能是 DGX H100 的 3 倍,推理性能是 DGX H100 的 15 倍,想了解更多Chiplet架构的小伙伴,可以移步视频号。

Chiplet的技术优势

01提高芯片良率

传统的单芯片设计模式,随着芯片尺寸的不断缩小,迈入3nm、2nm制程后,芯片的良率成为一大挑战。据悉,头部晶圆大厂的3nm良率也仅在50%左右。而Chiplet技术将芯片设计分解成多个更小的模块,每个模块可以单独进行制造和测试,从而可以提高整体芯片的良率。

02降低芯片成本

随着行业转向更小的工艺节点,生产大型芯片的成本持续增加。目前台积电3纳米晶圆每片成本为20,000美元,比5nm(16,000 美元)晶圆成本上涨了25%,而行业预计2nm晶圆成本将比3nm再增加50%。制造大型整体芯片将变得越来越不经济。在摩尔定律基本上不再带来经济效益的情况下,Chiplet被认为是最好的大芯片替代设计方法。Chiplet技术可以采用不同制程工艺、不同代工厂来制造不同的模块,例如可以使用成熟的制程工艺来制造成熟的IP模块,而使用更先进的制程工艺来制造关键的性能模块,这种混合制程工艺可以降低芯片的整体成本。

03提高芯片灵活性

Chiplet技术可以根据不同的需求定制芯片配置,例如可以根据客户的需求选择不同的IP模块或调整模块的数量。由于模块化设计使得各个模块独立,设计者可以针对特定需求对特定模块进行优化和迭代,而不会影响其他模块。这种灵活性使得芯片能够更好地满足不同的市场需求。

Chiplet面临的挑战

1互联技术挑战

Chiplet技术需要使用高速互联技术来将不同的Chiplet连接在一起。目前常用的互联技术包括高速SerDes、PCI Express等,但这些技术的带宽和成本都存在一定的限制。目前可以看到国际大厂在设计Chiplet芯片时,都将互联作为很重要的一环。像AMD的"Infinity Fabric"技术、英特尔的嵌入式多芯片互连桥 (EMIB) 等。

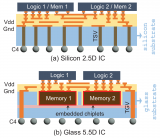

2封装技术挑战

Chiplet技术往往需要使用先进的封装技术,如2.5D、3D封装技术将不同的Chiplet封装在一起,与此同时,还要考虑散热和功耗的要求。包括台积电在内的晶圆代工厂正在通过3D封装技术来快速响应Chiplet。

3生态系统挑战

Chiplet技术需要一个完整的生态系统来支持,包括Chiplet设计工具、Chiplet制造工艺、Chiplet测试工具等。目前,Chiplet技术的生态系统还不完善,需要更多的企业和机构加入到Chiplet生态系统的建设中来。

4标准化挑战

Chiplet技术需要统一的标准来规范Chiplet的接口、互联方式等。目前业界Chiplet的互联标准规范有很多,有OIF联盟的XSR,Open联盟的BOW和OHBI,Chips Alliance的AIB,当然,还有目前最热的UCIe。UCIe(Universal chiplet interconnect express)互联标准的诞生,为Chiplet互联的兼容性和互操作性问题带来了很大的帮助,该标准由AMD、Arm、英特尔、高通、三星、台积电、日月光、谷歌、Meta和微软等十家行业巨头联合推出。随着UCIe标准的不断完善和推广,Chiplet技术将得到更加广泛的应用,并对芯片产业产生深远的影响,是德科技作为UCIe联盟的一员,也积极的参与到了标准的制定中来。

是德科技在Chiplet方面的储备

Chiplet技术需要对Chiplet之间的互联进行设计和测试。这对于芯片设计人员和测试工程师来说都是一个新的挑战。是德科技作为专业的测试方案提供商,也提供了从仿真到测试的完整方案。

1.仿真平台

ADS2024是业界支持Chiplet D2D的建模仿真工具,ADS2024 Update 1.0版本已经支持UCIe规范,能够仿真测试的指标包括:眼高,眼宽,BER,VTF等。

2.物理层测试平台

在高速接口的物理层测试方面,是德科技也提供了从发送,信道到接收端的测试方案。

3.On-wafer测试

对On-wafer测试,是德科技也与合作伙伴一起推出针对Chiplet晶圆和硅光的On-Wafer测试平台。

Chiplet技术俨然已经成为了一种重要的芯片设计趋势。

想象一下,未来我们可以像搭积木一样,轻松地构建各种功能强大、性能卓越的芯片,满足不同应用的需求。Chiplet不仅是一种制造方式,更是一种思维方式,让我们能够以更加灵活、创新的方式来构建未来的芯片世界。让我们一起期待,Chiplet技术如何继续推动科技的进步,引领我们进入更加美好的未来!

关于是德科技

是德科技(NYSE:KEYS)启迪并赋能创新者,助力他们将改变世界的技术带入生活。作为一家标准普尔 500 指数公司,我们提供先进的设计、仿真和测试解决方案,旨在帮助工程师在整个产品生命周期中更快地完成开发和部署,同时控制好风险。我们的客户遍及全球通信、工业自动化、航空航天与国防、汽车、半导体和通用电子等市场。我们与客户携手,加速创新,创造一个安全互联的世界。

-

芯片

+关注

关注

463文章

54409浏览量

469121 -

晶圆

+关注

关注

53文章

5447浏览量

132739 -

gpu

+关注

关注

28文章

5268浏览量

136058 -

chiplet

+关注

关注

6文章

499浏览量

13644

原文标题:积木造芯片?Chiplet 技术详解

文章出处:【微信号:是德科技KEYSIGHT,微信公众号:是德科技KEYSIGHT】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

拥抱Chiplet,大芯片的必经之路

多Chiplet异构集成的先进互连技术

如何突破AI存储墙?深度解析ONFI 6.0高速接口与Chiplet解耦架构

西门子EDA如何推动Chiplet技术商业化落地

跃昉科技受邀出席第四届HiPi Chiplet论坛

得一微电子受邀出席第四届HiPi Chiplet论坛

蓝牙6.0的Channel Sounding技术有哪些优势?

解构Chiplet,区分炒作与现实

玻璃中介板技术的结构和性能优势

CMOS 2.0与Chiplet两种创新技术的区别

小芯片(Chiplet)技术的商业化:3大支柱协同与数据驱动的全链条解析

Chiplet与3D封装技术:后摩尔时代的芯片革命与屹立芯创的良率保障

物联网蓝牙模块有哪些优势?

为什么选择超级电容?优势有哪些?

Chiplet技术有哪些优势

Chiplet技术有哪些优势

评论