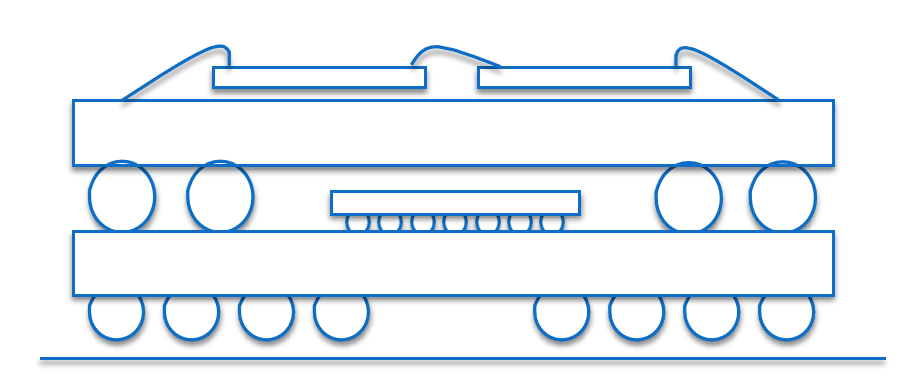

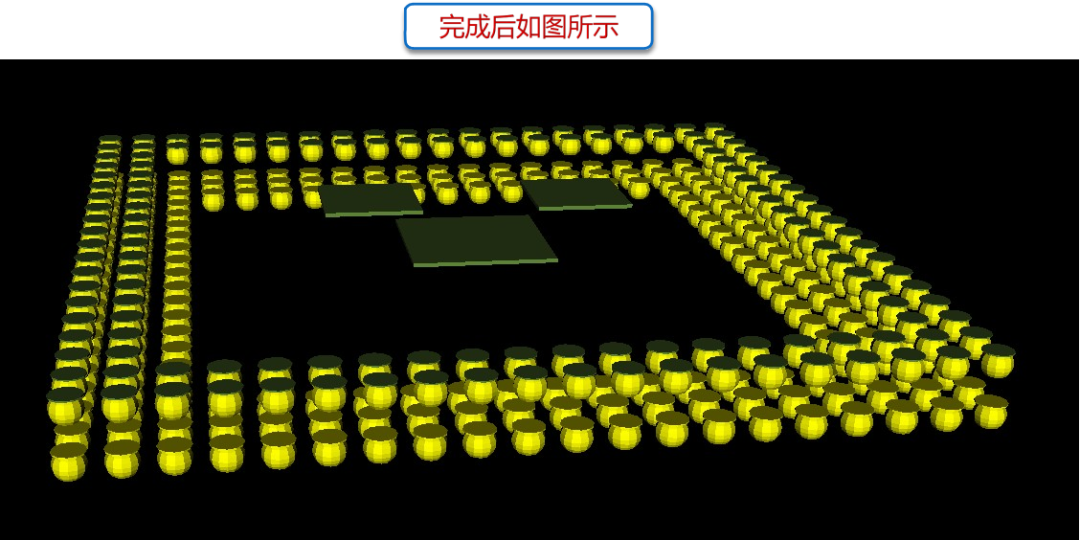

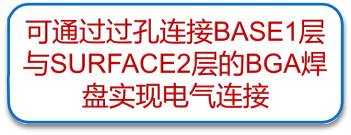

PoP封装结构

将要创建的元件参数如下:

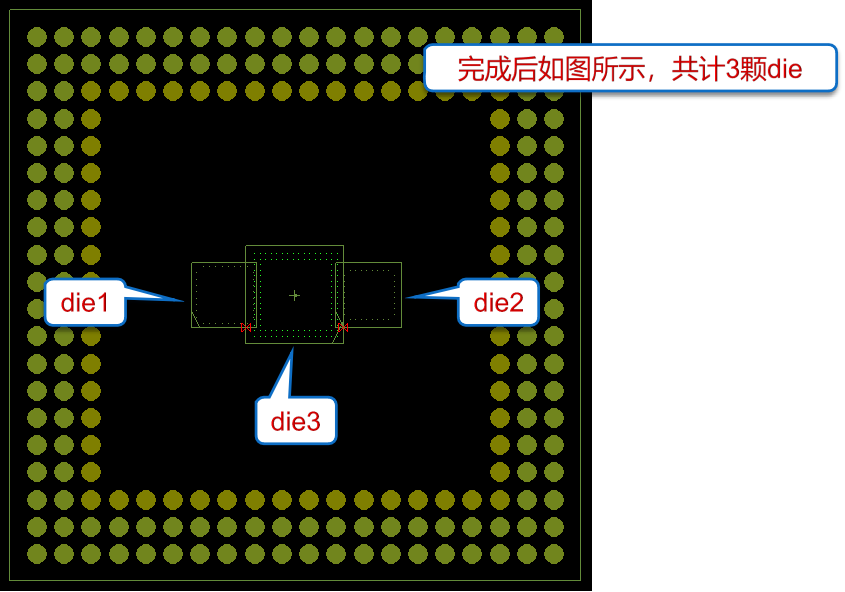

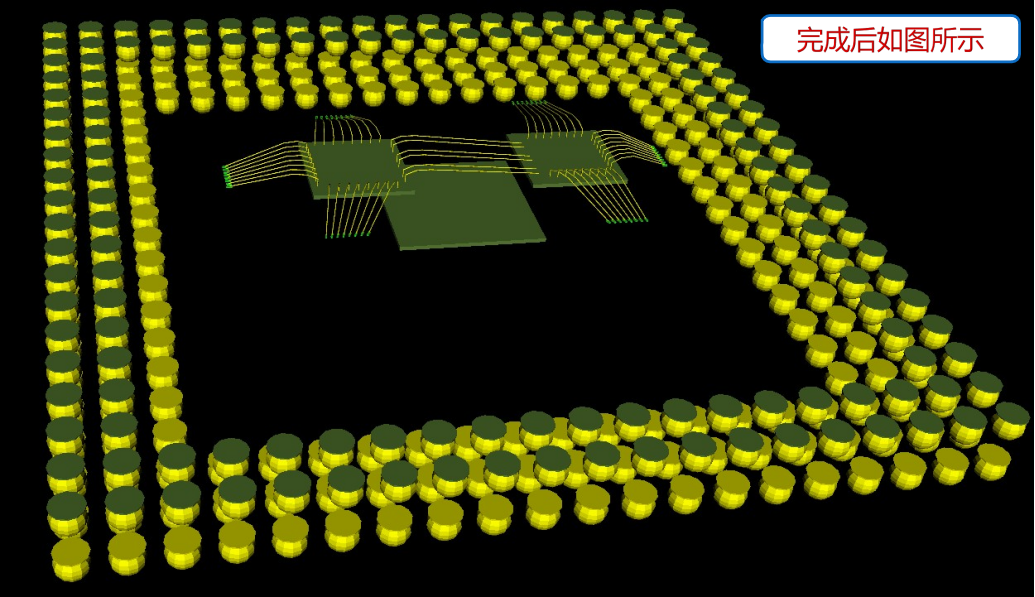

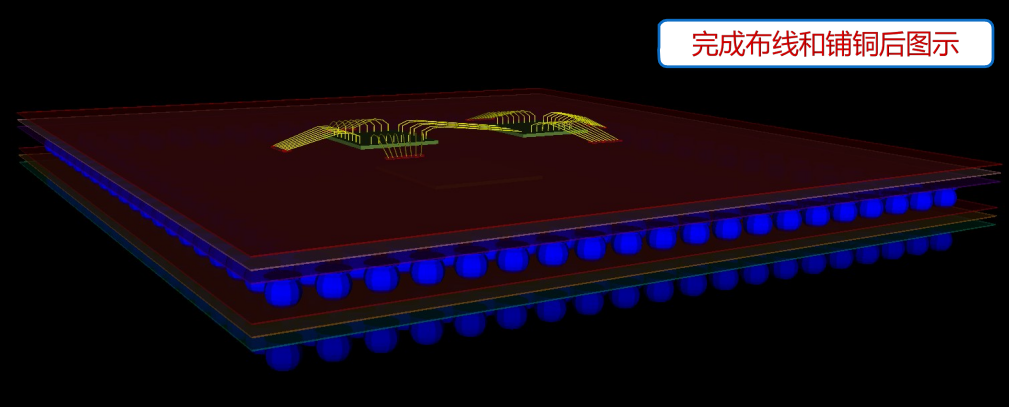

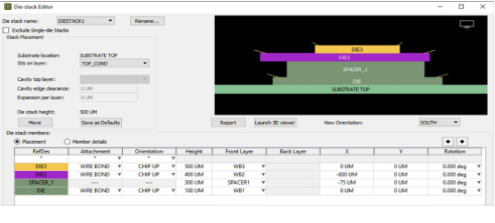

1、共有3颗die,上面封装基板正面放置2颗, Wireband连接形式;下面封装基板正面放置1颗,Flipchip连接形式;

2、共有两个封装堆叠,各有1块基板,均为BGA形式,层数均为4层;

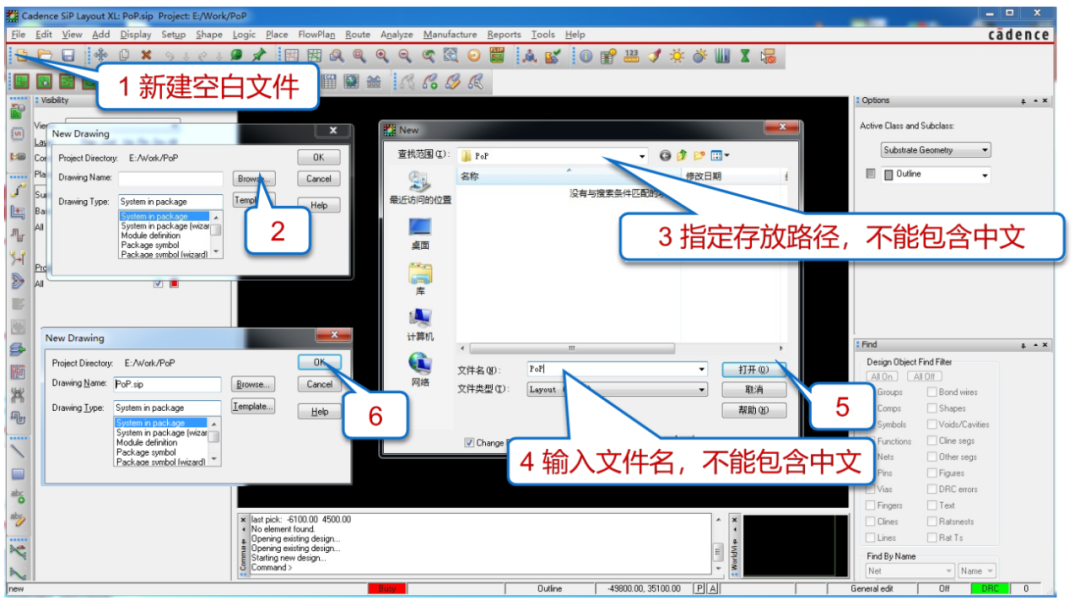

建立空白设计文件

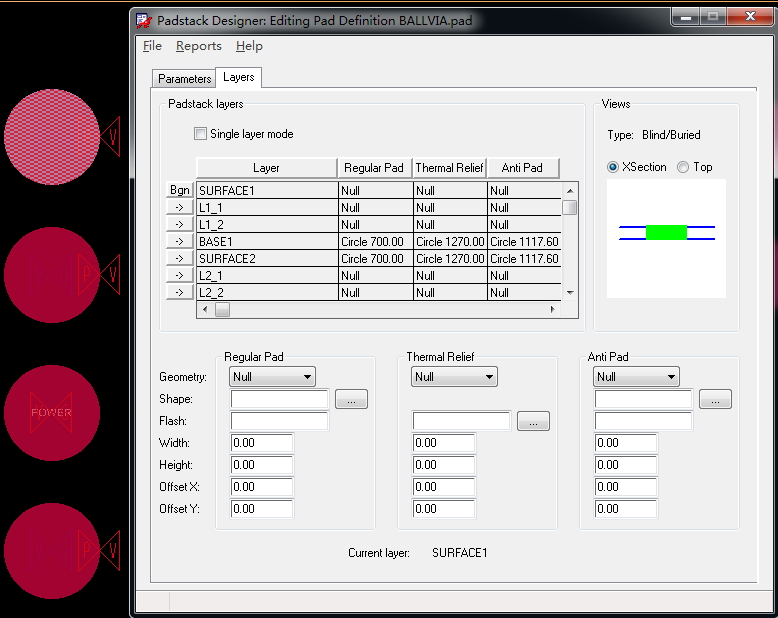

创建基板叠层结构

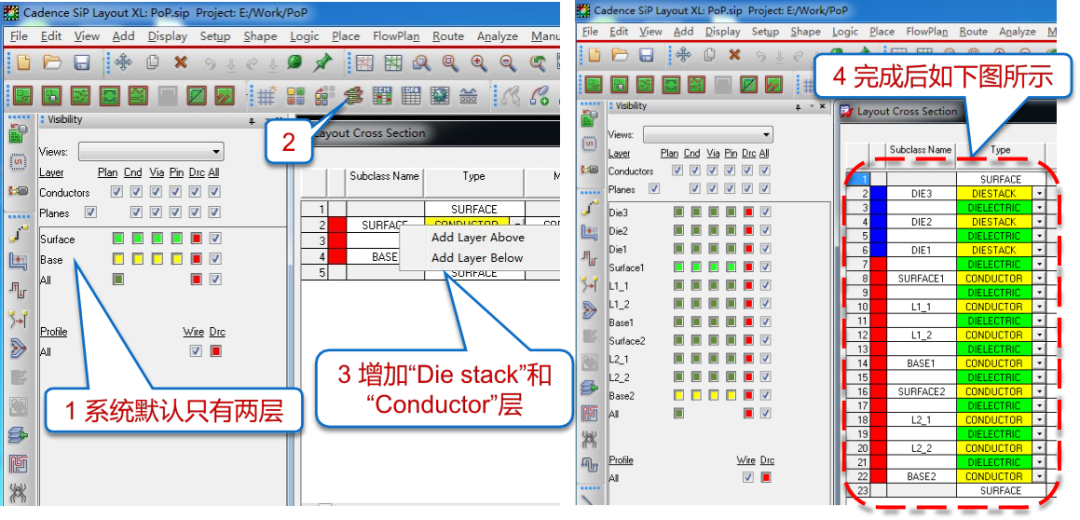

设置可放置埋入式元件的层

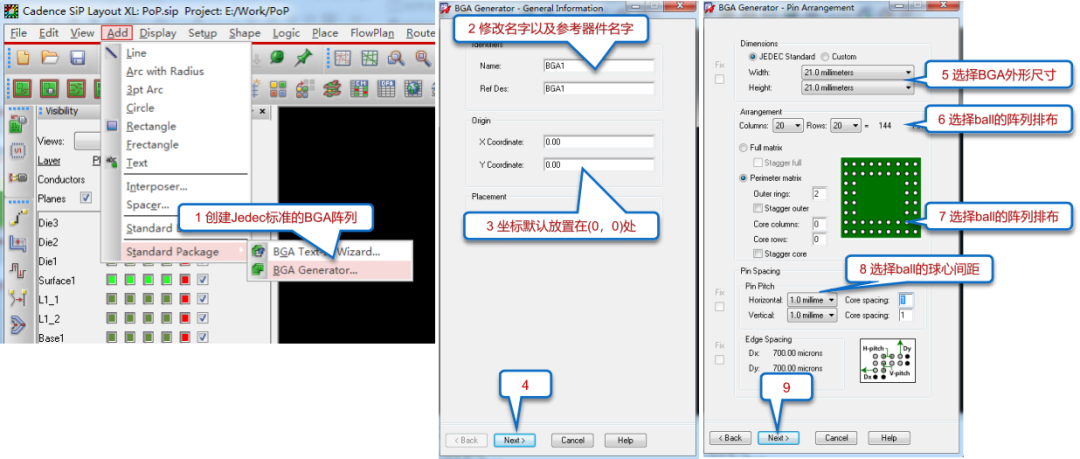

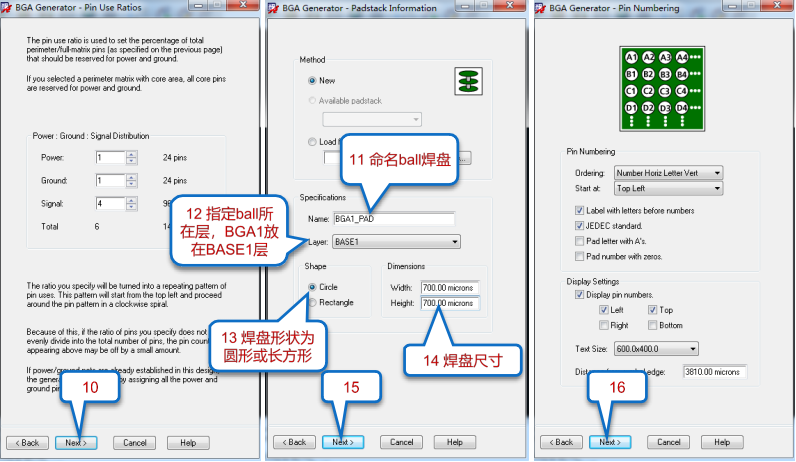

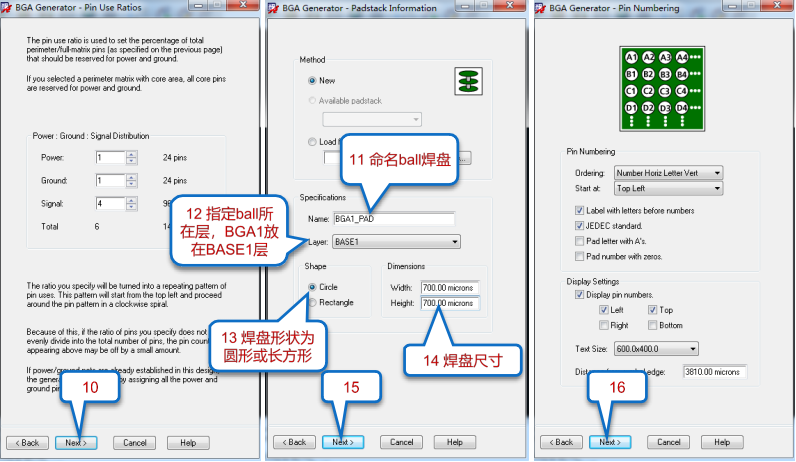

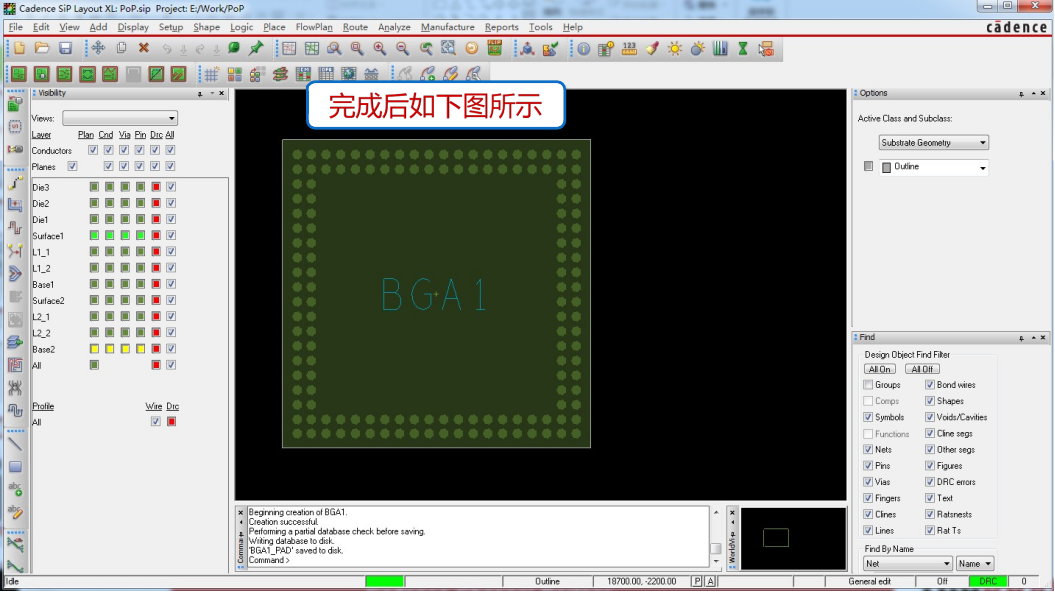

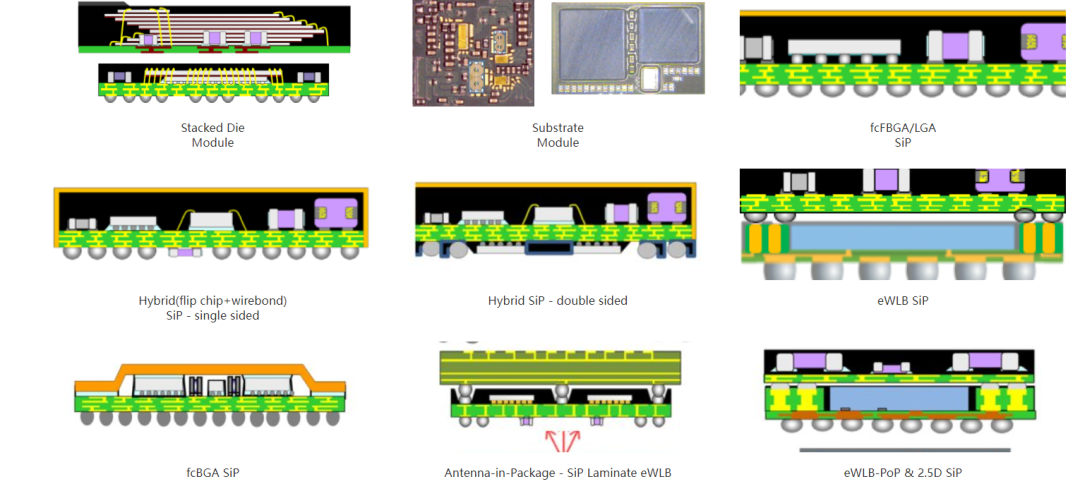

导入BGA

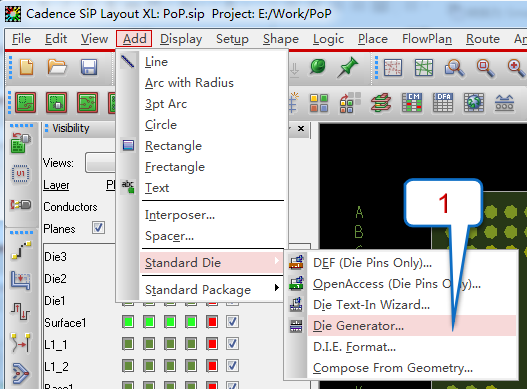

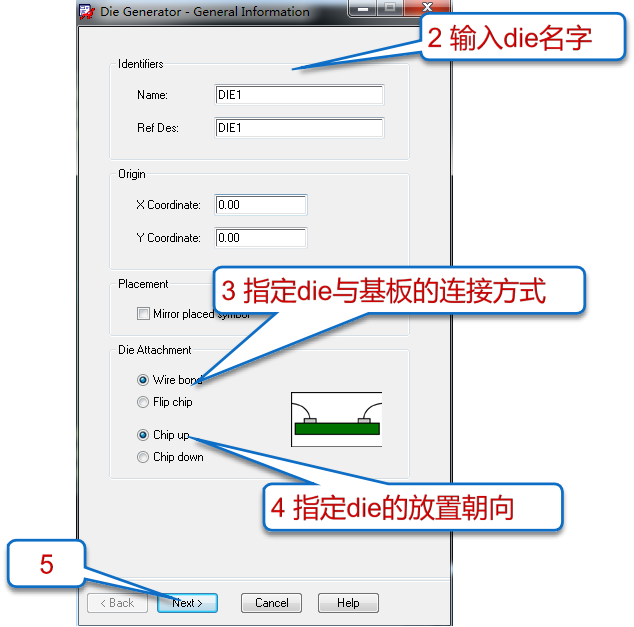

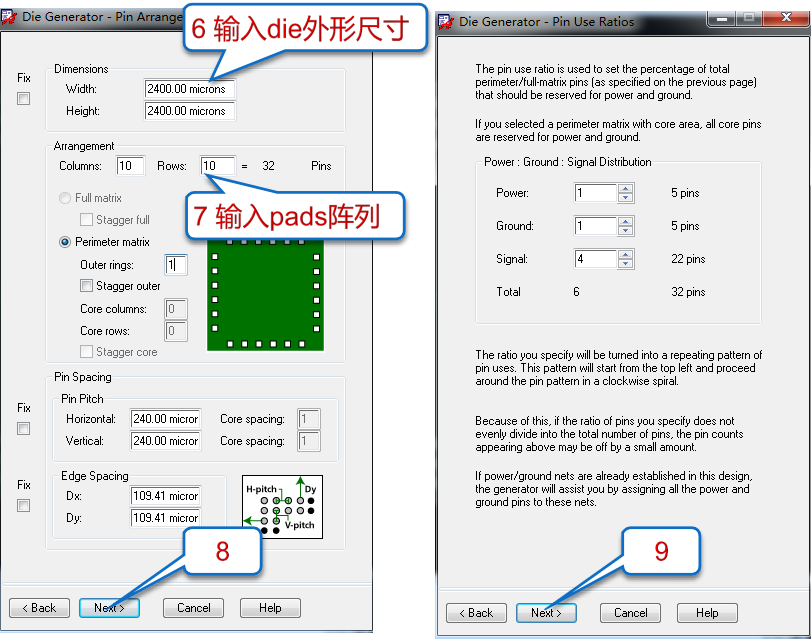

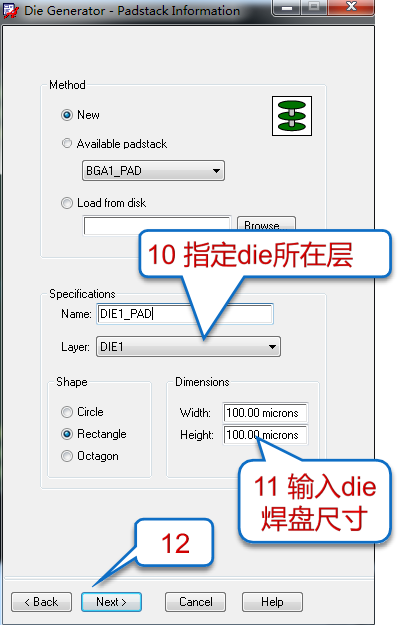

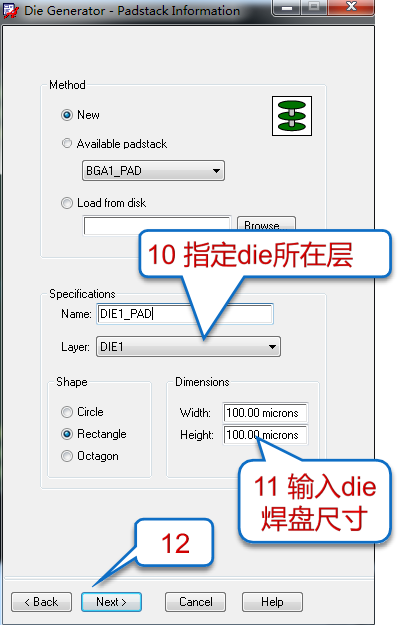

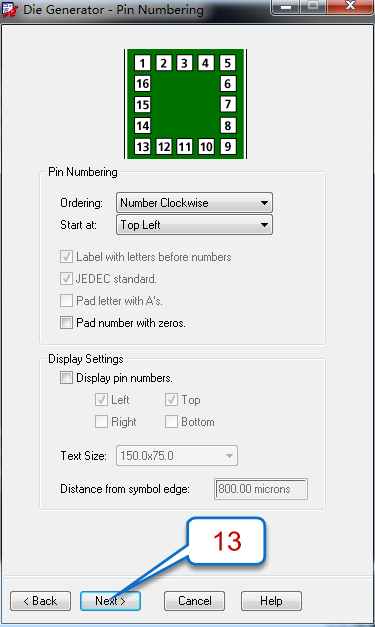

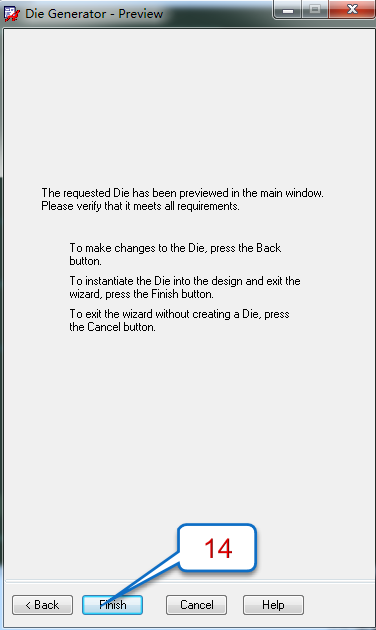

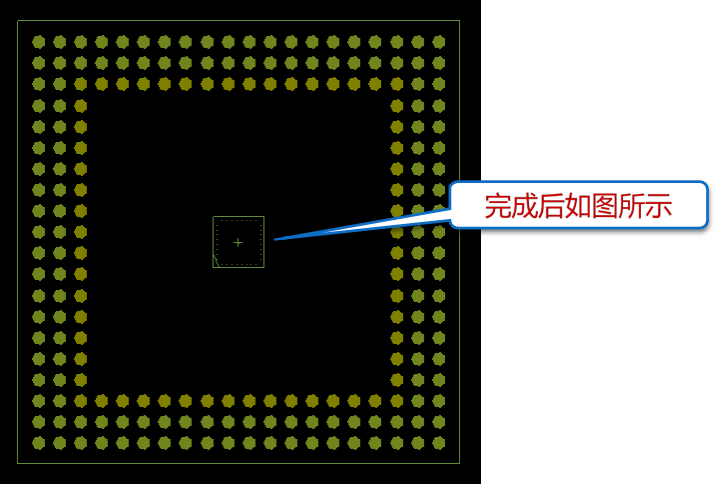

导入Die(DieGenerator方式)

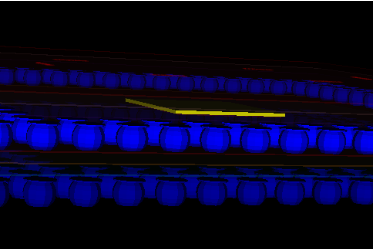

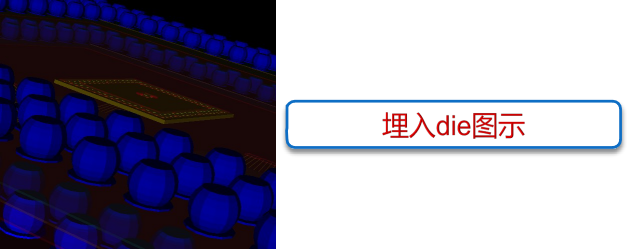

将Die调整为嵌入式

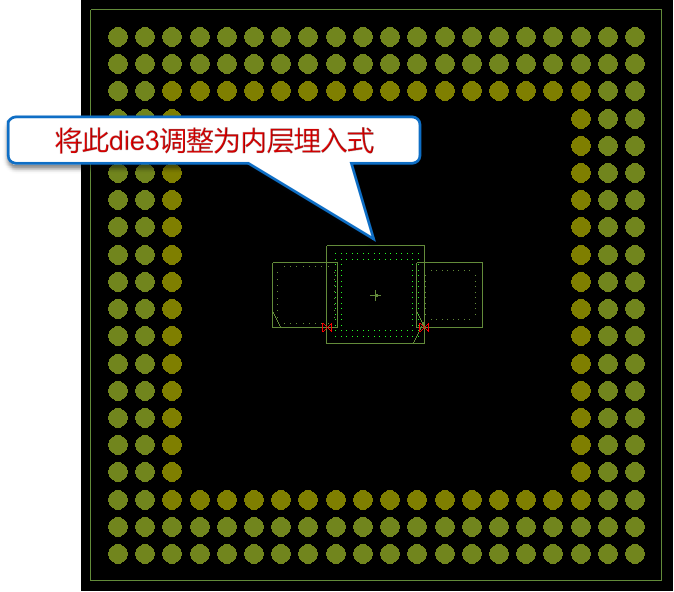

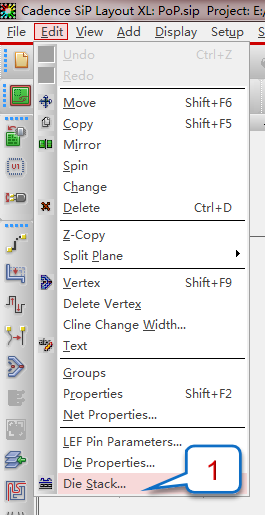

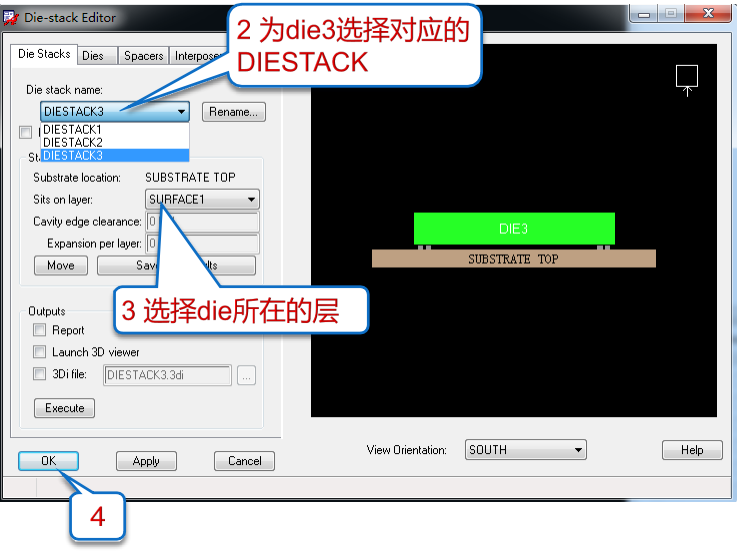

将Die3调整为内层埋入式

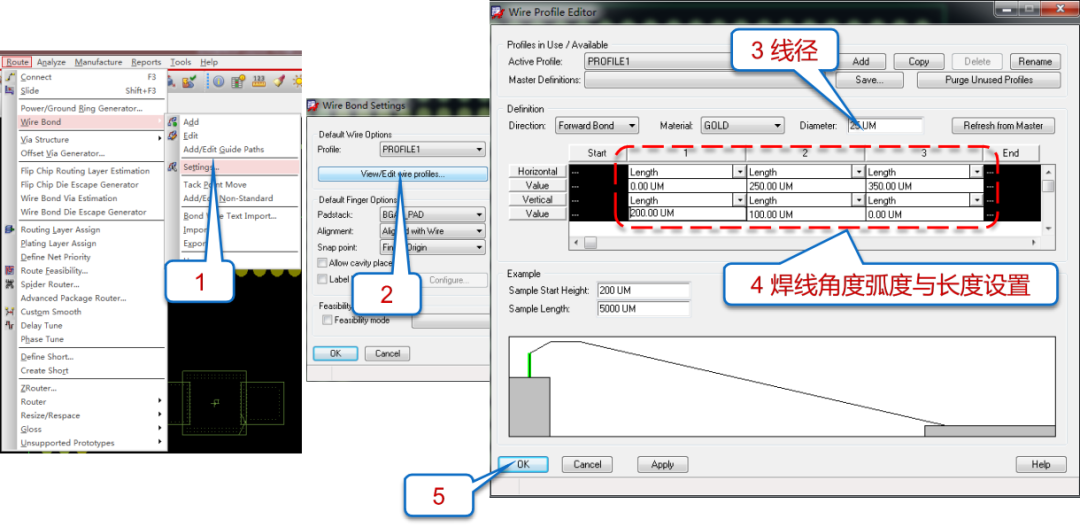

设置wirebond profile

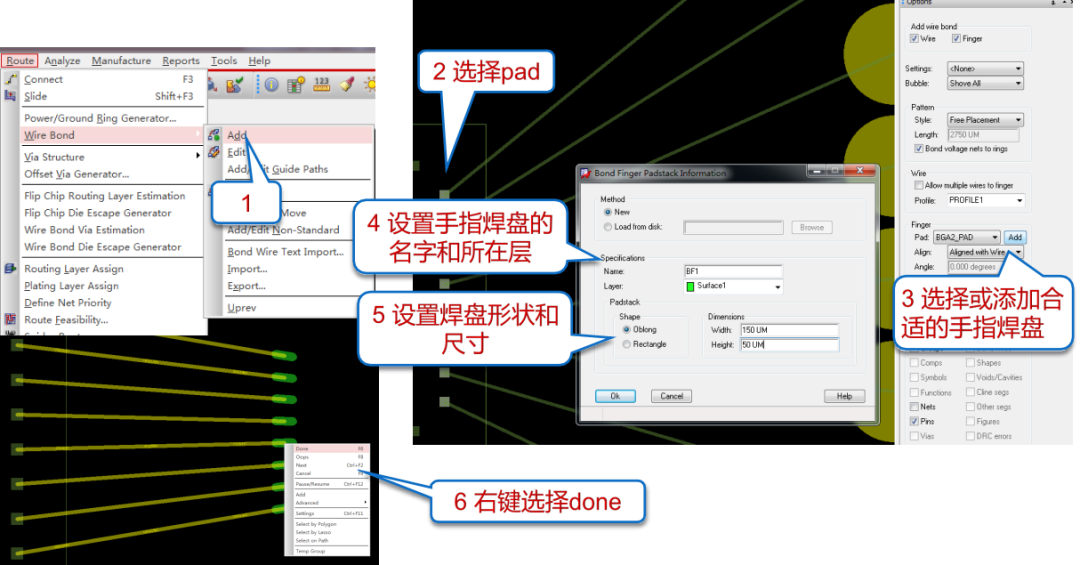

增加标准式焊线(Standard)

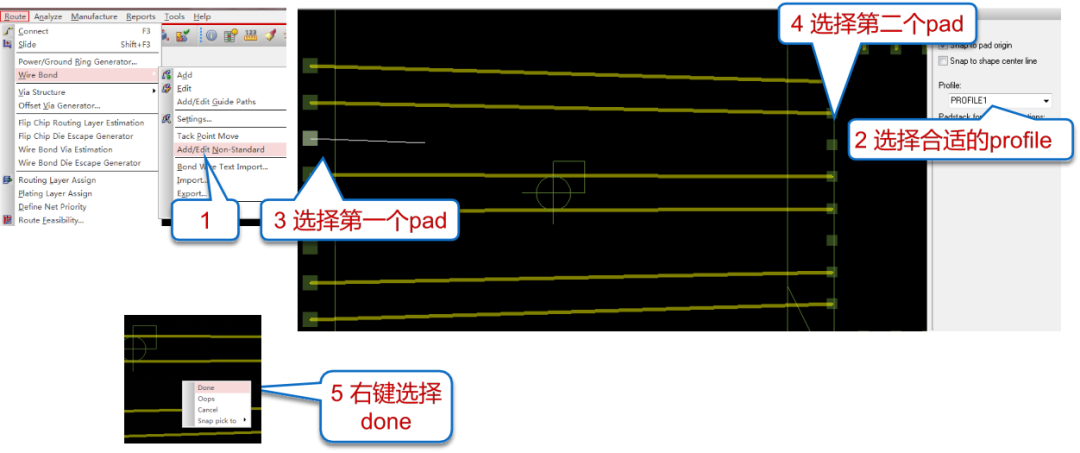

增加非标准式焊线(Non-Standard)--适合pad to pad或多根焊线连接

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

SiP

+关注

关注

6文章

543浏览量

108002 -

Layout

+关注

关注

15文章

424浏览量

75425 -

POP封装

+关注

关注

0文章

7浏览量

5287

原文标题:【技术指南】如何使用 SIP Layout 建立 PoP 封装结构

文章出处:【微信号:封装与高速技术前沿,微信公众号:封装与高速技术前沿】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

一文看懂SiP封装技术

的出现,对触控模组的处理能力和性能提出了更高的要求,其复杂结构要求触控芯片采用SiP组装,触觉反馈功能加强其操作友好性。指纹识别同样采用了SiP封装。将传感器和控制芯片

发表于 09-18 11:34

第一次发帖。这种三维封装堆叠用SIP Layout模块要怎么画呢?求个教程或者手册什么的。

Cadence SiP Layout为SiP设计提供了约束和规则驱动的版图环境。它包括衬底布局和布线、IC、衬底和系统级最终的连接优化、制造准备、整体设计验证和流片。该环境集成了IC/封装

发表于 06-06 19:43

系统级封装(SiP)的发展前景(上)

与扩大。其中也应该包括如何降低高连接线密度基板材料的成本;开发EDA设计工具;开发SiP电特性与机械特性的高速计算机模拟工具并使之与IC设计工具相连接;研究开发晶圆级

发表于 08-23 07:38

嵌入式存储封装技术SiP/SOC/MCP/PoP的区别是什么

成本以及拥有/减小成本。如何解决这些问题呢?层叠封装(PoP)的概念逐渐被业界广泛接受。PoP(Packaging on Packaging),即堆叠组装,又称为叠层封装。

发表于 12-27 07:43

SIP封装和采用SiP工艺的DFN封装是什么

ZLG致远电子新推出的电源隔离芯片采用成熟的SiP工艺与DFN封装,相比传统SIP封装体积缩小75%,性能和生产效能也有所提升。本文为大家分享传统S

SiP主流的封装结构形式

SiP封装(System In Package系统级封装)是将多种功能芯片,包括处理器、存储器等功能芯片集成在一个封装内,从而实现一个基本完整的功能,与SOC(System On Ch

单列直插式封装(SIP)原理

SIP封装并无一定型态,就芯片的排列方式而言,SIP可为多芯片模块(Multi-chip Module;MCM)的平面式2D封装,也可再利用

发表于 10-08 15:13

•3431次阅读

如何使用SIP Layout建立PiP封装结构

PiP封装结构 将要创建的元件参数如下: 1、共有2颗die,上方的封装基板正面放置1颗,Wireband连接形式;下方基板正面放置1颗,Flipchip连接形式; 2、共有两个封装

利用SIP Layout工具构建PoP封装结构的方法

利用SIP Layout工具构建PoP封装结构的方法

评论