与同类FPGA相比,Agilex 7 FPGA可为OpenCores公开发布的设计提供超过一个速度等级的内核性能提升。

简 介

本文介绍了一种对Agilex 7 FPGA产品家族的内核性能进行基准测试的方法,旨在清晰地展示相关方法和数据,以便感兴趣的读者可以重新生成和分析这些结果。

背景:FPGA和SoC的基准测试

当前,可编程逻辑行业尚无标准的指标评测方法。为此,使用了严格的内部分析,并广泛地采用了不同的设计组合,以充分了解、量化可编程逻辑产品相比前代产品/行业同类产品的性能。这些设计从不同的细分市场收集而来,包括高性能计算、图像和视频处理、有线和无线通信以及消费类产品等。此外,这些设计还使用了多种实施技术,包括来自行业同类产品的ASIC和FPGA。通过使用广泛的设计套件,致力于确保结果准确无误,且能够代表客户设计与Quartus Prime Software Suite等FPGA设计工具之间的复杂交互。为了使用客户设计,已在转换设计方面投资了大量资源,以便能够与广泛的合成工具和电子设计自动化(EDA)厂商合作。同时还确保功能予以保留,并针对特定FPGA厂商进行了适当的代码优化,这点是必需的,因为开发设计时通常会针对特定FPGA对设计进行优化。

在性能比较方面,采用的是尽力而为法,目的是显示可实现的最佳结果。尽力而为编译方法实验需要比默认按钮(push-button)编译更长的单独编译时间,而且,在该方法中,每项设计需要进行超过一次的编译。

借助这种方法,确定了Agilex 7 FPGA和SoC可提供比7纳米FPGA行业同类产品更高的内核性能,测量指标为在设计套件的每项设计中,针对速度关键型时钟路径所能实现的最大fMAX。

性能差异在13%-25%左右(具体数据取决于不同的设计),大约相当于一个或两个速度等级优势,一个速度等级通常被定义为10%-15%†的性能差异。这些结果有力证明了Agilex 7 FPGA作为最高性能10纳米FPGA产品家族的地位。然而,由于这些结果是专有设计获得的,所以只能就这项分析分享有限的详情,这最终会限制这些信息对可编程逻辑用户的有用性。

通过基于OpenCores的性能比较提高透明度

为了克服在理解可编程逻辑性能方面的挑战,使用已发布的OpenCores(www.opencores.org)设计进行指标评测。OpenCores提供了开源硬件知识产权(IP)内核。这项指标评测旨在帮助可编程逻辑用户:

了解性能评估过程中使用的具体设计,包括这些设计具体到寄存器传输级(RTL)描述的详细信息

自己重新生成分析结果

仔细查看分析结果,以更好地了解Agilex 7 FPGA性能和器件利用率,以及这些性能优势对于特定设计的意义

这项基于OpenCores的分析的范围小于使用的内部分析,因为前者专注于受时间约束的比较。分析并不全面,但分析结果说明了实施相似设计,或实施与设计示例套件所用功能相似的功能设计时,Agilex 7 FPGA相比行业同类器件的相对性能。

OpenCores标记方法

OpenCores设计只使用了目标设备中的一小部分资源,只使用这一小部分资源并非用户的惯例,也达不到他们所期望的目标。此外,随着设备资源逐渐被耗尽,以及设计变得更难以放置和路由,不断增加的利用率通常会对可实现的最高fMAX产生不利影响。为了模拟设备利用率对可编程逻辑性能的影响,OpenCores设计执行了大量编译,而且每次都会在前一次编译的基础上添加更多OpenCores实例。为了增加可编程逻辑设备的设计尺寸,每项OpenCores设计都在FPGA中重复进行了实例化(对同一内核进行多次标记):

每次标记都并行实施

添加I/O包装程序逻辑以减少更大设计所需的I/O引脚数

内核与包装程序逻辑之间不存在时间关键路径

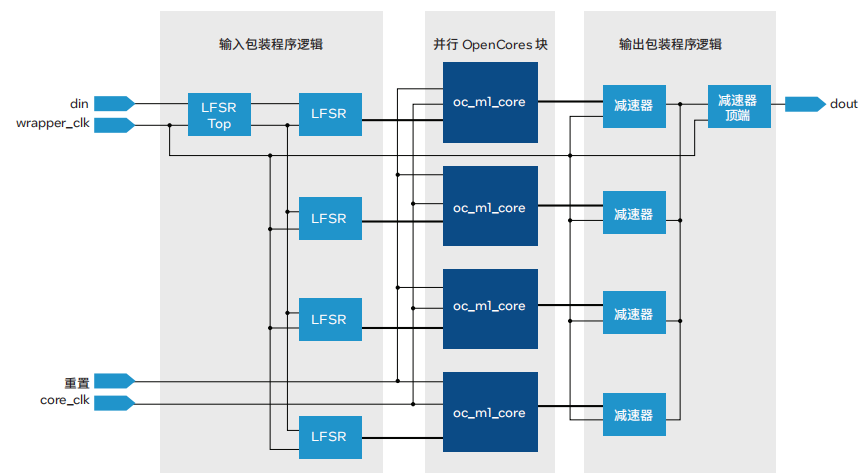

包装程序逻辑提供了尽可能少的开销。图1显示了标记过程

图1. 在FPGA中对oc_m1_core设计进行了四次实例化

OpenCores标记和基准测试方法

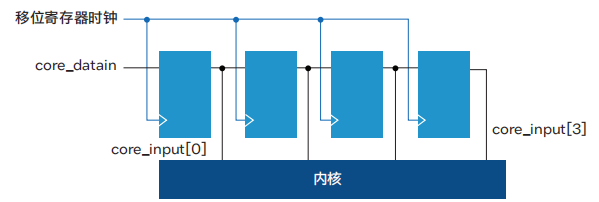

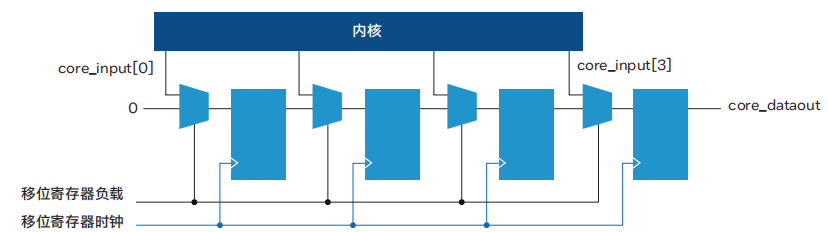

随着OpenCores设计标记数量增加(因此设计尺寸不断增加),I/O引脚和全局时钟等资源变得有限。为了避免引脚用尽,每个OpenCores设计都包裹在移位寄存器中,以便一个物理引脚能够为内核的所有输入引脚提供信息,以及内核的所有输出引脚都将信息输入到可加载的移位寄存器中。图2和图3分别显示了输入和输出移位寄存器。移位寄存器尺寸取决于I/O引脚数量,移位寄存器的数量取决于FPGA中实施的OpenCores设计数量。

图2. 输入移位寄存器实施

图3. 输出移位寄存器实施

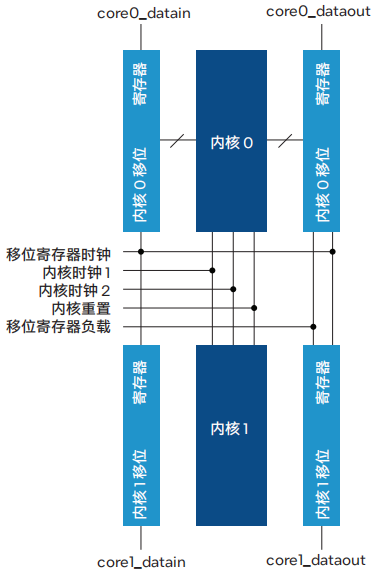

为了避免全局时钟资源耗尽,一个引脚直接为所有OpenCores设计提供全局时钟和重置信号。例如,如果一个内核需要两个时钟(即内核时钟1与内核时钟2)以及一个重置信号,内核时钟1的所有实例由一个引脚提供,内核时钟2的所有实例由另一个不同的引脚提供,重置信号的所有实例由第三个引脚提供。借助该方法,所有OpenCores设计都拥有相同的时钟和重置信号(请参见图4)。

图4. 共享时钟和重置信号的双核实施

在FPGA中,包装程序逻辑将所有OpenCores设计相连接后,为确保包装程序逻辑(即移位寄存器)和OpenCores设计之间不存在关键路径。为了实现这一目标,创建了错误的路径,同时通过为内核时钟和包装程序逻辑时钟设置不同的无关时钟域,消除了时间路径。然后,这些设计工具可将内核和移位寄存器分开优化。在设备和设计工具允许的情况下,对OpenCores设计进行了尽可能多的实例化,且无编译错误。

软件工具、设置与约束

为了开展这项研究,使用了分析时可用的所需FPGA开发工具的最新版本:

Quartus Prime Software Suite版本22.4

把工具安装并运行于Linux64设备之上。这些可编程逻辑工具提供的设置在设计性能、逻辑资源使用、编译时间和内存使用之间进行了折中。需要注意的是,某些设计可能使用特定设置生成最佳结果,但这并不意味着该设置适用于另一项设计。此外,用于指引EDA工具的用户约束可改善结果。即便使用代表客户设计的设计集,指标评测结果也会因软件设计和应用约束的不同而存在显著差异。对于本文介绍的比较,使用了尽力而为的编译模式,并设置了较为严格的时间约束。为了确定每项设计的严格时间约束,对每个OpenCores设计时钟应用了频率约束,以确定每个时钟刚好无法满足的约束。通过不断增加约束直至无法满足,确定了基础约束。然后,通过将基础约束值乘以最少1.3的系数,确定了严格约束。下面部分介绍了为每项设计应用的约束。

结 语

Agilex 7 FPGA家族实现了更高的fMAX值,范围在3%到41%之间,几何平均值为20%。性能优势相当于一到两个速度等级。此外,结果表明,在利用率较高的情况下,Agilex 7 FPGA性能稳定性更好,在这种情况下,Hyperflex 架构能提供更高的性能,让您可以更充分地利用可用逻辑。

-

FPGA

+关注

关注

1655文章

22283浏览量

630181 -

寄存器

+关注

关注

31文章

5588浏览量

129051 -

内核

+关注

关注

4文章

1436浏览量

42489 -

soc

+关注

关注

38文章

4514浏览量

227590 -

Agilex

+关注

关注

0文章

26浏览量

3979

原文标题:Agilex ™ 7 FPGA在OpenCores中展示性能优势

文章出处:【微信号:英特尔FPGA,微信公众号:英特尔FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

深度解读:Intel最新的FPGA Agilex

英特尔Agilex FPGA家族全系列概述表

全新英特尔Agilex D系列FPGA和SoC适用于中端FPGA应用

全新英特尔® Agilex™ FPGA 和 SoC 家族产品解析

英特尔® Agilex™ D系列FPGA和SoC适用于中端FPGA应用

BittWare提供基于英特尔Agilex™ 7 FPGA最新加速板

将AFE7769DEVM与Hitek Agilex eSOM7 FPGA连接

Altera Agilex 7 M系列FPGA正式量产出货

Altera Agilex 3 FPGA和SoC产品介绍

利用英特尔Agilex FPGA应对PQC与CRA挑战

Agilex 7 FPGA和SoC的基准测试

Agilex 7 FPGA和SoC的基准测试

评论