电子发烧友网报道(文/吴子鹏)随着摩尔定律速度放缓,近几年先进封装技术成为大算力芯片发展的主要推动力。得益于人工智能应用的算力需求爆发,芯片封装技术的重要性更是提升到了前所未有的高度。

在第十六届集成电路封测产业链创新发展论坛(CIPA2024)上,来自封装和设备行业的众多专家分享了产业前沿信息,包括国产封装厂商在先进封装方面的进展,先进封装里前沿的创新技术,以及先进封装如何更好地赋能大算力芯片的发展等。

国内先进封装技术的具体进展

从传统的引线框架封装,到球栅阵列封装(BGA)、陶瓷基板封装(CBGA)、面积阵列封装(LGA)等,再到2.5D/3D封装、系统级封装(SiP)、Chiplet等,产业界努力的方向就是在一个封装内塞进更多的功能单元,以实现更高的集成度。近几年,先进封装技术一直由台积电、英特尔、三星三大海外大厂主导,不过随着需求暴涨,国产封装大厂也在先进封装方面取得了积极的进展。

CIPA2024上,国内长电科技、通富微电、华天科技、华进半导体等均做了分享,也提到了各自企业在先进封装层面的进展。比如,华天科技(昆山)电子有限公司技术专家付东之分享了华天科技在先进封装方面所取得的成果。

华天科技(昆山)电子有限公司技术专家付东之

目前,华天科技的主要业务范围是封装设计、封装仿真、引线框封装、基板封装、晶圆级封装、晶圆测试及功能测试、物流配送等。华天科技先进封装平台的名字是Hmatrix,包括WLP(WaferLevelPackage)、SLP(StripLevelPackage)和eSinC(EmbeddedSysteminChip)。在这个体系下,华天科技也取得了一些成绩,比如在晶圆级封装WLP方面,华天科技拥有国内最大的WLP生产线,月产能达到3万多片。

另外,华天科技基于3DMatrix3D晶圆级封装平台开发的系统集成封装技术eSinCSiP,通过集成硅基扇出封装、bumping技术、TSV技术、C2W和W2W技术,可以实现多芯片高密度高可靠性3D异质异构集成。付东之称,华天科技也在布局2.5D封装技术。

华进半导体封装先导技术研发中心有限公司总经理孙鹏则在《后摩尔定律时代AI/HPC封装集成解决方案》分享里提到了华进半导体PDK(ProcessDesignKit,工艺设计套件)+EDA的先进封装设计流程和先进封装仿真技术。PDK是制造和设计之间沟通的桥梁,是模拟电路设计的起始点。孙鹏强调,要实现先进封装,需要先有PDK。

华进半导体封装先导技术研发中心有限公司总经理孙鹏

孙鹏表示,在AI/HPC芯片设计里,芯片的电压并不高,可能是1.2V,也可能是0.7V,但是负载电流是非常恐怖的,能够达到几百个安培。为了保证系统给芯片供电电压的稳定性,直流压降、交流纹波和电源阻抗等需要在设计前期就考虑到。同时,先进封装里芯片、封装与系统层级之间的电磁、热、力场的耦合干扰越来越显著,系统性的SI/PI和热机械失效问题也要提前考虑。

孙鹏强调,之所以说电源完整性在以先进封装技术打造的AI/HPC芯片里,其重要性可能比信号完整性更加重要,原因就是芯片内流转的电流太大了。华进半导体的PDK+EDA方案可以实现跨芯片-封装-系统的协同设计以及跨电学、热学、力学的综合分析,支撑2.5D/3DIC产品的规划、设计、验证和签核,以实现更好的先进封装。

另外,华进半导体实现的先进封装技术成果还包括:

·华进2.5D封装方案实现最大32Gbps速率的信号传输,可满足通道无源电性能RL(回损)、IL(插损)、PSXT(综合功率串扰)、ICR(综合串扰比)等4项约束;

·开发了基于low-K有源晶圆的正面Via-lastTSV加工技术,TSV10umx100um,bump高度80um,解决了low-K材料刻蚀和吸水性保护、高bump结构晶圆的切割等技术难题;

·3DChiplet结构实现了4颗网络处理芯粒、被动元件、有源TSV转接板和基板,相比基板上集成电源的方案,模块减少~84%的焦耳热损耗,TSV路径的最大电流密度减小~60%;

·在国内建成国产扇出封装中试线,支持RDL-FirstFO封装工艺,涵盖高密度布线及微节距凸点、C2W组装、激光临时键合/拆键合等相关工艺。

先进封装里面的前沿技术创新

先进封装是一个交叉融合的技术创新领域,涉及设计、环境、测试、材料、制造和可靠性等多学科领域。从芯片架构来看,先进封装关乎异构集成、互联技术、供电技术和安全技术等诸多方面。在CIPA2024上,也有非常多的嘉宾分享了先进封装中的前沿技术。

比如,江苏微导纳米科技股份有限公司半导体资深销售总监聂佳相分享了《低温镀膜工艺在半导体封测中的应用》,并介绍了微导纳米的先进封装薄膜解决方案。聂佳相称,摩尔定律本身就是一个物理极限,可能在1nm或者某个节点就无法进行下去了,先进封装便成为突破芯片性能瓶颈的最佳路径。而在先进封装中,TSV、背覆铜和混合键合都和镀膜技术息息相关。

江苏微导纳米科技股份有限公司半导体资深销售总监聂佳相

比如在混合键合HybridBonding中,除了铜层之间完成键合实现电气连接,两个Chip面对面的其他非导电部分也要贴合,这就需要使用CVD设备将铜填补进去完成键合。这个过程中存在两大挑战:其一是需要在低温环境下完成;其二是高分子材料的翘曲问题通常比较严重。

微导纳米作为国内排名靠前的薄膜设备供应商,设备类型主要集中在CVD和ALD两大类型,能够帮助封装厂商完成难度较大的低温工艺。比如,该公司的iTomic®HiK系列原子层沉积镀膜系统,适用于客户制程高介电常数(High-k)栅氧层、MIM电容器绝缘层、TSV介质层等薄膜工艺需求。

再比如,江苏华海诚科新材料股份有限公司董事陶军分享了《先进半导体封装材料及未来趋势》。在制程技术上,先进封装采用如微细化焊球、超低k材料等创新技术,因此材料创新对于先进封装而言是极其重要的。

江苏华海诚科新材料股份有限公司董事陶军

陶军主要谈到了铜线键合中的一些材料发展。在键合的过程中,如果基板或者塑封材料的pH值不合适,就可能对铜线造成腐蚀。这个过程中,氯离子的含量是非常关键的,会影响基板和塑封材料的pH值,进而影响键合和封装的效果。举例来说,当pH值为4时,键合的失效率就会非常高。

为了解决这个问题,华海诚科和很多半导体材料供应商进行合作,取得的成果包括:特殊含硅结构的环氧树脂,用陶瓷在塑封材料中替代金属,建立了一条无金属产线;用颗粒状塑封料来实现大面积封装,降低基板的翘曲问题;调节数字体系结构,将含硅环境的环氧结构和特殊的环氧结构进行融合,也能够应对翘曲的问题。

国产Chiplet如何赋能大算力芯片发展

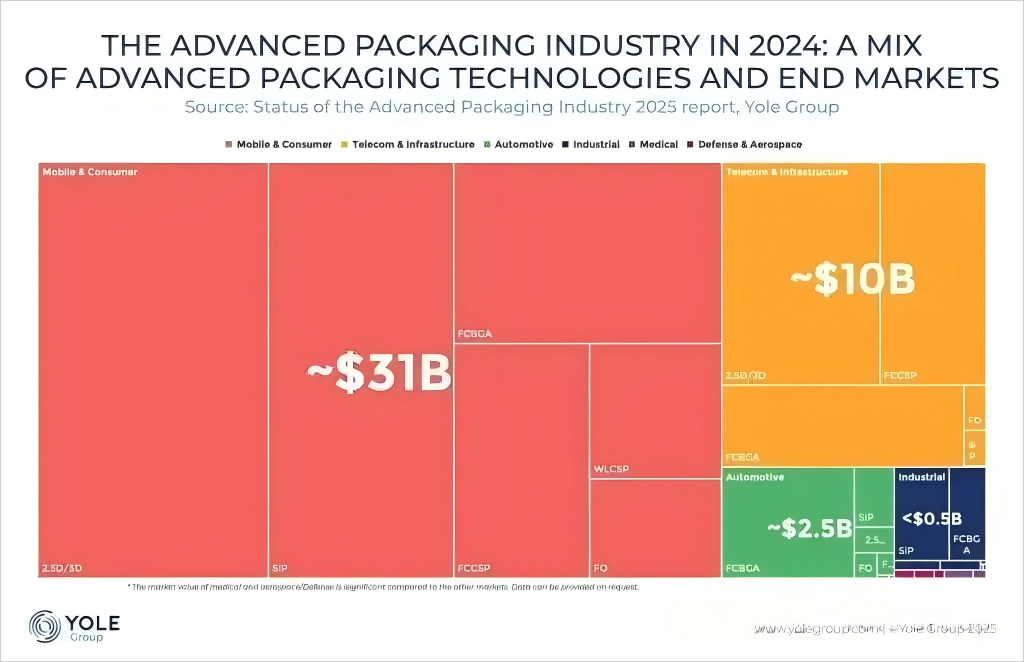

先进封装的研发和创新,最终还是落到应用上,也就是打造大算力芯片。根据Yole的统计数据,到2027年,预计2D/3D封装市场规模将达到150亿美元,扇出型WLP约为40亿美元,扇入型约为30亿美元,Embedded约为2亿美元。届时,先进封装将占整体封装市场的50%。

在CIPA2024上,锐杰微科技集团董事长方家恩分享了《Chiplet封装技术在封装级的相关应用》,主要探讨了国内如何发展2.5D封装技术以及Chiplet技术的落地。方家恩认为,受限于先进制程和HBM工艺不成熟,目前国内虽然出现了几十甚至上百家的2.5D封装企业,但产业发展仍处于早期阶段,尤其是缺少经过验证的经验。在这种情况下,国内应该如何用好Chiplet技术呢?

锐杰微科技集团董事长方家恩

方家恩指出,Chiplet技术发展受限于三点,一个是先进工艺和IP,一个是互联标准,还有一个是封装技术。在传统芯片设计里,一颗芯片可能对应两款封装。不过,在未来打造各种功能die时,研发一颗die可能需要适配十几种,甚至是二十几种封装类型,因此是封装引领Chiplet技术发展。未来几年,国产的Chiplet将迎来蓬勃的发展,年复合增长率可能高达50%以上。

方家恩强调,国产要形成自己的Chiplet生态链,这是非常重要的,也是值得大家思考和努力的。

为了实现这一点,国产芯片产业可以从几个方面入手:首先是标准方面,要拥有自己的Chiplet互联标准,目前《芯粒间互联通信协议》(ChipletsInterconnectProtocol,CIP)已经获批,并于今年1月1日正式实施;其次是先进封装技术,跳脱出国外主导的先进封装路线,基于传统封装和Chiplet也能够解决80%以上应用场景对高性能芯片的需求。

目前,国产芯片在同构D2D方面已经取得了一定的进展,也就是将计算SoC分拆成2个、4个或者6个,然后将其拼起来以实现更高的计算性能。然后就是异构的,将不同的计算单元以及HBM融入高性能计算芯片中,这方面台积电的CoWoS是非常值得借鉴学习的。

方家恩在演讲中提到,国内Chiplet要想发展好,两个全流程是非常重要的。其一是工艺全流程,解决前道和后道所有工艺问题以实现全流程;其二是开发全流程,在设计开发过程中对电、热、应力、可靠性等方面做到周全地考虑。

结语

先进封装是未来打造高算力芯片的重要技术,意味着先进的设计思路和先进的集成工艺。在国内,受限于先进工艺制程方面的影响,目前台积电、英特尔和三星的技术路线并不适用于国产先进封装技术的发展,国内芯片产业需要走出自己的路。比如在Chiplet领域,要率先实现工艺全流程和开发全流程,同时也要有自己的标准,形成自己的生态,才能够逐渐做大做强。

-

封装

+关注

关注

128文章

9333浏览量

149053 -

算力

+关注

关注

2文章

1676浏览量

16833 -

先进封装

+关注

关注

2文章

563浏览量

1062

发布评论请先 登录

AI时代算力瓶颈如何破?先进封装成半导体行业竞争新高地

华为领衔,三剑客入局!十万卡智算集群落地,国产算力芯片强势崛起

算力爆发时代IP设计面临哪些新挑战

对话飞凯材料 | 锚定先进封装核心赛道,支撑AI算力增长

国产AI芯片真能扛住“算力内卷”?海思昇腾的这波操作藏了多少细节?

安世事件警示录:当先进封装设备成为AI算力新战场

国产芯片的崛起:机遇与挑战并存

RISC-V架构下AI融合算力及其软件栈实践

大算力浪潮下,国产先进封装技术取得了怎样的成绩?面临怎样的挑战?

大算力浪潮下,国产先进封装技术取得了怎样的成绩?面临怎样的挑战?

评论