来源:中国科学院微电子研究所

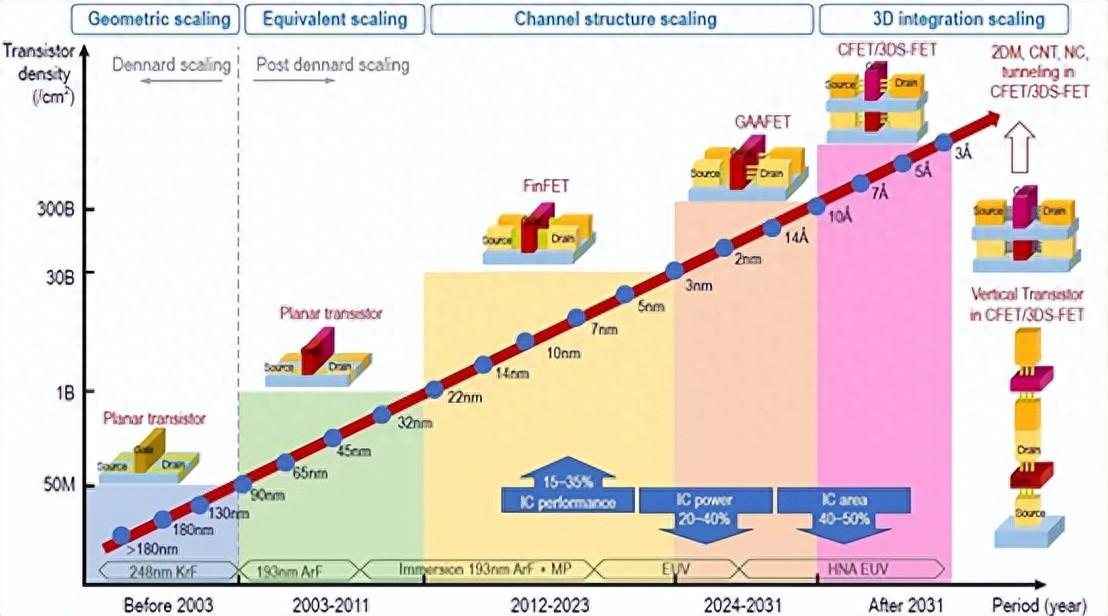

金属-氧化物-半导体场效应晶体管(MOSFET)是推动大规模CMOS集成电路按照“摩尔定律”持续微缩并不断发展的核心器件。近十几年,为突破更小技术节点下的微缩挑战,晶体管结构创新成为了技术发展的主要路径,从平面晶体管演进到鳍式场效应晶体管,再到最新3nm技术节点下的堆叠纳米沟道全环绕栅极FET(GAAFET),通过晶体管内部沟道的全三维化以获得更好的短沟道栅控能力与同尺寸导电性能。在1nm技术节点附近,因为MOSFET栅控能力无法进一步提升、内部Si基导电沟道临近载流子传输量子效应限制边界,传统摩尔定律所描述的尺寸缩减不再预期有效,晶体管结构创新将迈入更进一步的晶体管垂直三维堆叠。

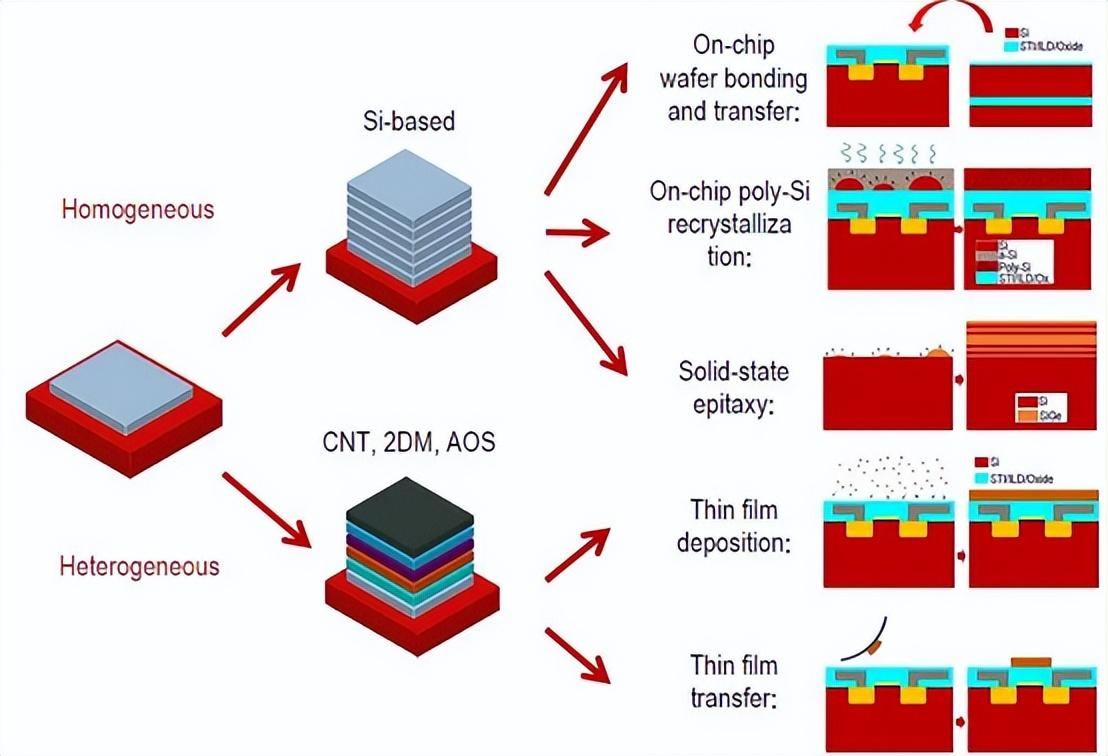

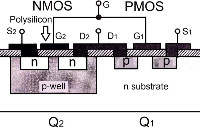

近日,中国科学院微电子研究所集成电路先导工艺研发团队在中国科学杂志社的《国家科学评论》(National Science Review,NSR)在线发表了关于先进CMOS集成电路新结构晶体管的综述文章“New structure transistors for advanced technology node CMOS ICs”(《用于集成电路的新兴材料和晶体管》专题论文之一),并入选期刊封面论文。该文从最新的GAAFET所面临的关键技术挑战出发,针对1nm技术节点下集成电路持续发展的集成密度需求,介绍了实现晶体管垂直三维堆叠的主要途径,包括上下垂直互补FET(也称3D堆叠FET)和垂直沟道晶体管,总结了实现晶体管三维堆叠的单次与顺次集成路径和工艺方法、所需的创新工艺、材料(低温外延硅、碳纳米管、二维材料等)以及协同设计技术,分析了面向大规模集成应用的关键工艺、电路设计及内部散热挑战,展望了未来进一步与其它新原理晶体管及3D芯片与系统结合的综合发展可能。

中国科学院微电子研究所张青竹研究员、张永奎高级工程师为论文第一作者,殷华湘研究员为论文通讯作者。

全文链接:

https://doi.org/10.1093/nsr/nwae008

集成电路中MOSFET持续创新发展路径

晶体管三维堆叠中的不同沟道材料选择与方法

声明:本网站部分文章转载自网络,转发仅为更大范围传播。 转载文章版权归原作者所有,如有异议,请联系我们修改或删除。

审核编辑 黄宇

-

晶体管

+关注

关注

78文章

10282浏览量

146464 -

场效应晶体管

+关注

关注

6文章

401浏览量

20377 -

微电子

+关注

关注

18文章

405浏览量

42628 -

CMOS集成电路

+关注

关注

4文章

41浏览量

14635

发布评论请先 登录

CMOS集成电路中闩锁效应的产生与防护

多值电场型电压选择晶体管结构

中国集成电路大全 接口集成电路

多值电场型电压选择晶体管结构

硬件基础篇——TTL与CMOS电平

数字集成电路 Verilog 熟悉vivado FPGA微电子、电子工程

微电子所在超宽带低噪声集成电路设计领域取得新进展

微电子所在《中国科学:国家科学评论》发表关于先进CMOS集成电路新结构晶体管的综述论文

微电子所在《中国科学:国家科学评论》发表关于先进CMOS集成电路新结构晶体管的综述论文

评论