据4月26日网友Izzukias分享的一份114页AMD官方文件确认,将于明年发布的Zen 5 APU具有强大性能,Strix Halo APU将运用多芯粒(Chiplet)设计,其内嵌的40个CU(即20xWGP)超越了现今主流独立显卡。

文件进一步夯实之前的曝料,AMD Zen 5 APU将包含常规版Strix Point和增强型“大杯”Strix Halo两款产品。

Strix Point

常规版Strix Point将保持单芯片设计,但核心数量从8核16线程的Zen 4提升至12核24线程的Zen 5,核显部分由12个RDNA 3.1 CU增至16个RDNA 3.5 CU,NPU运算能力提高至50 TOPS,功耗范围在45W~65W之间。

“大杯”Strix Halo

Strix Halo APU则更加强劲,采用多芯粒设计,搭载两个8核心Zen 5芯片,共计16核32线程,同时配备40个RDNA 3.5 CU核显,相较之下,AMD RX 7600 XT独显仅有32个CU。

厂家表示,Strix Halo的GPU性能堪比RTX 4060 Laptop,NPU运算能力最高可达60 TOPS。Strix Halo APU的官方TDP设定为70W,但厂家可根据设备散热设计进行调整,最大可达130W以上。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

芯片

+关注

关注

463文章

54494浏览量

469903 -

amd

+关注

关注

25文章

5713浏览量

140484 -

线程

+关注

关注

0文章

511浏览量

20878

发布评论请先 登录

相关推荐

热点推荐

英伟达+联发科,打入游戏本市场?

合作,通过更低的功耗,实现RTX 4070同级的性能,并搭载在更轻薄的机身内。 APU(Accelerated Processing Unit,加速处理单元)是AMD推出的一种处理器架构概念,主要理念是

芯粒设计与异质集成封装方法介绍

近年来,芯粒设计与异质集成封装技术受到了行业内的广泛关注,FPGA(如赛灵思与台积电合作的Virtex系列)、微处理器(如AMD的EPYC系列、英特尔的Lakefield系列)等产品,均借助芯

Cadence工具如何解决芯粒设计中的信号完整性挑战

在芯粒设计中,维持良好的信号完整性是最关键的考量因素之一。随着芯片制造商不断突破性能与微型化的极限,确保组件间信号的纯净性与可靠性面临着前所未有的巨大挑战。对于需要应对信号完整性与电源完整性复杂问题的工程师而言,深入理解这些挑战

UCIe协议代际跃迁驱动开放芯粒生态构建

在芯片技术从 “做大单片” (单片SoC)向 “小芯片组合” (芯粒式设计)转型的当下,一套统一的互联标准变得至关重要。UCIe协议便是一套芯粒芯片互联的 “通用语言”。

面向芯粒设计的最佳实践

半导体领域正经历快速变革,尤其是在人工智能(AI)爆发式增长、对更高处理性能及能效需求持续攀升的背景下。传统的片上系统(SoC)设计方案在尺寸与成本方面逐渐触及瓶颈。此时,Multi-Die设计应运而生,将SoC拆分为多个称为芯

借助Arm芯粒技术构建计算未来

在我们近期与业界伙伴的多次交流中,明显发现芯粒时代的大幕已徐徐拉开,行业已经不再抱存对芯粒的质疑态度,而是正在合作解决如何借助芯

芯粒技术的专利保护挑战与应对策略

本文由TechSugar编译自SemiWiki在半导体行业中,许多产品由独立制造和分销的组件组装而成,这一特点为商业专利保护带来了特殊考量。而芯粒(Chiplet)的出现,则打破了这种传统模式,它所

【「AI芯片:科技探索与AGI愿景」阅读体验】+半导体芯片产业的前沿技术

MI300,是AMD首款数据中心HPC级的APU

③英特尔数据中心GPU Max系列

3)新粒技术的主要使用场景

4)IP即芯粒

IP即

发表于 09-15 14:50

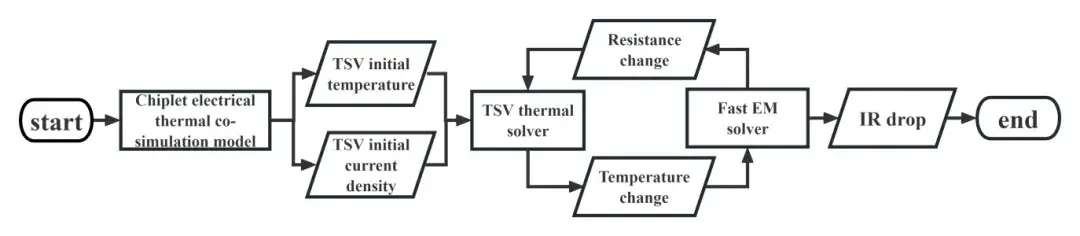

微电子所在芯粒集成电迁移EDA工具研究方向取得重要进展

随着高性能人工智能算法的快速发展,芯粒(Chiplet)集成系统凭借其满足海量数据传输需求的能力,已成为极具前景的技术方案。该技术能够提供高速互连和大带宽,减少跨封装互连,具备低成本、高性能

从Ascend 910D看芯粒创新,半导体行业将迎重大变局

性能的提升。在此背景下,无论是深耕行业多年的老牌企业,还是新入局的创新力量,都积极推出基于先进封装理念的产品与方案,以此作为提升计算能力的关键路径。 今年 6月 华为 凭借Ascend 910D这款基于芯粒的AI处理器设计引

江波龙企业级DDR5 RDIMM率先完成AMD Threadripper PRO 9000WX系列兼容性认证

2025年7月23日,AMD(超威半导体)正式发布了基于全新Zen5架构的锐龙线程撕裂者Threadripper9000系列处理器,包括面向专业工作站的撕裂者

行芯科技亮相第三届芯粒开发者大会

在刚刚于无锡圆满落幕的第三届芯粒开发者大会——这场汇聚全球顶尖芯片企业、科研机构及产业链专家的盛会上,行芯科技作为国内Signoff领域的领军企业,受邀发表了主题演讲《面向3DIC的Signoff挑战与行

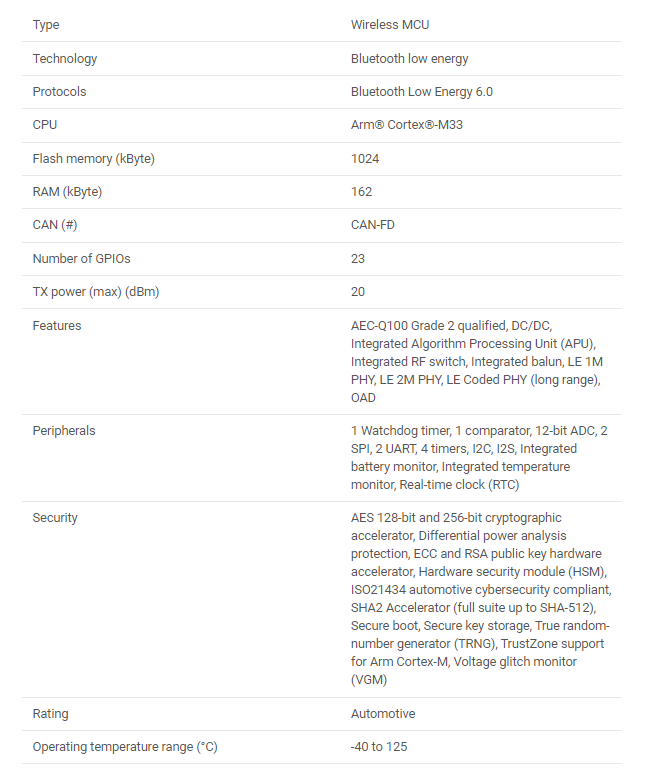

TI芯品CC2745P10-Q1具有1MB闪存、HSM、APU、CAN-FD 和 +20dBm 的汽车级SimpleLink™ 低功耗 Bluetooth6.0无线MCU

TI芯品CC2745P10-Q1具有1MB闪存、HSM、APU、CAN-FD 和 +20dBm 的汽车级SimpleLink™ 低功耗 Bluetooth6.0无线MCU

多芯粒2.5D/3D集成技术研究现状

面向高性能计算机、人工智能、无人系统对电子芯片高性能、高集成度的需求,以 2.5D、3D 集成技术为代表的先进封装集成技术,不仅打破了当前集成芯片良率降低、成本骤升的困境,也是实现多种类型、多种材质、多种功能芯

AMD明年Zen5 APU性能确切,Strix Halo APU将应用多芯粒

AMD明年Zen5 APU性能确切,Strix Halo APU将应用多芯粒

评论