在数字集成电路设计中,SoC(System on Chip)是一种将多个模块集成在单个芯片上的技术。为了确保这些模块能够正确地协同工作,设计者需要使用一种专门的约束语言——SDC(Synopsys Design Constraints)来指导综合、布局布线等后续流程。本文将简要介绍SDC在SoC设计中的作用,并提供一些基本的语法举例。

### SDC的作用

SDC是Synopsys公司定义的一种约束语言,它被用于描述设计者对电路性能、面积、功耗等方面的要求。在SoC设计中,SDC的作用主要体现在以下几个方面:

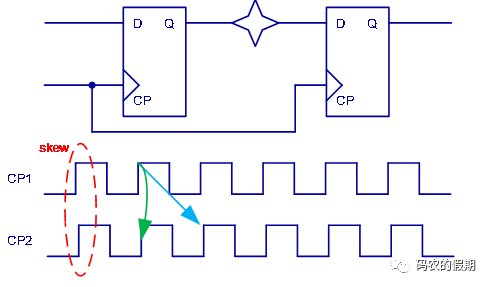

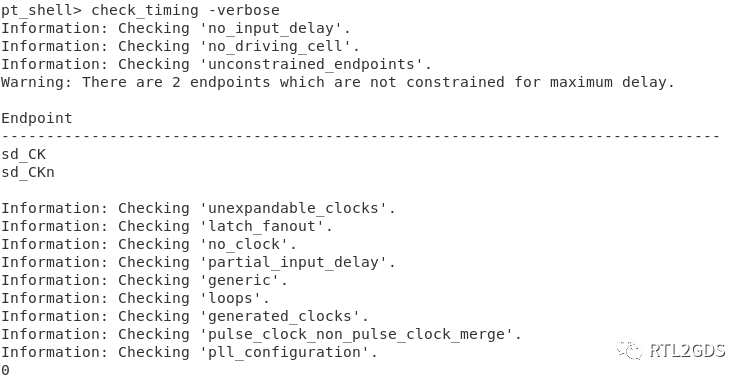

1. **性能约束**:SoC中的各个模块需要满足特定的时序要求,以确保数据能够在正确的时钟周期内传输。SDC允许设计者定义时钟周期、时钟偏斜、时钟抖动等参数,从而确保设计满足性能要求。

2. **接口时序**:SoC中的模块通常需要与外部设备通信,这就要求设计者能够准确地描述这些接口的时序。通过SDC,设计者可以定义输入输出信号的建立时间和保持时间,从而确保数据的正确传输。

3. **功耗管理**:随着移动设备的普及,功耗成为了SoC设计中的一个重要考虑因素。SDC允许设计者定义电源域、电源开关时间等参数,从而帮助降低整个系统的功耗。

4. **布局布线**:SoC设计中,各个模块的布局布线对电路的性能有着重要影响。SDC允许设计者定义模块之间的距离、布线规则等参数,从而优化布局布线过程。

### SDC的基本语法举例

下面是一些SDC的基本语法举例,用于说明如何在SoC设计中使用SDC。

1. **定义时钟**:

create_clock -period 10 -name clk [get_ports clk]这条命令定义了一个周期为10ns的时钟,名称为clk,并将其与输入端口clk关联。

2. **设置时序约束**:

set_input_delay -clock clk -max 2 [get_ports A] set_output_delay -clock clk -min 1 [get_ports B]这两条命令分别设置了输入端口A的最大建立时间为2ns,输出端口B的最小保持时间为1ns。

3. **定义功耗约束**:

set_power_domain -name VDD - supplies [get_ports VDD] set_power_domain -name VSS - grounds [get_ports VSS]这两条命令定义了电源域VDD和VSS,并将其分别与输入端口VDD和VSS关联。

4. **布局布线约束**:

set_false_path -from [get_clocks clk1] -to [get_clocks clk2]这条命令指定了从时钟clk1到时钟clk2的路径为无效路径,即不进行时序分析。

综上所述,SDC在SoC设计中起着至关重要的作用。它不仅能够帮助设计者确保电路的性能、功耗等满足要求,还能够优化布局布线过程,提高设计的可靠性。通过本文提供的SDC基本语法举例,希望读者能够更好地理解SDC在SoC设计中的应用。

审核编辑:刘清

-

集成电路

+关注

关注

5446文章

12469浏览量

372706 -

单芯片

+关注

关注

3文章

479浏览量

35955 -

SoC设计

+关注

关注

1文章

151浏览量

19474 -

SDC

+关注

关注

0文章

50浏览量

16171 -

VDD

+关注

关注

1文章

318浏览量

36786

原文标题:探索SoC设计中的SDC:基本语法与应用实例

文章出处:【微信号:快乐的芯片工程师,微信公众号:快乐的芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

霍尔开关SDC1211,SDC1215,SDC1177,SDC1181,SDC1182,SDC1183应用于TWS,筋模枪,流量传感器,开关门检测等

介绍系统接口sdc

SDC1742 12位自整角机数字转换器

SDC1740 14位自整角机数字转换器

SDC1700/SDC1702:低调自整角机/旋转变压器-数字转换器过时数据表

时序分析基本概念—SDC概述

探讨一下SDC的各种语法构成和整体结构

SDC的基本语法举例:如何在SoC设计中使用SDC?

SDC的基本语法举例:如何在SoC设计中使用SDC?

评论