大端,最高字节存储在最低的内存地址,小端则是最低有效字节存储在最低的内存地址。在Verilog中实现大端(Big-Endian)和小端(Little-Endian)之间的转换通常涉及到对多字节数据的操作。

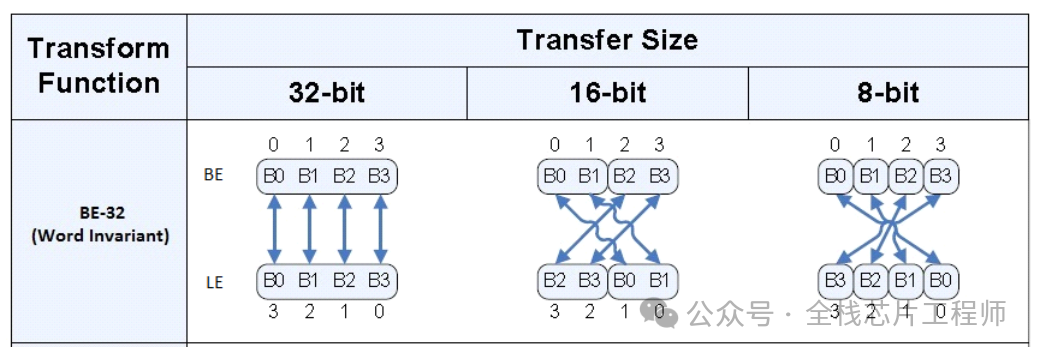

按照word传输不变的要求,一般我们可以分为三种:

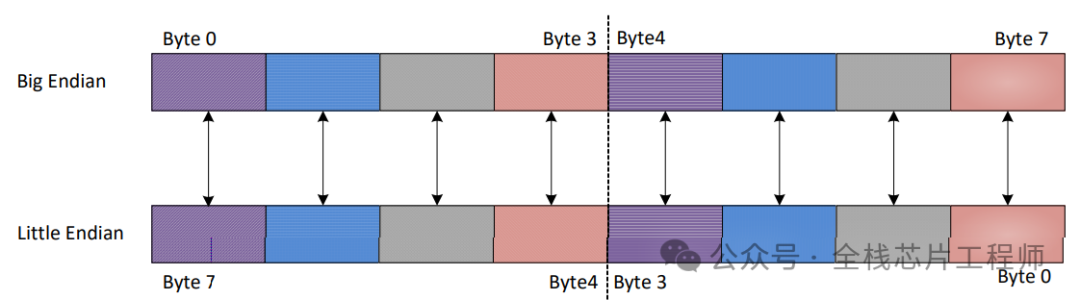

第一种:word传输不变,Word access的处理。

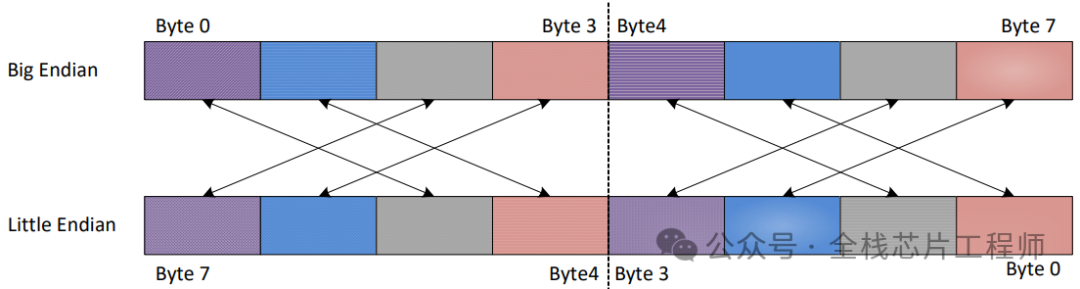

第二种:word传输不变,half Word access的处理。

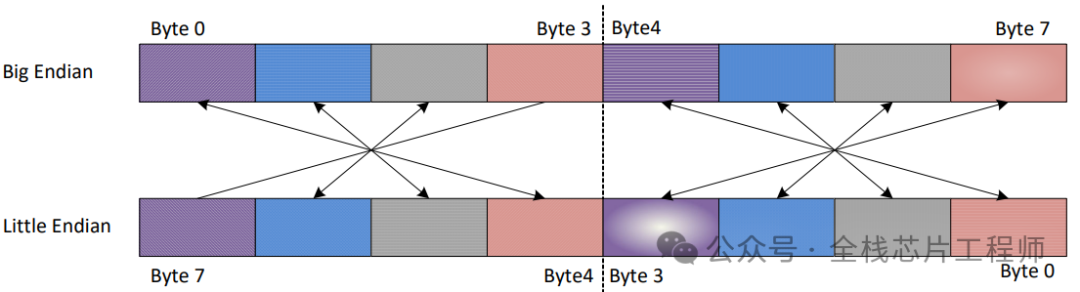

第三种:word传输不变,Byte access的处理。

以下是一个简单的Verilog代码示例,展示了如何在大端和小端之间进行转换。这个例子中,我们假设要转换的数据是一个32位的数字。

module endian_converter(

input wire clk, // 时钟信号

input wire [31:0] data_in, // 输入数据,假设为大端格式

input wire [2:0] mode, // 模式选择信号,2'b00为大转小,2'b01为小转大

output reg [31:0] data_out // 输出数据

);

// 根据模式选择信号进行字节序转换

always @(*) begin

case (mode)

2'b00: begin // 大端转小端

data_out[7:0] = data_in[31:24];

data_out[15:8] = data_in[23:16];

data_out[23:16] = data_in[15:8];

data_out[31:24] = data_in[7:0];

end

2'b01: begin // 小端转大端

data_out[7:0] = data_in[7:0];

data_out[15:8] = data_in[15:8];

data_out[23:16] = data_in[23:16];

data_out[31:24] = data_in[31:24];

end

default: data_out = 32'b0; // 无效模式,输出清零

endcase

end

endmodule

这个模块在每个时钟上升沿触发时执行转换。根据mode的值,数据会被重新排列。对于大端转小端(2'b00),最高有效字节(MSB)被移动到最低有效字节(LSB)的位置,而最低有效字节被移动到最高有效字节的位置。对于小端转大端(2'b01),数据保持不变,因为我们假设输入已经是按照预期的格式排列的。

审核编辑:黄飞

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

内存

+关注

关注

9文章

3234浏览量

76506 -

Verilog

+关注

关注

31文章

1374浏览量

114716

原文标题:字传输不变的3种大小端处理方式

文章出处:【微信号:全栈芯片工程师,微信公众号:全栈芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

无铅PCB的设计方法和表面处理方式选择等介绍

和形状,钢网和焊盘的关系能符合最佳焊接的温度。 2、设计方法和细节的处理: 避免出现焊接立碑的情况,所以在设计时候对器件的受热要考虑周全,保证每个器件受热均匀。 3、表面处理方式的选择: 不同的表面

发表于 09-27 11:51

•0次下载

基于android采用异步处理方式开发移动护理程序的设计

移动护理系统开发采用异步处理的方式,可以缩短执行操作的时间,避免UI线程阻塞。笔者介绍了采用异步处理方式开发移动护理程序的方法,并以移动护理中的病人列表异步任务处理为例进行分析。 任务

发表于 10-26 16:24

•0次下载

介绍学习一种模拟信号的处理方式:对数处理

非常大的信号如1mv~1v,前级电路该如何覆盖处理到上下限而不降低性能呢?切换采集量程是一种最简单的方式,也可通过软件设计成自动控制增益,也可以采用自动增益控制芯片AGC,但是这些方式

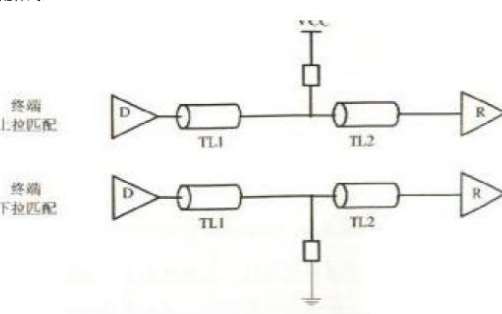

阻抗匹配的四种处理方式

当传输路径上阻抗不连续时,会有反射发生,阻抗匹配的作用就是通过端接元器件,时传输路线上的阻抗连续以去除传输链路上产生的反射。

常见的阻抗匹配有如下几种:

1. 串联端接方式

靠近输出

发表于 02-11 15:35

•20次下载

使用相序识别仪时,常见故障原因以及处理方式概述

使用相序识别仪时,常见故障原因以及处理方式概述 相序识别仪(Phase Sequence Relay)是一种用于工业和家庭电气系统中的设备,主要用于检测和纠正电源的相序错误。然而,相序识别仪也

字传输不变的3种大小端处理方式

字传输不变的3种大小端处理方式

评论