ARM Cortex-M0+是2012年3月14日ARM公司发布的一款低功耗效率、能效最高的ARM处理器,可用于存在设计约束的嵌入式应用。它具有最小的硅面积和极少的代码量,从而使开发人员能够以16和8位的价位实现32位性能。处理器的低门数使其能够部署在需要简单功能的应用中。

作为ARM Cortex-M处理器系列的最新成员,32位Cortex-M0+处理器采用了低成本90纳米低功耗(LP)工艺,耗电量仅9μA/MHz,约为主流8位或16位处理器的1/3,却能提供更高的性能。这类低功耗和高性能的结合为仍在使用8位或16位架构的用户提供了一个转型开发32位器件的理想机会,从而在不牺牲功耗和面积的情况下,提高日常设备的智能化程度。该款经过优化的Cortex-M0+处理器可针对家用电器、白色商品、医疗监控、电子测量、照明设备以及功耗与汽车控制器件等各种广泛应用的智能传感器与智能控制系统,提供超低功耗、低成本微控制器(MCU)。

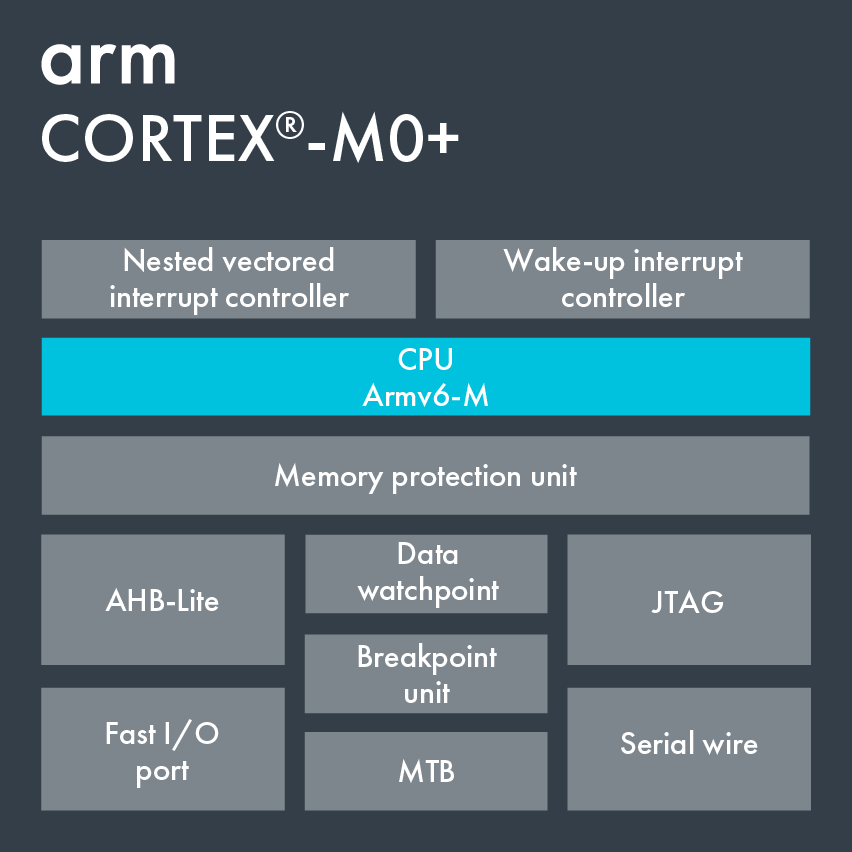

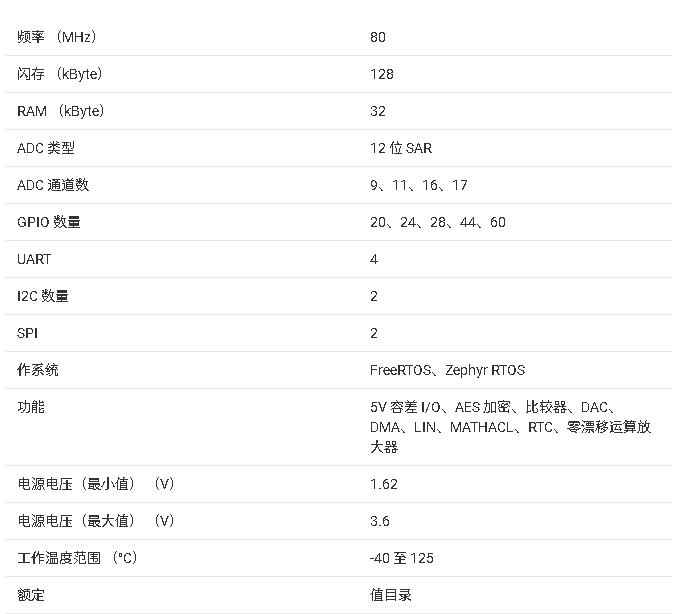

Cortex-M0+集成了存储器保护单元(MPU)、单周期I/O接口和微跟踪缓存(MTB)。ARM Cortex-M0+框图如图1-1所示。

图1-1 ARM Cortex-M0+框图

ARM Cortex-M0+内核具有以下关键特征。

·ARMv6-M架构。

·AHB-lite总线接口,冯·诺依曼总线架构,带可选单周期I/O接口。

·Thumb/Thumb-2子集指令支持。

·2段流水线。

·可选8区域MPU,带子区域和背景区域。

·不可屏蔽中断+1到32个物理中断。

·唤醒中断控制器。

·硬件单周期(32×32)乘法。

·多种休眠模式,带集成式等待中断(WFI)、等待事件(WFE)以及退出时睡眠功能、睡眠和深度睡眠信号。

·根据实现方式提供多种保留模式。

·JTAG和串行线调试端口,具有多达4个断点和2个观察点。

·可选微跟踪缓存。

ARM Cortex-M0+ MCU的关键优势如下。

·小尺寸内核使其能够用作小设备中的单核心,或在需要特定硬件隔离或任务划分时,用作额外的嵌入式配套内核。

·Cortex-M0+内核不会影响基于I/O、模拟和非易失性存储器的典型MCU的各元件之间的取舍。因此在划分MCU产品组合时,总线大小(8、16或32位)不再相关。

·M0+微控制器在入门级应用中广泛使用,并带来了巨大优势。它们满足计算性能要求,其基本架构允许M0+ MCU在开关门数量最少的应用中达到超低功耗性能。Cortex-M0内核可减少噪声发射,并满足使用最佳时钟速度的性能要求。

·内核的动态功率为5到50µW/MHz,取决于所采用的技术。但是,内核并不能代表设备的整体功耗,并且不是要考虑的唯一因素。

·Thumb指令集是Cortex-M系列的子集。它可以重复使用任何经验证的Cortex-M产品软件块,以此来简化产品组合的可扩展性。

·存储器保护单元(MPU)管理CPU对存储器的访问,确保任务不会意外破坏其他激活任务所使用的存储器或资源。MPU通常由RTOS控制。若程序访问的存储器位置被MPU禁止,则RTOS可检测到它并采取行动。内核可基于执行的进程,动态更新MPU区的设置。MPU为可选,并可以进行旁路。

-

内核

+关注

关注

4文章

1476浏览量

43091 -

Cortex

+关注

关注

2文章

220浏览量

49016

发布评论请先 登录

STM32L072xx 超低功耗32位MCU,基于ArmR的Cortex-M0+规格书

Cortex-M0和Cortex-M0+的区别

最小化ARM Cortex-M CPU功耗的方法与技巧分享

Cortex-M0 处理器介绍

RM0479+基于 BlueNRG-LP ARM Cortex-M0+参考手册

Cortex-M0+通用 MCU CW32F系列产品介绍

为什么cortex-M0+功耗低?

STM32C031x4/x6:面向主流应用的Arm® Cortex®-M0+ 微控制器

PY32F030系列32位ARM Cortex-M0+微控制器介绍

Cortex-M0+处理器的HardFault错误介绍

MSPM0C1106-Q1 汽车 32MHz Arm® Cortex-M0®+ MCU技术手册

MSPM0G1507 80MHz Arm® Cortex-M0®+ MCU技术手册

MSPM0L2228 32MHz Arm® Cortex-M0®+ MCU技术手册

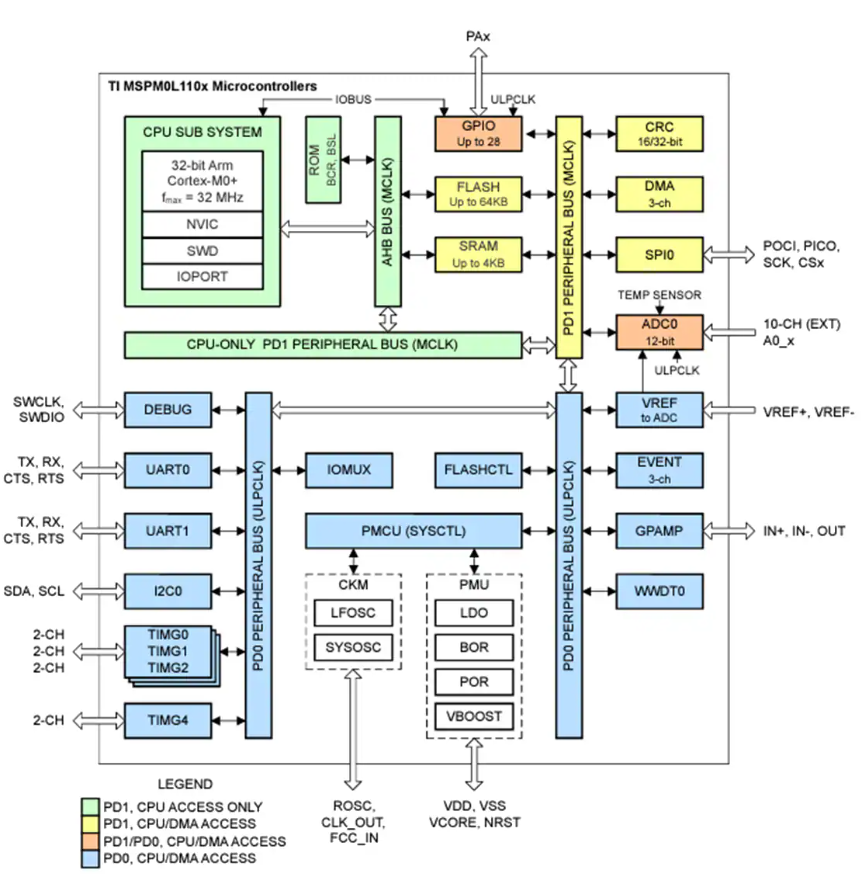

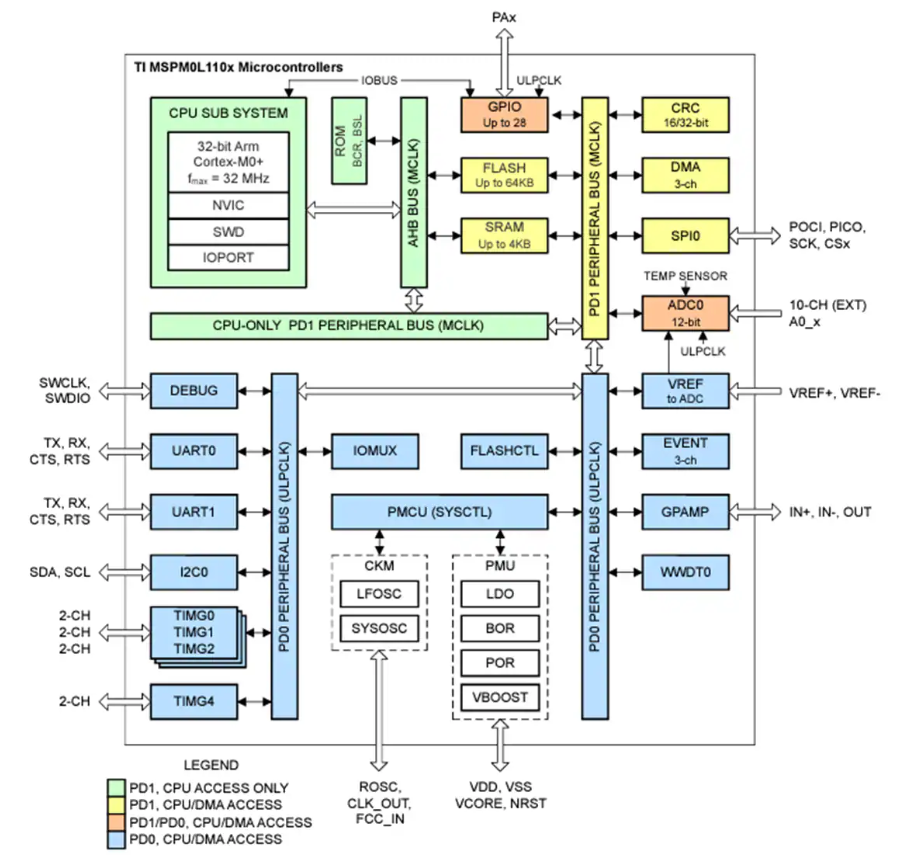

Texas Instruments MSPM0L110x Arm® Cortex®-M0微控制器深度解析

MSPM0L110x Arm Cortex-M0+微控制器技术解析

Cortex-M0+内核介绍

Cortex-M0+内核介绍

评论