1.HardFault介绍

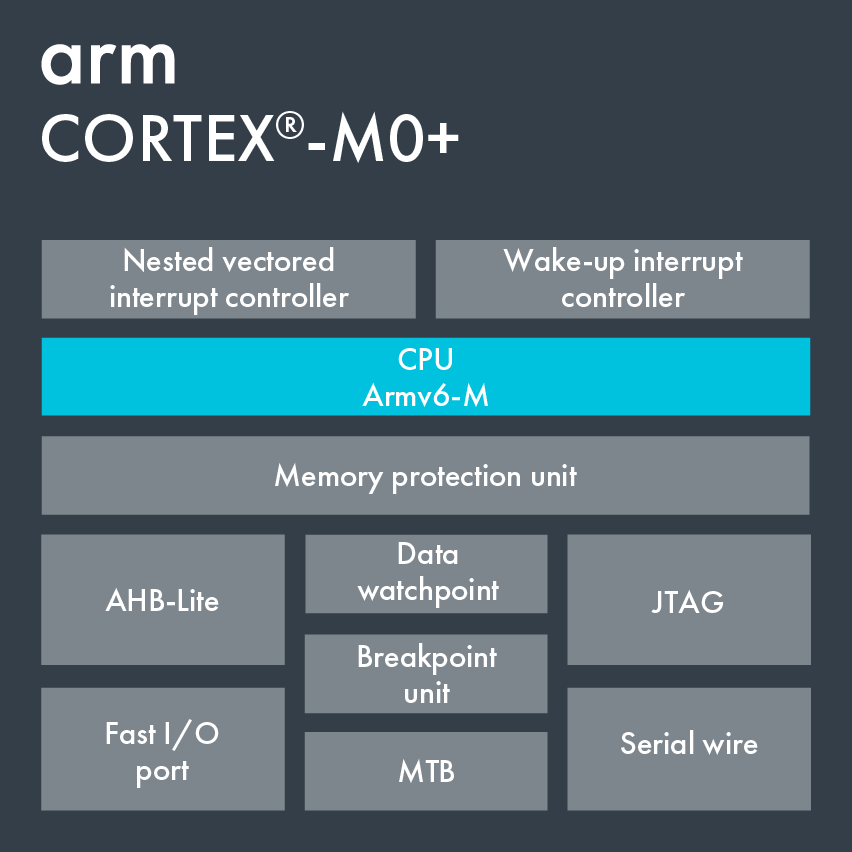

在ARM处理器中,如果一个程序产生了错误并且被处理器检测到,就会产生错误异常。Cortex-M0+处理器只有一种异常用以处理错误:HardFault。

HardFault,可重复且不可能恢复的故障。当它发生时,意味着微控制器出现了问题,并且需要采取修复错误。

2.HardFault错误是如何产生的

Cortex-M0+产生HardFault错误的类型主要有以下三种:

存储器相关:

-- 总线错误(可以是程序访问也可以是数据访问),在总线传输中使用非法地址会产生error;

-- 试图在标记为不可执行的存储器区域内执行程序;

-- 试图在系统控制空间中访问非特权访问等级的寄存器(非特权访问功能在M0+处理器中为可选功能);

-- 存储器访问和定义在存储器保护单元中的设置冲突(存储器保护单元在M0+处理器中为可选功能);

程序错误:

-- 未定义指令的执行;

-- 试图切换至ARM状态:Cortex-M0+处理器无ARM指令,正常情况下处理器不会切至ARM状态;

-- 试图进行非对齐存储器访问;

-- Cortex-M0+处理器支持的Thumb指令只能产生对齐访问,也就是说传输地址只能是传输大小的整数倍; 如字传输(32位)只能访问0x0/0x4/0x8/0xc之类的地址;

--通常情况下,使用C编译器不会产生任何非对齐访问(有编译器自动完成);如果C程序直接操作一个指针,则可能存在非对齐访问;

-- 当SVC异常优先级与当前的优先级相比相同或更小时,试图执行SVC指令;

-- SVC只能运行在线程模式或者比SVC自身优先级低的异常处理中(SVC一般在OS环境中使用),否则会触发硬件错误异常;

-- 执行异常返回时EXC_RETURN的值非法;

-- EXC_RETURN在Cortex-M0+处理器中的合法值为0xFFFFFFF1、0xFFFFFFF9、0xFFFFFFFD;

-- 当调试未使能时(没有连接调试器),试图执行断点指令(BKPT);

-- BKPT指令为调试过程中提供断点功能;

中颖芯片硬件模块操作异常:

-- Flash解锁寄存器写入值错误;

-- Flash解锁后,重新解锁;

-- DMA读取保留地址区或非法读写;

3.如何定位HardFault错误位置

当异常产生时,内核会做如下动作:

压栈并且栈指针(SP)更新;

处理器取出异常向量(确定ISR的起始地址)并将其写入R15(PC);

寄存器更新(LR、终端程序状态寄存器(IPSR)、NVIC)

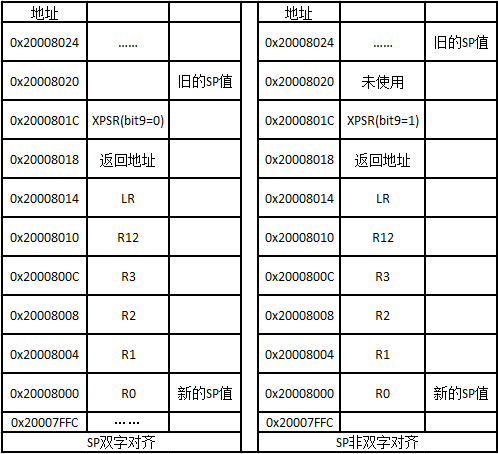

当异常发生时,8个寄存器会被自动压栈,这些寄存器包括R0~R3、R12、R14(LR)、返回地址/PC和xPSR,压栈顺序如下表:

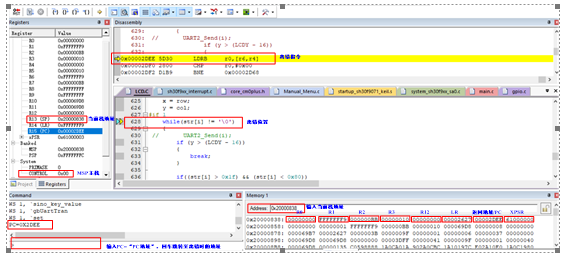

可以通过解析进入Hard Fault中断后的寄存器值及入栈的寄存器值来定位出错位置,并找到问题点。

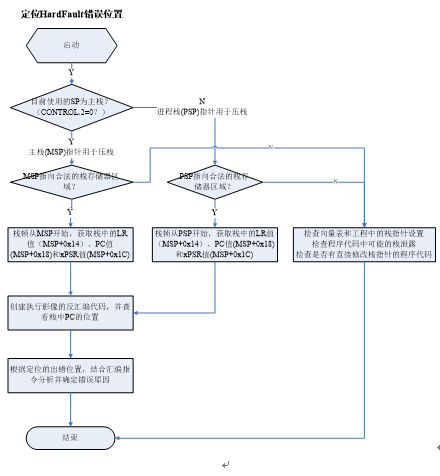

定位HardFault错误位置步骤如下:

4.举例说明如何定位HardFault错误位置

使用调试器(以MDK编译器为例)

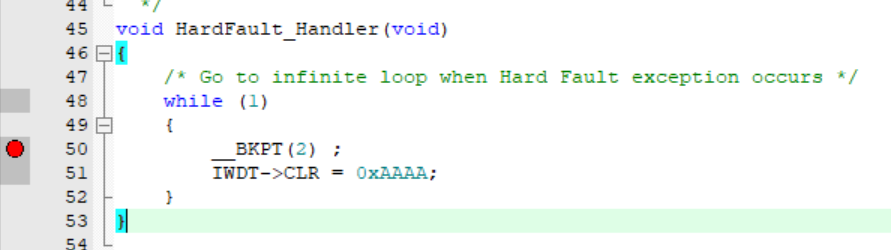

--在工程中创建HardFault中断处理函数,并在其函数中添加硬件断点或断点指令(BKPT),当发生HardFault错误时,处理器会自动暂停到断点或断点指令处

;

-- 根据章节3中的HardFault错误分析流程,找到发生HardFault错误时的地址位置;

-- 结合程序分析具体出错原因。

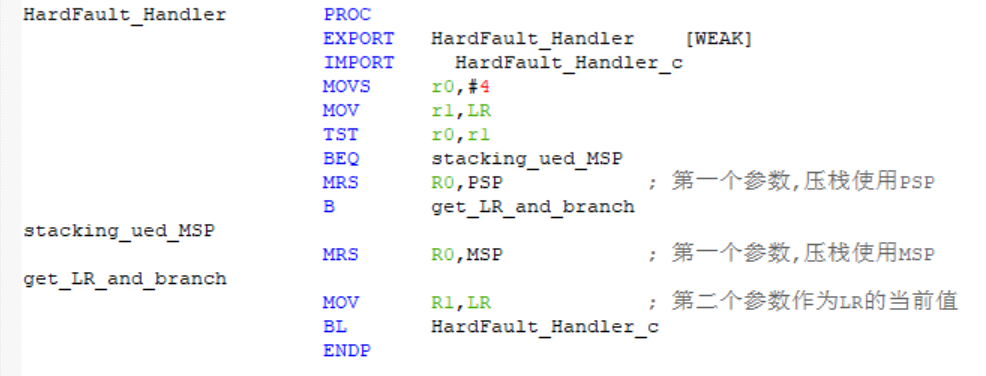

无调试器 -- 当仿真口被占用时,需要通过串口或其他接口,提取并输出发生HardFault错误时的各调试信息; -- 下面以串口为例,说明如何实现调试信息的输出: -- 在startup_xxx.s启动文件的“HardFault_Handler”中做如下处理:

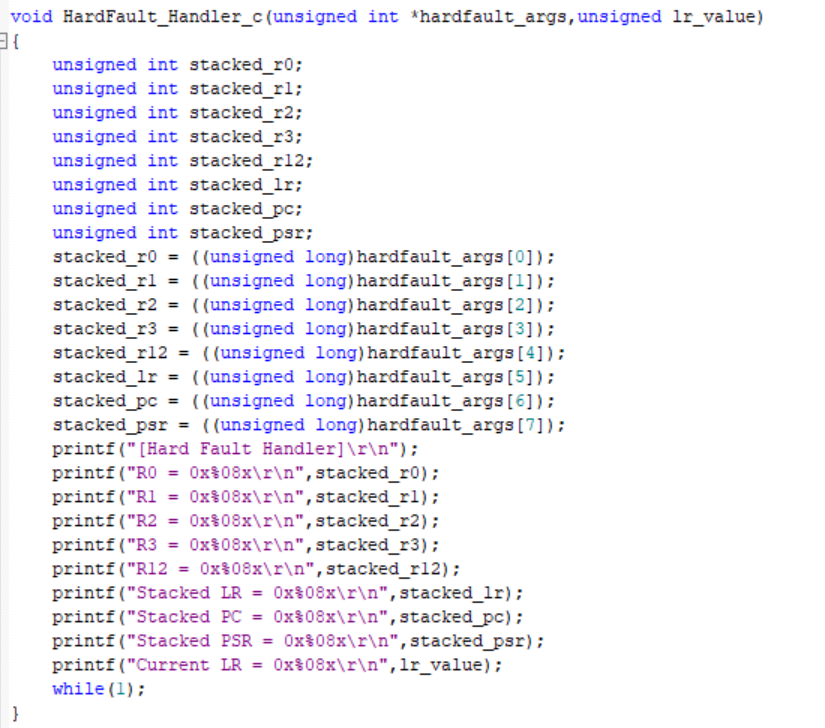

-- 屏蔽C程序中的“HardFault_Handler”中断服务程序,增加栈数据输出函数“HardFault_Handler_c”,如下:

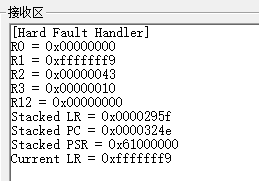

-- 发生HardFault错误后,串口软件会输出当前寄存器及栈内的寄存器值,通过章节3中的HardFault错误定位流程,进一步分析错误原因。

5、如何避免产生Hard Fault

Ø给栈预留足够的空间:

-- 工程编译后,在生成的编译信息文件中,找到以工程名命名的.htm文件,此文件列出工程使用的栈最大长度(如下);

-- 一般在此基础上增加至少0.5倍(预留给中断服务程序及其临时变量),配置为栈大小;

Ø在C语言嵌套汇编代码时,请注意汇编指令是否存在非对齐情况;若存在,请增加NOP指令使其对齐;

Ø程序中不使用断点指令(BKPT);若调试过程中使用了断点指令,请在程序Release时屏蔽此断点指令;

Ø非OS应用,不使用SVC指令;

Ø正确配置芯片的硬件模块,避免引起HardFault错误。

-

微控制器

+关注

关注

48文章

8249浏览量

162266 -

处理器

+关注

关注

68文章

20148浏览量

246936 -

ARM

+关注

关注

135文章

9499浏览量

388555 -

Cortex

+关注

关注

2文章

220浏览量

48392

原文标题:Cortex-M0+ HardFault错误介绍

文章出处:【微信号:SINO_25181447,微信公众号:中颖电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

如何选择正确的Cortex-M处理器?

ARM Cortex-M0+中断机制和中断编程步骤

ARM Cortex-M0+内核定时器

ARM Cortex-M0+处理器数据表

Cortex-M0+——ARM推出全球最节能处理器

ARM发布Cortex-M0+处理器号称世界最高效

飞思卡尔率先推出Cortex-M0+控制器,为何投入ARM怀抱?

关于最低功耗ARM Cortex-M0+的ARM处理器的介绍

cortex内核hardfault错误的定位方法实战

Cortex-M0+内核介绍

Cortex-M0+处理器的HardFault错误介绍

Cortex-M0+处理器的HardFault错误介绍

评论