IMEC在2024年IEEE国际固态电路会议(ISSCC)上推出了开放式设计探路(design pathfinding)工艺设计套件(PDK),并通过EUROPRACTICE提供的相应培训计划。PDK将支持IMEC N2技术中的虚拟数字设计,包括背面供电网络。PDK将嵌入在EDA工具套件中,例如来自Cadence Design Systems和Synopsys的工具套件,为设计探路、系统研究和培训提供对广泛的高级节点访问。这将为业界提供培训未来半导体专家的工具,降低学术界和工业界接触最先进半导体技术的门槛,并使工业界能够通过有意义的设计探索将其产品转变为下一代技术。

晶圆代工PDK使芯片设计人员能够访问经过测试和验证的组件库,以提供功能齐全且可靠的设计。然而,准入限制和保密协议的需要,为学术界和工业界在开发过程中获取先进技术节点设置了很高的门槛。使用IMEC N2 PDK将有助于新一代芯片设计人员尽早接触到在最先进技术节点上发展设计技能所需的基础设施。随附的培训课程将使这些设计人员尽快掌握最新技术,例如纳米片器件和晶圆背面技术。

设计探路PDK包含基于一组数字标准单元库和SRAM IP宏的数字设计所需的基础设施,允许采用2nm环绕栅极(GAA)技术(包括背面连接)进行数字设计。

未来,设计探路PDK平台将会扩展到更高级节点(例如A14)。该培训计划将于第二季度初开始,告知订阅者N2技术节点的特性,并提供使用Cadence和Synopsys EDA软件的数字设计平台的实践培训。

图片来源于网络

审核编辑 黄宇

-

IMEC

+关注

关注

0文章

60浏览量

22875 -

PDK

+关注

关注

1文章

24浏览量

8037

发布评论请先 登录

EFC2K102ANUZ:用于单节锂离子电池保护的双N沟道功率MOSFET

Prometheus千节点集群的横向扩展实践

今日看点:台积电敦促客户预订 2nm 制程产能;广州再添两大百亿级半导体项目

如何在Arm Neoverse N2平台上提升llama.cpp扩展性能

看点:台积电2纳米N2制程吸引超15家客户 英伟达拟向OpenAI投资1000亿美元

PDK在集成电路领域的定义、组成和作用

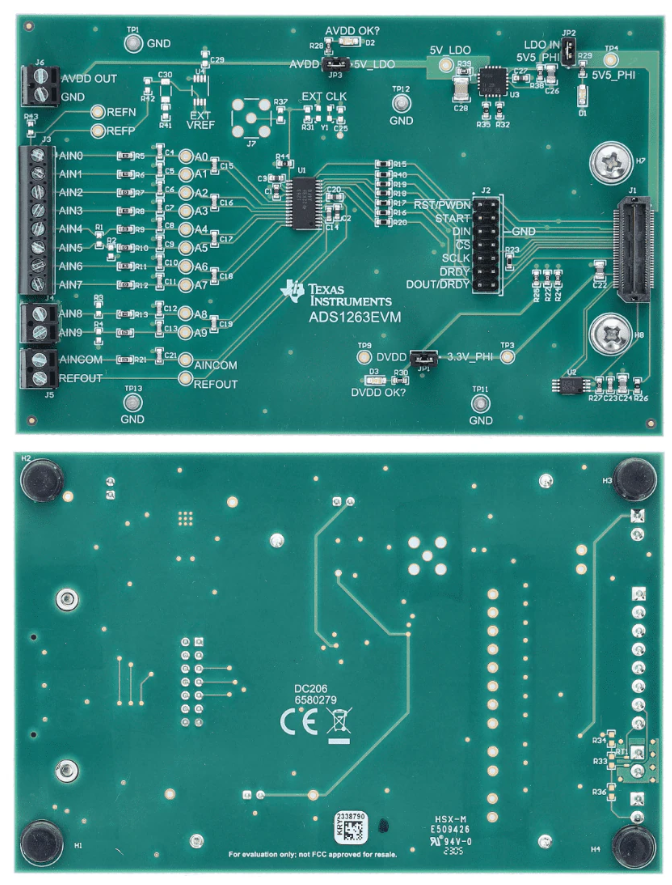

ADS1263EVM-PDK评估模块技术解析与应用指南

多达 48 个计算节点!Firefly 推出 CSC2-N48 AI 算力服务器

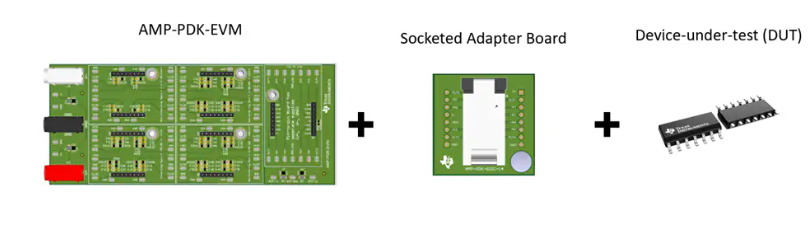

Texas Instruments AMP-PDK-EVM子板开发套件数据手册

Arm Neoverse N2平台实现DeepSeek-R1满血版部署

台安N2变频器与Modbus RTU转Profinet网关实现数据互换

下一代高速芯片晶体管解制造问题解决了!

AMD实现首个基于台积电N2制程的硅片里程碑

IMEC推出针对N2节点的设计探路PDK

IMEC推出针对N2节点的设计探路PDK

评论