Cadence 数字和定制/模拟流程在 Intel 18A 工艺技术上通过认证。Cadence设计 IP 支持 Intel 代工厂的这一节点,并提供相应的制程设计套件(PDK),用于加速一系列应用的开发,包括低功耗消费电子、高性能计算(HPC)、人工智能和移动计算设计。现在,客户可以使用能够立即投产的 Cadence 设计流程和设计 IP,实现设计目标并加快产品上市。

“Intel 代工厂能够与 Cadence 扩大合作,共同为关键市场提供尖端的 Intel 18A 工艺技术,我们为此感到非常荣幸,”Intel 代工厂产品与设计生态系统副总裁兼总经理 Rahul Goyal 说道,“我们将利用 Cadence 业界一流的 IP 组合、AI 赋能的设计技术和先进的封装解决方案,助力客户采用 Intel 代工厂更先进的工艺技术,开发大批量、高性能、高能效的 SoC 产品。Cadence 支持我们的 IDM2.0 策略以及 Intel 代工厂的生态系统,是我们不可替代的合作伙伴。”

“Cadence 研发团队与 Intel 代工厂携手合作,认证了其 Intel 18A 工艺和EMIB先进封装技术的流程,为客户提供一流的SoC(系统级芯片)和芯片系统设计能力,推动开发更先进的人工智能、高性能计算和高级移动应用,“Cadence高级副总裁兼战略及市场开发事业部总经理 Nimish Modi 表示,“我们的客户可以信心十足地进行设计,因为他们知道 Cadence 的工具和 IP 已针对 Intel 代工厂经过优化,可确保客户实现每瓦最高性能,满足更苛刻的设计要求。”

Intel 18A 数字全流程

完整的 AI 驱动的 Cadence RTL-to-GDS 流程已通过认证并优化,可与 Intel 18A 技术无缝配合,帮助客户实现功耗、性能和面积(PPA)目标。该流程包含一系列可靠且强大的解决方案,如 Cadence 的 GenusSynthesis Solution、InnovusImplementation System、Quantus Extraction Solution、Quantus Field Solver、TempusTiming Solution、PegasusVerification System、LiberateCharacterization 以及 VoltusIC Power Integrity Solution。

Intel 18A 定制/模拟流程

Cadence VirtuosoStudio、集成的 SpectrePlatform 以及 Voltus-XFi 定制电源完整性解决方案均已通过 Intel 18A 认证。

Virtuoso Studio 与 Innovus Implementation System 集成,为混合信号设计提供了一套完整的实现方法。此外,Virtuoso Studio 可在 Intel 18A 工艺上提供高效的设计和版图实现。它集成了许多先进的功能,包括:电路和良率优化、可靠性分析、自动化器件和标准单元布局与布线(P&R)、器件编辑辅助功能(包括器件阵列和填充)、集成电迁移及电压降检查、集成签核质量的寄生参数提取,以及使用 Virtuoso InDesign DRC 实现的集成式签核质量级物理验证功能。

Intel 18A 设计 IP

Cadence 为 Intel 18A 技术设计的 IP 支持高性能计算(HPC)以及人工智能/机器学习(AI/ML)应用,包括企业级 PCI Express(PCIe)6.0 和Compute Express Link(CXL);LPDDR5X/5 8533Mbps 的多标准 PHY 支持多样化的存储应用,UCIe用于提升多芯片系统封装集成能力,以及 112G 超长距离 SerDes 用于提供卓越的比特误码率(BER)性能。

-

Cadence

+关注

关注

68文章

999浏览量

146219 -

intel

+关注

关注

19文章

3506浏览量

190574 -

SoC芯片

+关注

关注

2文章

662浏览量

36842 -

人工智能

+关注

关注

1813文章

49747浏览量

261612 -

HPC

+关注

关注

0文章

342浏览量

24829

原文标题:Cadence 数字和定制/模拟流程通过 Intel 18A 工艺技术认证

文章出处:【微信号:gh_fca7f1c2678a,微信公众号:Cadence楷登】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

热压键合工艺的技术原理和流程详解

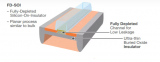

SOI工艺技术介绍

18A工艺大单!英特尔将代工微软AI芯片Maia 2

英特尔288核新至强处理器揭秘:Intel 18A制程,3D堆叠与键合,EMIB封装……

小鹏汽车斩获两项国际顶级安全认证 ISO 26262功能安全流程认证和ISO 21448预期功能安全(SOTIF)流程认证

Cadence携手台积公司,推出经过其A16和N2P工艺技术认证的设计解决方案,推动 AI 和 3D-IC芯片设计发展

新思科技与英特尔在EDA和IP领域展开深度合作

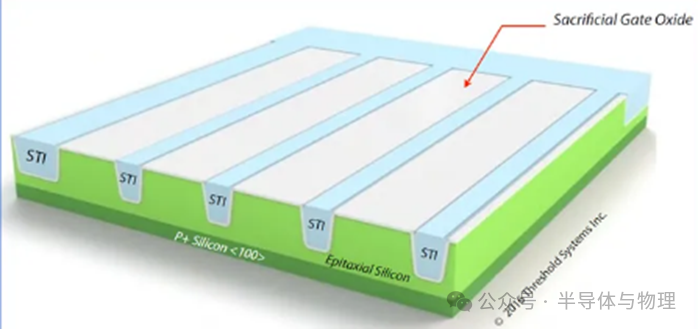

BiCMOS工艺技术解析

英特尔 Panther Lake 移动 SoC 延迟上市,又是18A背锅?

英特尔18A与台积电N2工艺各有千秋

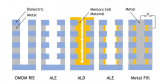

ALD和ALE核心工艺技术对比

Cadence数字和定制/模拟流程在Intel 18A工艺技术上通过认证

Cadence数字和定制/模拟流程在Intel 18A工艺技术上通过认证

评论