首先我们看一下如何在Vivado下设置BITSTREAM配置信息。这可以在综合之后进行。借助如下操作:

打开综合后的设计

依次点击Tools-》 Edit Device Properties

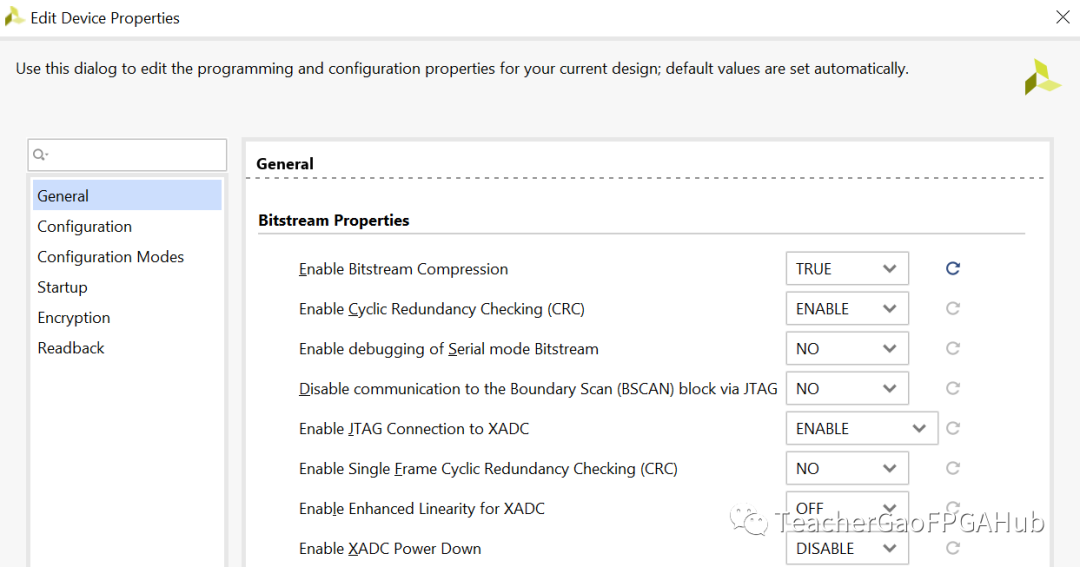

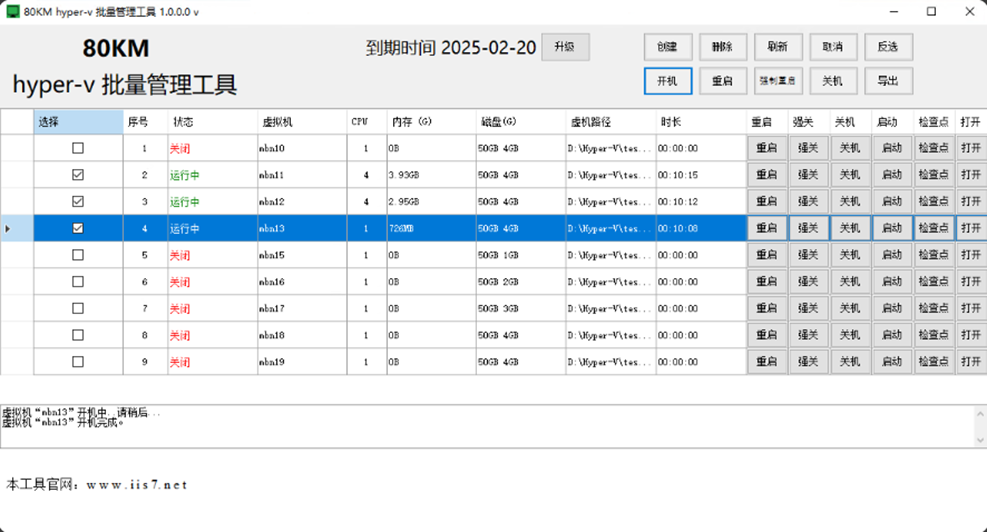

会弹出如下界面。

在这个界面的左侧部分,相当于主菜单,右侧部分为菜单细节。例如,这里选择General,可以看到右侧BitstreamProperties细节。如果要对生成的bit文件进行压缩,就可以选择这里的Enable Bitstream Compression。有时如果只记得某个属性名字,不知道在哪个菜单下,可直接在搜索处(主菜单上方的放大镜处)输入关键字就可以快速找到。

这里我们选择SPI配置方式,同时将未使用的FPGA管脚设置为下拉。

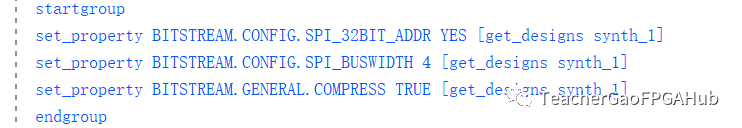

事实上,这些信息最终都是以约束的形式被保存在.xdc文件中。上述设置对应的约束即为(这些命令会出现在Vivado Tcl Console中):

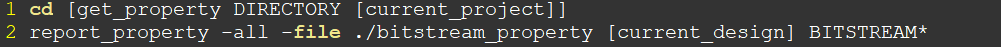

如果已经执行完布局布线并生成了布线后的.dcp文件,那么如何从这个文件中获取BITSTREAM信息呢?这个借助Tcl命令就很简单,具体命令如下图所示。

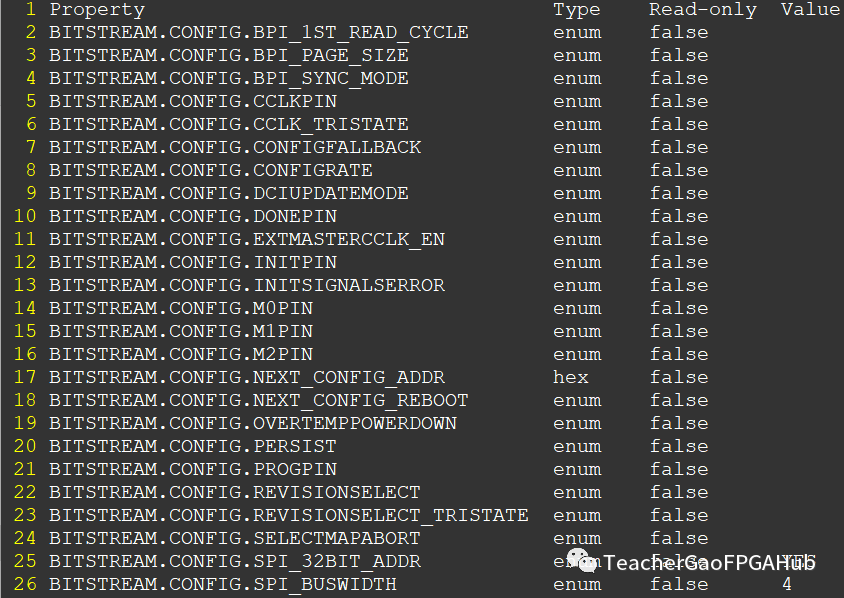

其中第一条命令是将当前目录切换到Vivado工程所在目录。第二条命令则会生成BITSTREAM相关属性信息,并将其写入指定文件中。文件内容如下图所示。可以看到和之前的设置是一致的。

有兴趣的同学可执行下面的命令,观察输出结果,理解命令list_property和list_property_value的含义。

编辑:jq

-

FPGA

+关注

关注

1655文章

22283浏览量

630245 -

SPI

+关注

关注

17文章

1866浏览量

99807 -

Vivado

+关注

关注

19文章

846浏览量

70471

发布评论请先 登录

使用Vivado 2018.2编译E203的mcs文件,遇到的问题求解

生成Bitstream的DRC LUTLP-1错误的解决办法

Windows系统下用vivado将电路烧写到MCU200T板载FLASH的方法

Vivado中向FPGA的Flash烧录e203的方法

如何在Vivado上仿真蜂鸟SOC,仿真NucleiStudio编译好的程序

如何在 IAR Embedded Workbench for ARM 开发环境中启用可配置数据闪存并设置大小?

请问如何在 IAR Embedded Workbench for ARM 开发环境中启用可配置数据闪存并设置大小?

Vivado无法选中开发板的常见原因及解决方法

如何在EZ-USB SX3配置实用程序中配置它的设置?

如何设置信令测试仪的发射参数

hyper-v 配置,Hyper-V配置:性能优化与高级设置

如何在Vivado下设置BITSTREAM配置信息

如何在Vivado下设置BITSTREAM配置信息

评论