2月21日,江苏苏州园区通富微电子有限公司启动三期项目典礼,并迎来其2.5D/3D制程首台设备的入驻。

根据苏锡通科技产业园区信息透露,通富微电子三期项目的启动是其发展历程中的重要里程碑,对突破先进封装测试的关键技术瓶颈起到了关键作用。同时间接说明了其在苏锡通园区先进封装测试基地建设方面取得了显著进展,推动公司步入新的发展征程。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

通富微电

+关注

关注

4文章

51浏览量

24914 -

先进封装

+关注

关注

2文章

562浏览量

1062

发布评论请先 登录

相关推荐

热点推荐

台积电如何为 HPC 与 AI 时代的 2.5D/3D 先进封装重塑热管理

随着半导体封装不断迈向 2.5D、3D 堆叠以及异构集成,热管理已成为影响性能、可靠性与量 产能力的关键因素之一。面向高性能计算(HPC)和人工智能(AI)的芯片功率密度持续提升, 封装尺寸不断扩大

景旺电子景嘉智能制造大厦落成暨项目投产

1月31日上午,景旺电子在深圳宝安隆重举行景嘉智能制造大厦落成暨半导体封装基板及高端高密度印制电路智能制造基地项目投产庆典。

西门子Innovator3D IC异构集成平台解决方案

Innovator3D IC 使用全新的半导体封装 2.5D 和 3D 技术平台与基底,为 ASIC 和小芯片的规划和异构集成提供了更快和更可预测的路径。

2D、2.5D与3D封装技术的区别与应用解析

半导体封装技术的发展始终遵循着摩尔定律的延伸与超越。当制程工艺逼近物理极限,先进封装技术成为延续芯片性能提升的关键路径。本文将从技术原理、典型结构和应用场景三个维度,系统剖析2D、2.5D及3

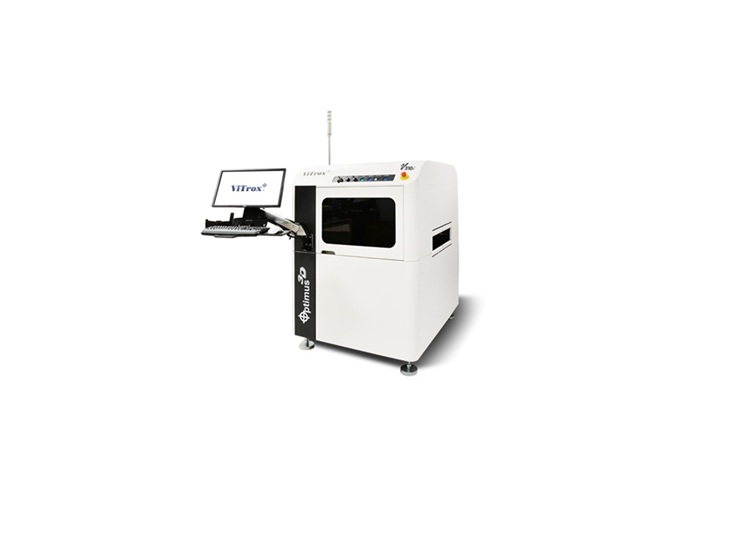

Vitrox 的3D V310i锡膏检测设备

今天,我们将视角聚焦于智能制造的首道质量防线——锡膏检测(SPI),看一项融合了高速3D成像与人工智能的技术,如何为微电子与先进封装领域,构建一个更智能、更可靠的“工艺守护者”。 一、 新挑战:先进

Vitrox的v510i系列的3D AOI光学检测设备

V510i部署在SMT生产线的 贴片机之后、回流焊炉之前或之后 ,主要用于检测贴装好的电子元件是否存在缺陷。其核心任务是: 3D与2D复合检测 :同时利用3D轮廓信息和2

浅谈2D封装,2.5D封装,3D封装各有什么区别?

集成电路封装技术从2D到3D的演进,是一场从平面铺开到垂直堆叠、从延迟到高效、从低密度到超高集成的革命。以下是这三者的详细分析:

Socionext推出3D芯片堆叠与5.5D封装技术

Socionext Inc.(以下简称“Socionext”)宣布,其3DIC设计现已支持面向消费电子、人工智能(AI)和高性能计算(HPC)数据中心等多种应用。通过结合涵盖Chiplet、2.5D

3D封装的优势、结构类型与特点

nm 时,摩尔定律的进一步发展遭遇瓶颈。传统 2D 封装因互连长度较长,在速度、能耗和体积上难以满足市场需求。在此情况下,基于转接板技术的 2.5D 封装,以及基于引线互连和 TSV 互连的 3D 封装等应运而生,并迅速发展起来

华大九天推出芯粒(Chiplet)与2.5D/3D先进封装版图设计解决方案Empyrean Storm

随着“后摩尔时代”的到来,芯粒(Chiplet)与 2.5D/3D 先进封装技术正成为突破晶体管微缩瓶颈的关键路径。通过异构集成将不同的芯片模块化组合,依托2.5D/3D封装实现高带宽

如何提高3D成像设备的部署和设计优势

3D视觉技术正快速普及,其增长得益于成本下降和软件优化,应用场景从高端工业扩展到制造、物流等领域。该技术通过1-2台3D相机替代多台2D设备,显著提升效率并降低成本。目前主流

多芯粒2.5D/3D集成技术研究现状

面向高性能计算机、人工智能、无人系统对电子芯片高性能、高集成度的需求,以 2.5D、3D 集成技术为代表的先进封装集成技术,不仅打破了当前集成芯片良率降低、成本骤升的困境,也是实现多种类型、多种材质、多种功能芯粒集成的重要手段。

软通动力签约中关村温泉科技园三期项目

软通动力凭借数智空间规划与设计、建设与集成能力,成功签约《海淀区温泉镇中关村温泉科技园三期项目》,此次合作进一步彰显了软通动力在园区智能化建设的领航优势。

苏锡通园区通富微电子三期项目启动暨2.5D/3D首台设备落成典礼

苏锡通园区通富微电子三期项目启动暨2.5D/3D首台设备落成典礼

评论