单板上时钟的注意事项 单板上时钟晶体下面铺地的好处

单板上时钟是指将时钟晶体组件直接铺装在电路板上,这种设计方案在电子设备中广泛应用。在介绍单板上时钟的注意事项之前,让我们先了解一下为什么要在单板上放置时钟晶体。

时钟晶体是一种能够稳定产生时钟信号的元件,它常常被用于主频的稳定和时序控制。在过去,时钟晶体通常单独用外壳封装,在电路板上通过引线连接,这种设计虽然方便可靠,但也存在一些问题。引线连接会产生电器特性的不确定性,降低时钟信号的信噪比,同时,晶体与连接线之间的不匹配也会导致时钟信号的波动。为了解决这些问题,单板上时钟成为了一种更为理想的选择。

单板上时钟的注意事项如下:

1. 确保正确安放和固定晶体:单板上时钟的成功与否与晶体的安放和固定有着密切的关系。晶体需要正确地定位在设计图纸上所标明的位置,并采用适当的方式进行固定。可以使用焊接或者特殊的粘贴剂将晶体牢固地固定在PCB板上。此外,为了避免对晶体造成机械应力,晶体周围应该远离其他元件或者大电流热源。

2. 选择合适的板材和线路布局:选择合适的板材和线路布局是确保单板上时钟性能稳定的重要因素。在单板设计中,需要考虑板材的介电常数、热膨胀系数和机械强度等因素,以满足时钟信号传输时的电器和机械要求。同时,线路布局也需要遵循较短、较直接的原则,并且避免与其他信号线或高频元件交叉布线,以减少干扰和串扰。

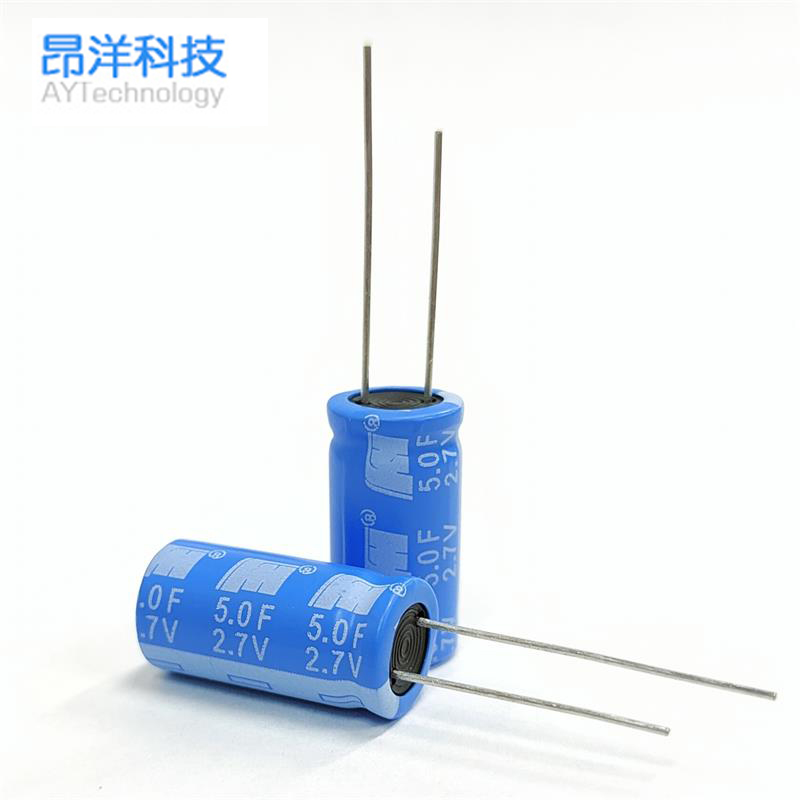

3. 保持时钟信号的完整性:单板上时钟的设计需要保持时钟信号的完整性,以确保时序控制和主频的稳定。为了减少传输线路和其他元件对时钟信号的损耗和干扰,可以采用差分传输线、屏蔽线和降噪电容等方法。此外,还可以通过增加地引脚和电源引脚的数目,提高地和电源的连接质量,减少共模干扰。

4. 适当的温度控制:时钟晶体的性能受温度的影响比较大,因此需要对单板上时钟进行适当的温度控制。可以通过增加散热片、热沉等手段来提高散热效果,降低温度。此外,还可以考虑利用温控晶振等技术来对单板上时钟的温度进行监测和调节。

5. 做好EMC防护:单板上时钟的信号往往包含丰富的高频噪声成分,因此需要对其进行EMC(电磁兼容)设计。可以在时钟晶体附近添加电磁屏蔽罩,或者在设计中增加地线和电源线的连接点,以提高EMC性能。此外,还可以采用合适的解耦电容、滤波电感等元件,来滤除其他信号对时钟信号的干扰。

单板上时钟晶体下面铺地的好处如下:

1. 改善信号的电气性能:在单板上时钟晶体下面铺地可以有效地降低信号的串扰和辐射噪声。铺设地面层可以提供一个良好的地参考平面,降低信号的传输损耗,并减少信号之间的相互影响。

2. 提高系统的抗干扰能力:单板上时钟晶体下面的地面层可以起到屏蔽的作用,减少来自外部电磁场的辐射干扰对时钟信号的影响。地层还可以通过电磁吸收和抑制来降低噪声电流对电路的影响,提高系统的抗干扰能力。

3. 优化信号传输的匹配性能:通过在单板上时钟晶体下面铺设地面层,可以提供良好的电路匹配条件,减少时钟信号的反射和衰减。地面层的引出电流还可以提供一个回路,使得时钟信号能够在PCB板上循环流动,减小信号在传输过程中的波动。

4. 提高系统的稳定性和可靠性:通过适当铺设地层,可以降低温度对时钟晶体的影响,提高时钟信号的稳定性。同时,地层还可以提供稳定的地电位,为晶体提供稳定的工作环境,进一步提高系统的可靠性。

总结起来,单板上时钟的注意事项包括正确安放和固定晶体,选择合适的板材和线路布局,保持时钟信号的完整性,适当的温度控制,以及做好EMC防护。同时,在单板上时钟晶体下面铺设地面层可以改善信号的电气性能,提高系统的抗干扰能力,优化信号传输的匹配性能,以及提高系统的稳定性和可靠性。这些注意事项和铺地的好处将确保单板上时钟的正常工作和稳定性能,进一步提高整个系统的可靠性和性能。

-

信噪比

+关注

关注

3文章

272浏览量

29718 -

时钟

+关注

关注

11文章

2000浏览量

135286 -

信号完整性

+关注

关注

68文章

1500浏览量

98272

发布评论请先 登录

PCBA单板工艺概述

CW32时钟运行中失效检测的流程是什么?CW32时钟运行中失效检测注意事项有哪些呢?

驱动板PCB布线的注意事项

极海APM32E030 MCU中高速时钟的配置和相关注意事项

新品上新:国产工业级AI视觉单板机 + 8核2TOPS NPU算力 ,支持 4K双屏异显

【作品合集】赛昉科技VisionFive 2单板计算机开发板测评

电解电容并联使用有什么好处和注意事项

智多晶PLL使用注意事项

单板上时钟的注意事项 单板上时钟晶体下面铺地的好处

单板上时钟的注意事项 单板上时钟晶体下面铺地的好处

评论