来源:DIGITIMES ASIA

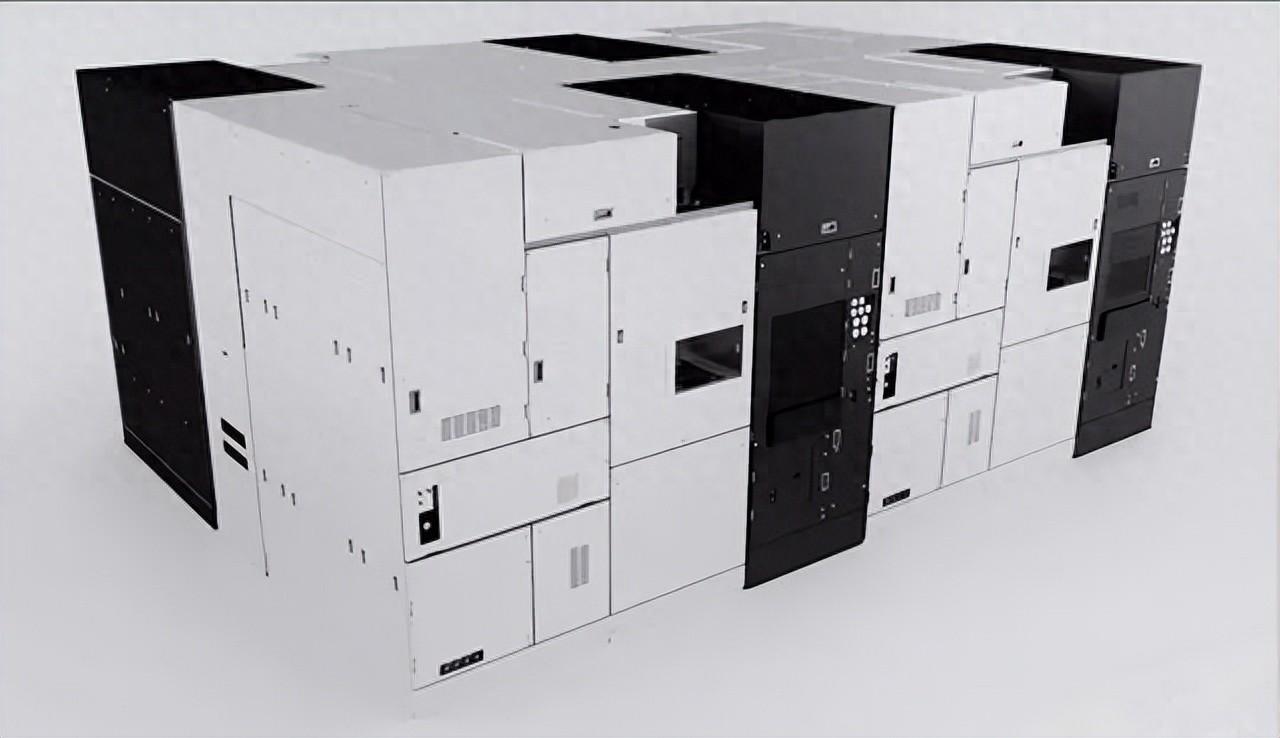

佳能预计其纳米压印光刻机将于今年出货,与ASML的EVU设备竞争市场,因为世界各地的经济体都热衷于扩大其本土芯片产能。

佳能董事长兼首席执行官Hiroaki Takeishi向英国《金融时报》表示,公司计划于2024年开始出货其纳米压印光刻机FPA-1200NZ2C,并补充说芯片可以轻松以低成本制造。2023年11月,该公司表示该设备的价格将比ASML的EUV机器便宜一位数。

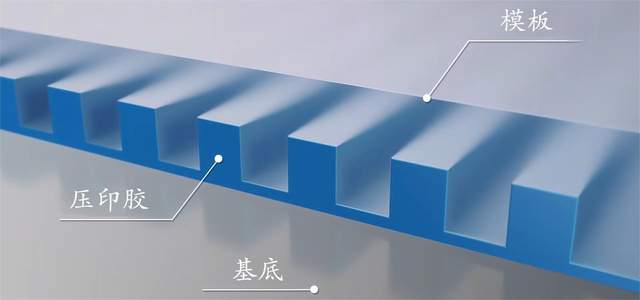

佳能表示,与利用光曝光电路图案的传统光刻技术不同,纳米压印光刻不需要光源,利用简单的原理形成电路,只需将电路图案掩模转移到晶圆表面涂覆的抗蚀剂上即可。此外,纳米压印光刻技术可以一次形成复杂的二维和三维图案,与先进的逻辑曝光技术相比,功耗可降低约十分之一。

Takeishi表示,佳能并不打算从(ASML的)EUV中抢夺市场份额,公司相信多种光刻技术可以共存,为行业的整体增长做出贡献。

Ansforce首席执行官Jeff Chu表示,由于目前大容量NAND闪存采用3D堆叠结构,更适合纳米压印光刻。Bits & Chips报道称,SK海力士和Kioxia多年来一直在测试佳能的纳米压印光刻机。尽管如此,SK海力士在2023年5月表示,纳米压印光刻技术的引入可能或商业化尚未讨论。

采用该技术制造的芯片的良率还有待观察。英国《金融时报》援引分析师的话称,良率必须接近90%才能与ASML的技术竞争。Radio Free Mobile的创始人Richard Windsor表示,如果这项技术真的更先进的话,那么它现在就已经投入运行,并大量投放市场了。

Takeishi告诉英国《金融时报》,佳能已经基本解决了这个问题。然而,由于现有的芯片制造工艺是针对EUV进行优化的,因此引入新技术会遇到各种困难。

图片来源于网络

审核编辑 黄宇

-

光刻机

+关注

关注

31文章

1201浏览量

49004 -

ASML

+关注

关注

7文章

738浏览量

43628

发布评论请先 登录

俄罗斯亮剑:公布EUV光刻机路线图,挑战ASML霸主地位?

AI需求飙升!ASML新光刻机直击2nm芯片制造,尼康新品获重大突破

垄断 EUV 光刻机之后,阿斯麦剑指先进封装

光刻机的“精度锚点”:石英压力传感器如何守护纳米级工艺

国产高精度步进式光刻机顺利出厂

国产首台28 纳米关键尺寸电子束量测量产设备出机

全球市占率35%,国内90%!芯上微装第500台步进光刻机交付

今日看点丨佳能再开新光刻机工厂;中国移动首款全自研光源芯片研发成功

佳能9月启用新光刻机工厂,主要面向成熟制程及封装应用

AI PC爆发年!2025出货量将破亿,科技巨头引领产业变革

压电纳米定位系统如何重塑纳米压印精度边界

佳能预计到2024年出货纳米压印光刻机

佳能预计到2024年出货纳米压印光刻机

评论