时钟是芯片验证过程中最基本也是最重要的决定因素,一个精确的时钟产生对时钟敏感的电路来说至关重要。

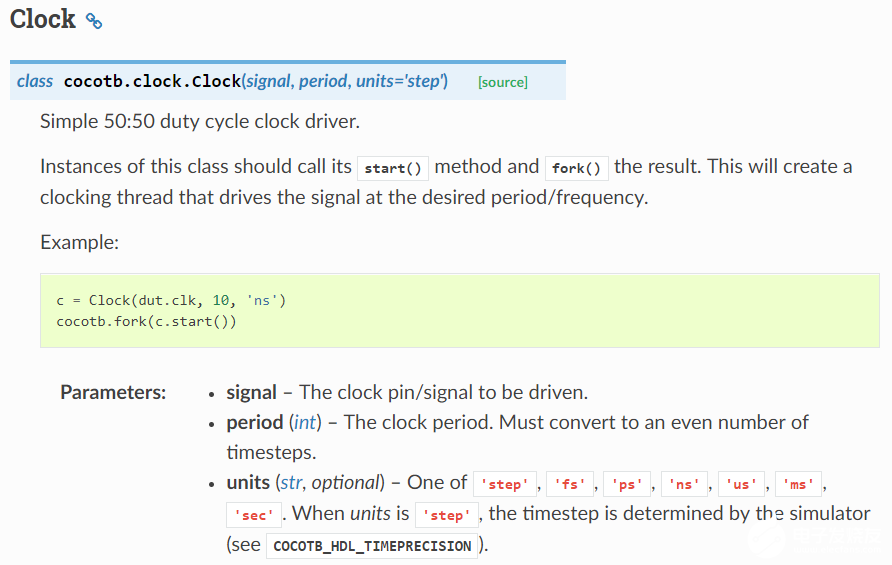

Cocotb平台中内建了时钟产生的函数Clock()。Clock函数在官网上的描述如下:

Clock函数一共有三个形参,分别为:

signal:驱动的时钟信号,如dut.clk

period:时钟周期,必须为偶数个时间单位

units:时间单位,可以为“飞秒”、“皮秒”、“纳秒”、“微秒”、“毫秒”、“秒”等时间单位;同时支持“时间步”,此时则协同“COCOTB_HDL_TIMEPRECISION”来决定具体的时间单位。

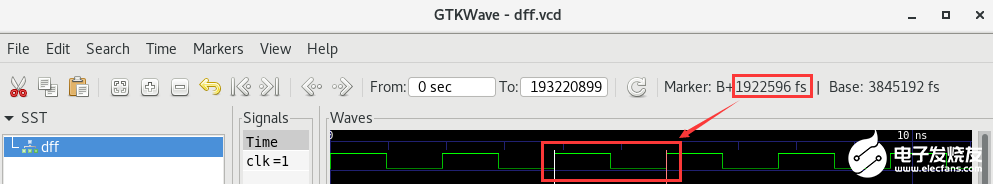

Clock的构造实例如下:

方式一:c = Clock(dut.clk, 10, 'ns')

cocotb.fork(c.start())

方式二:cocotb.fork(Clock(dut.clk, 10, units='ns').start())

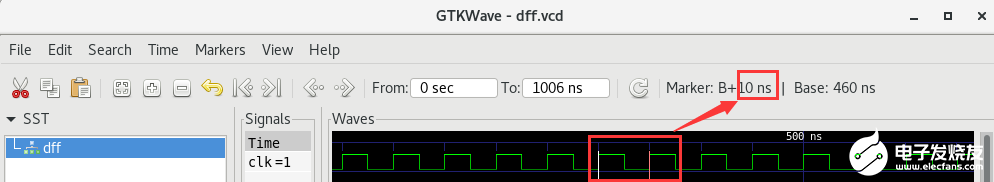

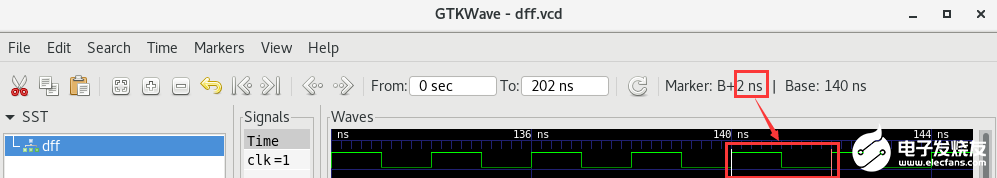

产生的效果如下:

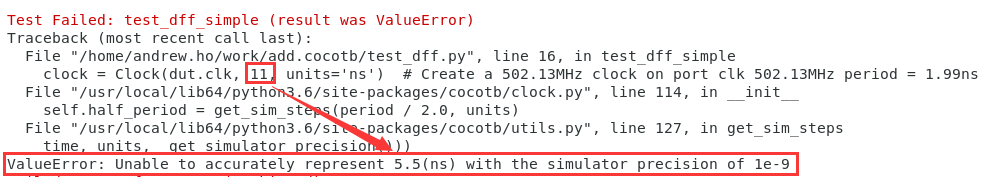

当时钟周期为奇数时则会报相关系统错误

当希望产生一个520.13MHz频率的时钟时,时钟周期为1.922596274008421ns,为了产生精度较高的520.13MHz时钟时,可以采用不同的时间单位来构造该时钟。

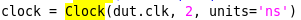

1、采用时间单位为“ns”,时钟周期四舍五入取值为2ns

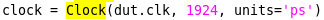

2、采用时间单位为“ps”,时钟周期四舍五入取值为1923ps,周期要求偶数则取值为1924ps

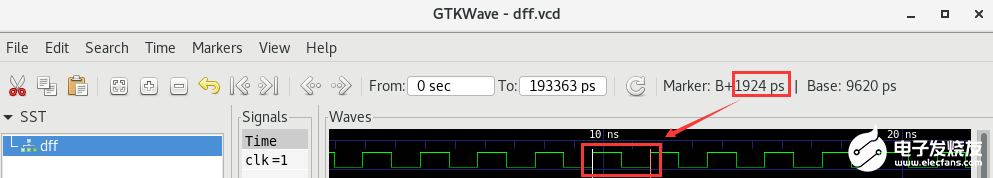

3、采用时间单位为“fs”,时钟周期四舍五入取值为1922596fs

Clock函数采用不同的时间单位时需要确保与代码的timescale匹配,也就是说Clock函数的时间单位应大于等于timescale的时间单位。

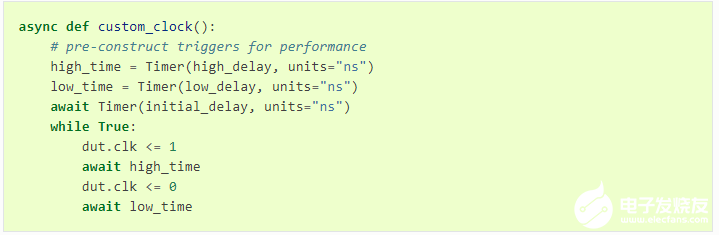

以上产生的时钟均为占空比1:1的时钟,当用户需要产生占空比非1:1的时钟时,可以参考如下代码的实现:

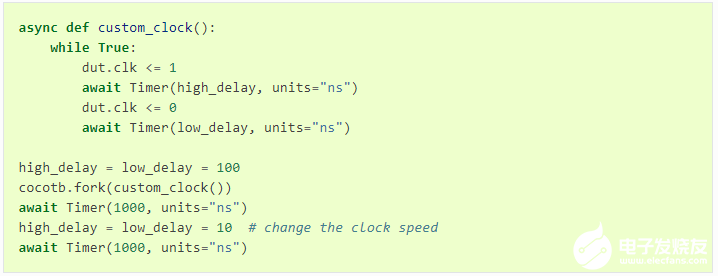

当用户需要做时钟的动态调整时,可以参考如下的代码实现:

审核编辑:黄飞

-

芯片

+关注

关注

462文章

53574浏览量

459427 -

时钟

+关注

关注

11文章

1953浏览量

134562 -

函数

+关注

关注

3文章

4406浏览量

66859 -

时钟信号

+关注

关注

4文章

495浏览量

29700

发布评论请先 登录

SoC验证平台的FPGA综合怎么实现?

验证方法简介

Python硬件验证——摘要

基于FPGA的NoC验证平台的构建

基于PCI接口的IP验证平台

基于System Verilog的可重用验证平台设计及验证结果分析

基于python的用于构建仿真及测试用例的lib库cocotb

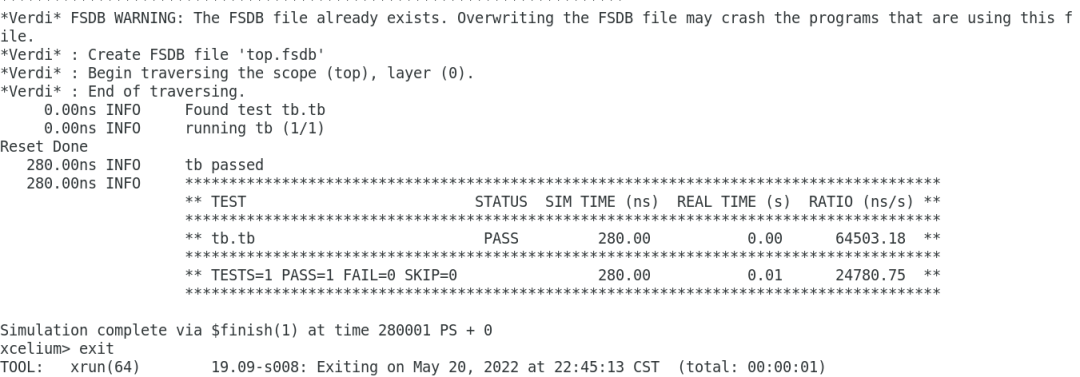

Cocotb验证平台时钟的产生代码

Cocotb验证平台时钟的产生代码

评论