Vivado在前一段时间更新了2023.2版本,经过一段时间的使用这个版本还是很丝滑的,用起来挺舒服。

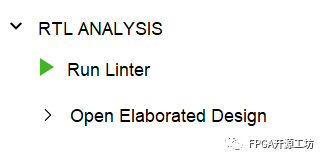

特别是增加了一个Lint检查的按钮,可以让我们提前知道RTL设计有什么风险。做数字IC设计的时候写完代码之后可能不是直接就去仿真,而是先拿Spyglass做一次检查,消除掉lint错误之后再拿去仿真,Vivado增加了这个功能,让我们能够更好的去掌控自己的代码。

这个lint检查有什么作用呢,先来看一小段代码。

`timescale 1ns / 1ps module top( input [7:0] a , input b , output [7:0] c ); always @(*) begin if(b == 1'b1)begin c = a; end end endmodule

没有几行代码,直接一看有两处问题,第一是c在always begin end里面进行赋值的,应该用reg类型,第二会产生一个latch。

代码比较少,可以一眼发现问题,如果代码比较多呢,还能一眼发现问题吗?之前版本没有lint检查的时候,我们会拿去直接综合,也许会给我们报一个警告出来,但是又有多少次我们会去一个一个的看这个警告报的什么问题呢?

现在增加了Lint功能,直接点击run一下看看。

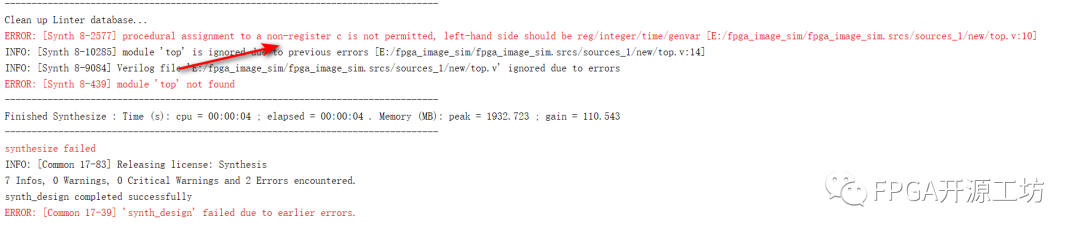

vivado直接报错了,告诉我们c不是reg类型的。

把c改成reg类型的,代码如下

`timescale 1ns / 1ps

module top(

input [7:0] a ,

input b ,

output reg [7:0] c

);

always @(*) begin

if(b == 1'b1)begin

c = a;

end

end

endmodule

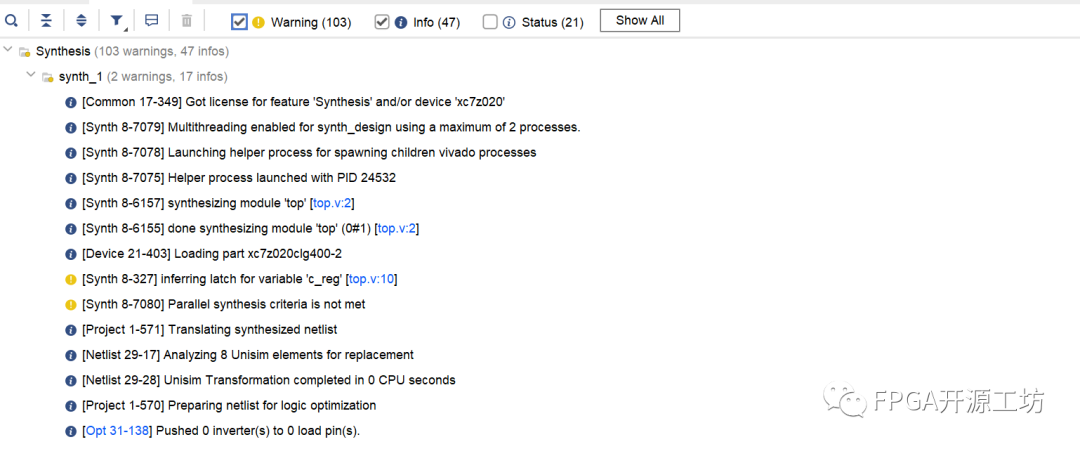

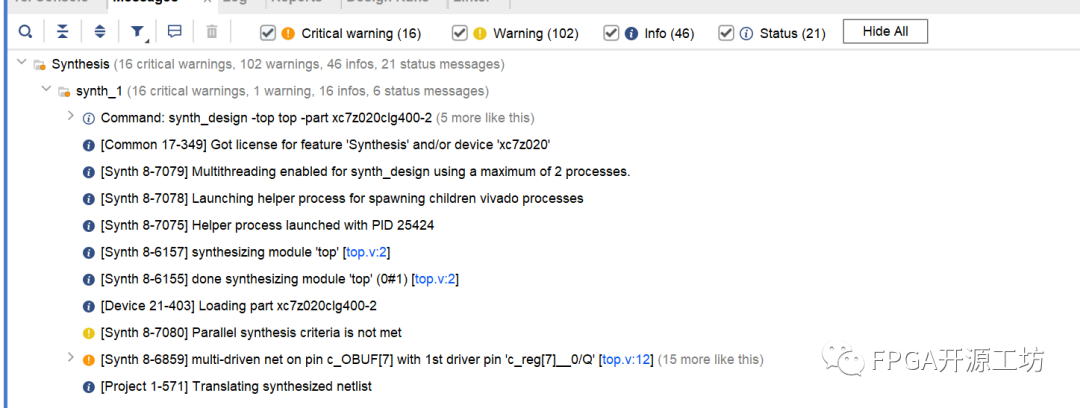

先来综合一下看看,下面是报告。

看起来一点问题都没有,报了一大堆信息,也许你仔细看还能看到其中一条警告说c被综合成一个latch了,要是信息更多的话还会看到他不。

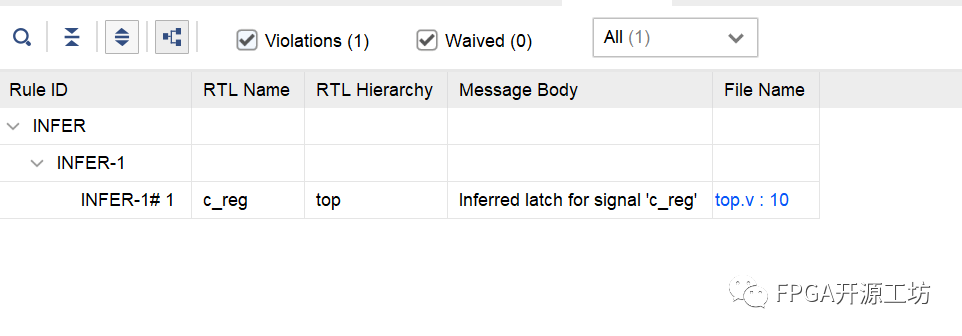

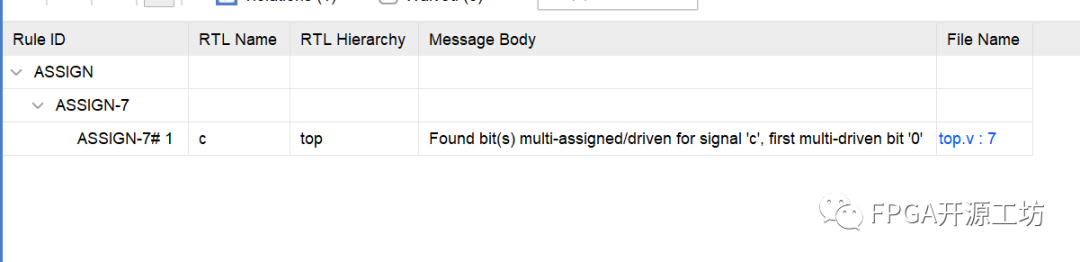

而运行lint之后,会帮我们生成一个表,可以很清晰的看到这些信息:

再来看另外一个典型的多驱动问题:

`timescale 1ns / 1ps

module top(

input clk,

input [7:0] a1 ,

input [7:0] a2 ,

input b ,

output reg [7:0] c

);

always @(posedge clk) begin

if(b == 1'b1)begin

c <= a1;

end

end

always @(posedge clk) begin

c <= a2;

end

endmodule

在综合后会有一个关键警告产生,但也不会报错,这个会在之后的布局布线的时候报错。

同样lint也会把这个问题给暴露出来:

还有一些小问题比如位宽不匹配的问题,lint也能帮我们查出来

`timescale 1ns / 1ps

module top(

input clk,

input [7:0] a ,

input b ,

output reg [6:0] c

);

always @(posedge clk) begin

if(b == 3'b101)begin

c <= a;

end

end

submodule submodule_inst(

.a (kkk)

)

endmodule

module submodule (

output [3:0] a

);

assign a = 3'b111;

endmodule

不知道大家能一眼看出来这个代码的问题不。

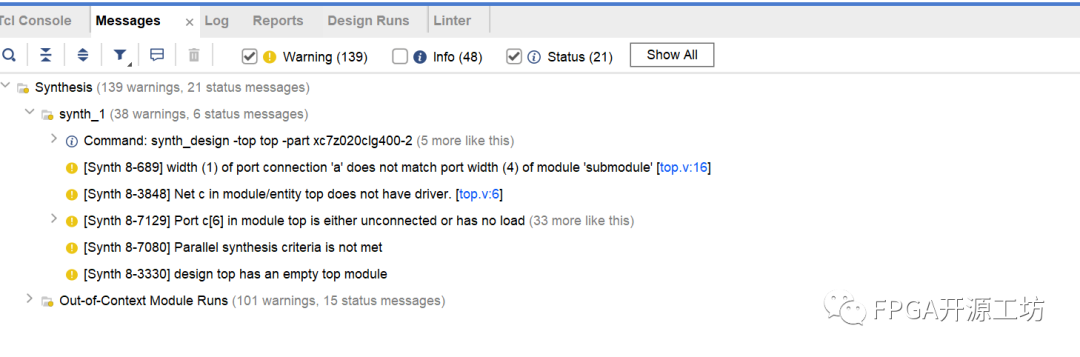

先看看综合的结果:

看着似乎没啥问题。

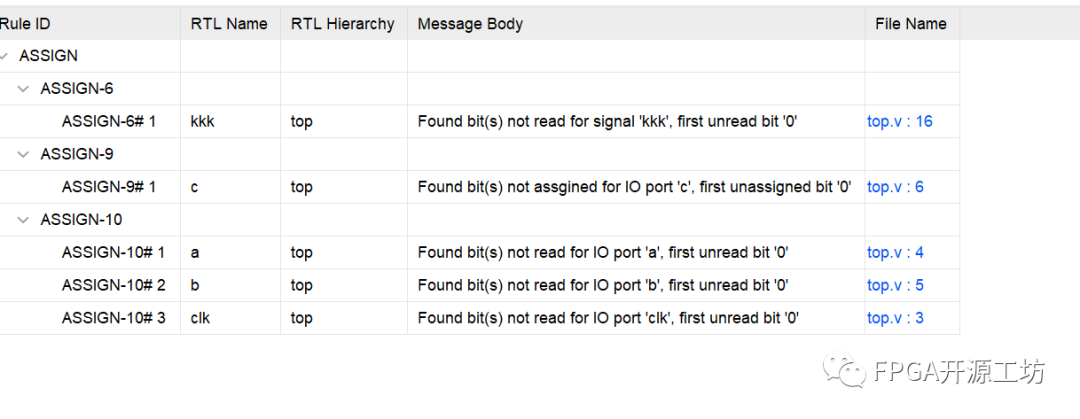

lint报了一堆位宽不匹配的问题。

先看看第一个kkk的位宽不匹配,可以看到在在submodule这个模块里面输出了一个4bit的变量,但是我们在例化这个模块的时候kkk忘记定义了,这个时候kkk就被隐式推断为了一个1bit的wire类型的变量,这样就出现了潜在的bug。其他几个位宽不匹配也是一样的,当然不是所有的位宽不匹配都是bug,这个就需要我们明确知道哪些是我们故意这样设计的。

通过观察lint报告,可以让我们更加了解自己的设计,让问题发现在最开始的地方,而不是等到最后布局布线了甚至更晚,才发现这种低级的问题。

审核编辑:汤梓红

-

IC设计

+关注

关注

38文章

1406浏览量

108440 -

仿真

+关注

关注

55文章

4539浏览量

138698 -

RTL

+关注

关注

1文章

395浏览量

62902 -

代码

+关注

关注

30文章

4977浏览量

74419 -

Vivado

+关注

关注

19文章

860浏览量

71428

原文标题:Vivado2023.2的一个小功能

文章出处:【微信号:FPGA开源工坊,微信公众号:FPGA开源工坊】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Vitis2023.2使用之—— updata to Vitis Unified IDE

Hanlp1.7版本的新增功能一览

Xilinx发布Vivado 2013.3 新增全新设计方法及功能

赛灵思Vivado设计套件推出2013.1版本,提供IP 集成器和高层次综合功能

Vivado Design Suite 2015.3新增量编译功能介绍

Vivado™ 设计套件 2023.2 版本:加速自适应 SoC 和 FPGA 产品设计

Vitis2023.2全新GUI的功能特性介绍

使用Vivado通过AXI Quad SPI实现XIP功能

AMD Vivado设计套件2025.1版本的功能特性

Vivado 2023.2版本的新增功能

Vivado 2023.2版本的新增功能

评论