OSTU大津法是一种确定图像二值化阈值的方法,由日本学者大津提出来的。

FIFO是FPGA/IC设计中经常使用到的模块,它经常被用在两个模块之间进行数据的缓存,以避免数据在....

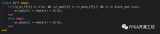

verilog语法中使用以下两个运算符可以简化我们的位选择代码。

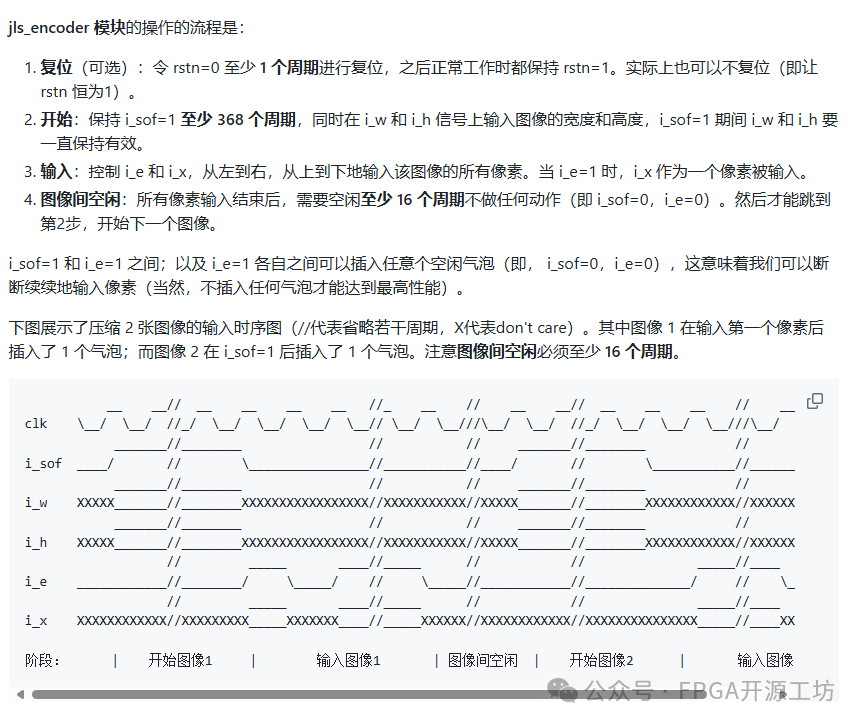

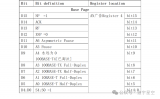

现在来看一下GitHub上面一个开源的JPEG LS算法的Verilog实现

我们在日常开发中经常使用sublime、vim、vs code等第三方的编辑器,这些编辑器可以使用很....

以上按位数分可以编译为32位和64位两种,另外就是都可以编译为elf版本和linux版本。

如果同一个上下文中对少量元素进行编码,通常无法获得足够的上下文编码信息。但是如果对大量元素进行编码又....

在图像压缩算法中可以采用哈夫曼编码的方式对编码冗余的信息进行压缩,可以采用预测的方式来减少像素间冗余....

10M/100M/1000M自协商,主要协商的内容为“速度双工”、“流控”和“主从”三大类,下面先介....

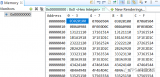

NextPage有两大类(D13=1时为Messgage Page; D13=0时为Unformat....

在FLP突发中,D0应是传输的第一个比特。

自协商机制是以太网技术物理层重要的一种机制。它可以使得不同底层技术网络设备(计算机终端,网桥,交换机....

这个过程很简单,分为下面几个步骤。

在FPGA图像处理--CLAHE算法(一)中介绍了为啥要用CLAHE算法来做图像增强。

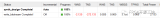

在做仿真的时候往往会去做代码覆盖率和功能覆盖率的分析,来保证仿真是做的比较充分完备的。

在介绍CLAHE算法之前必须要先提一下直方图均衡化,直方图均衡化算法是一种常见的图像增强算法,可以让....

相信好多人在开始学习FPGA图像处理的时候都是接触的RGB转灰度图,Sobel图像检测,直方图均衡化....

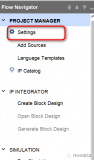

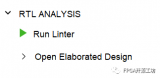

Vivado在前一段时间更新了2023.2版本,经过一段时间的使用这个版本还是很丝滑的,用起来挺舒服....

为了省流,还是先甩结论。有符号数和无符号数的最本质区别就是:符号位的识别和高位拓展。除此之外,另一个....

在上一篇FPGA图像处理--Canny边缘检测(一)里介绍了Canny边缘检测的NMS计算,这里就介....

在之前的文章里面介绍了Canny算法的原理和基于Python的参考模型,之后呢在FPGA上完成了Ca....

在边缘检测算法里面Sobel是比较简单的一个算法,但是其检测出来的边缘往往是比较粗的,效果不是很好,....

今天群友遇到一个在综合的时候报错ambiguous clock in event control的问....

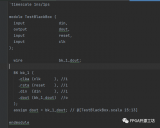

在仿真的时候会实时打印DUT和参考模型的结果是否比对成功。因为设置了DUT和参考模型的结果之间的阈值....

SpinalHDL是基于Scala全新的硬件描述语言,解决了不少Verilog等传统HDL语言的痛点....

HSV色彩空间相对于RGB色彩空间更适合做颜色追踪,分割颜色等。那么RGB色彩空间要怎么转变为HSV....

在Zynq开发中有一个很常用的功能是将ARM端的数据导出到本地,然后通过Matlab,Python等....

在SpinalHDL中使用之前已有的Verilog等代码的时候需要将这些代码包在一个BlackBox....

重构技术是一项非常实用的技术,从比特属性上来分类可以分成全部重构和局部重构。

在三天前SpinalHDL1.8.0正式上线,在这次更新中增加了Scala代码和生成的RTL代码....