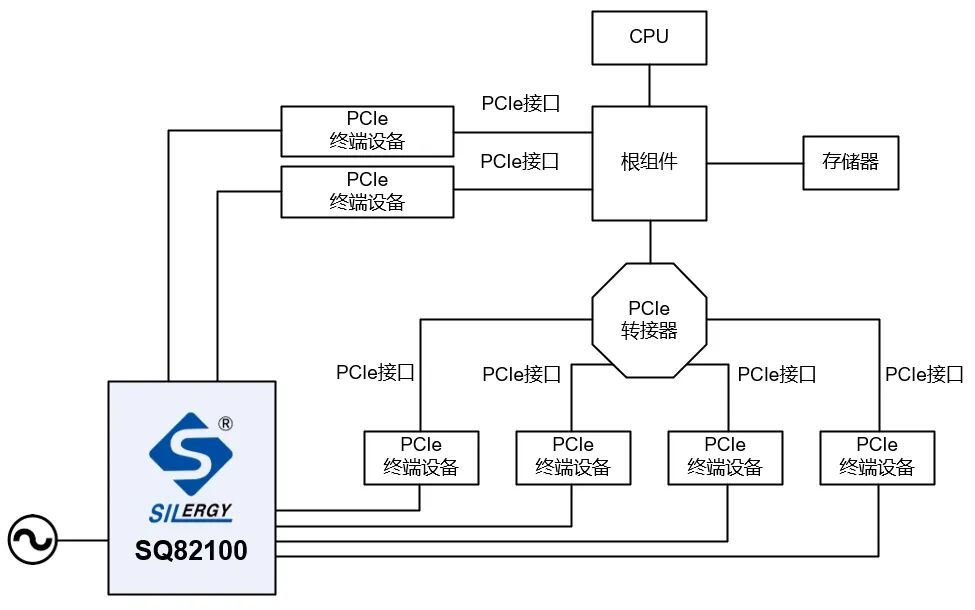

PCI-Express(PCIe)是一种高速串行计算机扩展总线标准,主要用于扩充计算机系统总线数据吞吐量以及提高设备通信速度。目前服务器等应用已集成越来越多的PCIe终端,矽力杰新一代高性能PCIe时钟缓冲器SQ82100可以为系统提供20路超低附加抖动的LP-HCSL参考时钟,能够简化系统布局,进一步提高终端系统性能和集成度。

PCIe接口

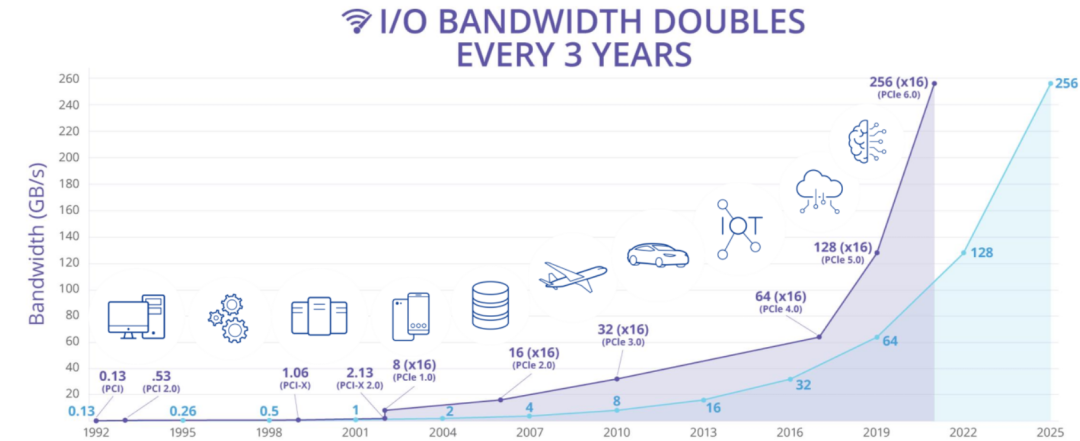

PCIe接口常用于服务器和高性能计算系统的高速数据接口,经过多年发展,PCIe接口已经从PCIe Gen1(2.5GT/s)演进到如今的PCIe Gen6(64GT/s),在个人计算机,服务器,工作站,辅助驾驶等电子设备终端中被广泛应用。

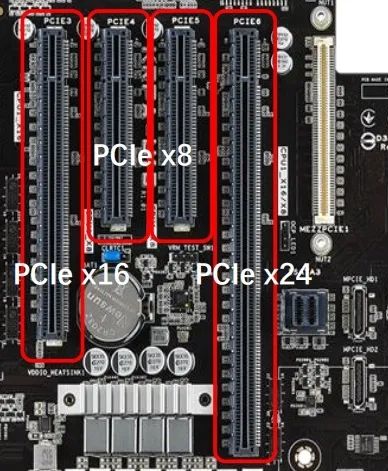

PCIe接口的参考时钟为100MHz的差分 HCSL/LP-HCSL 电平信号。最为常用和可靠的时钟架构是Common Clock Architecture (CC),即使用单一的时钟缓冲器为多个PCIe终端设备提供点对点的参考时钟,如下图为服务器的主板上的PCIe接口。

矽力杰多通道时钟缓冲器方案

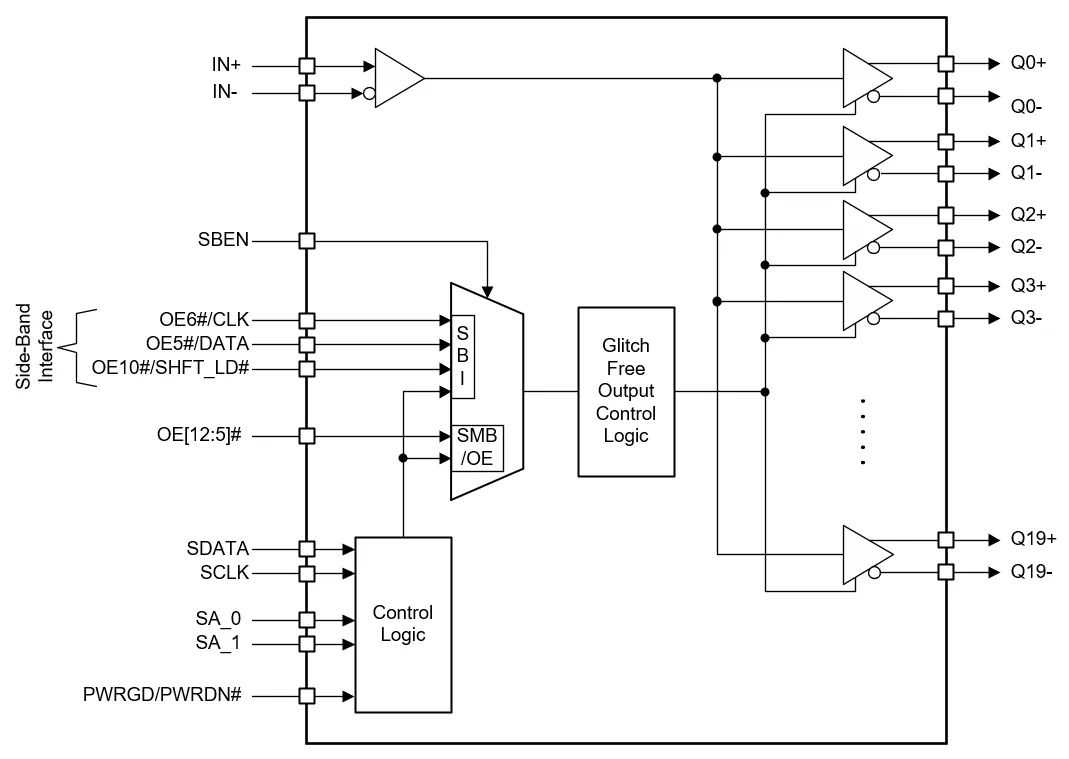

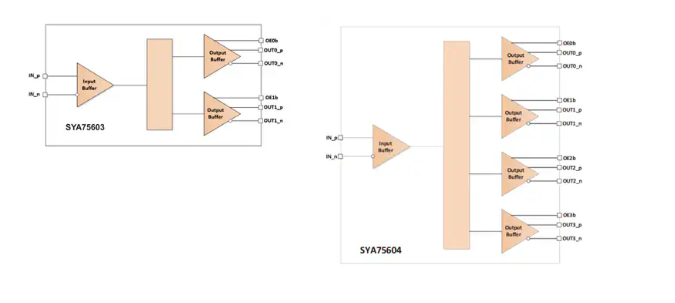

矽力杰新一代时钟缓冲器SQ82100提供20路超低附加抖动的LP-HCSL参考时钟,输出差分阻抗为85Ω。SQ82100高集成的输出端口可以节省外部匹配的80个终端电阻从而优化PCB布局。内部集成OE,SMBus以及3线SBI (Side Band Interface) 功能以方便控制打开或关闭任何通道,调节输出信号幅度、阻抗及默认下电电平。

SQ82100

高性能20路PCIe时钟缓冲器

◆20路低功耗推挽式LP-HCSL PCIe 85Ω差分输出时钟

◆ 满足Intel DB2000QL指标要求

◆ 差分输出时钟附加抖动:

♢DB2000QL<30fs RMS

♢PCIe Gen4 <30fs RMS

♢PCIe Gen5 <20fs RMS

♢PCIe Gen6 <10fs RMS

◆ 输出频率范围: 1MHz to 400MHz

◆ 3.3V供电,典型功耗600mW

◆ 内部集成LDO

◆ 通道间Skew<50ps

◆ SMBus接口和SBI接口

◆ 8个OE控制引脚

◆ 允许掉电情况下数字引脚有输入信号(PDT), 确保在异常系统条件下的器件得到保护

◆可选的SMBus地址允许同时使用多个器件

◆ 紧凑型封装: AQFN6x6-80

性能优势

超低附加抖动

随着数据传输速率要求不断提高,为了保证系统无码传输,PCIe高速接口对参考时钟的RMS抖动指标要求愈加苛刻,最新的PCIe Gen6要求100MHz参数时钟在协议规定的积分带宽内低于100fs RMS的时钟抖动。PCIe接口对参考时钟的指标要求如下:

SQ82100 的超低附加抖动远超PCIe Gen5.0, Gen6.0的性能指标要求,能够有效简化PCIe系统设计,为系统设计提供更多的设计余量。

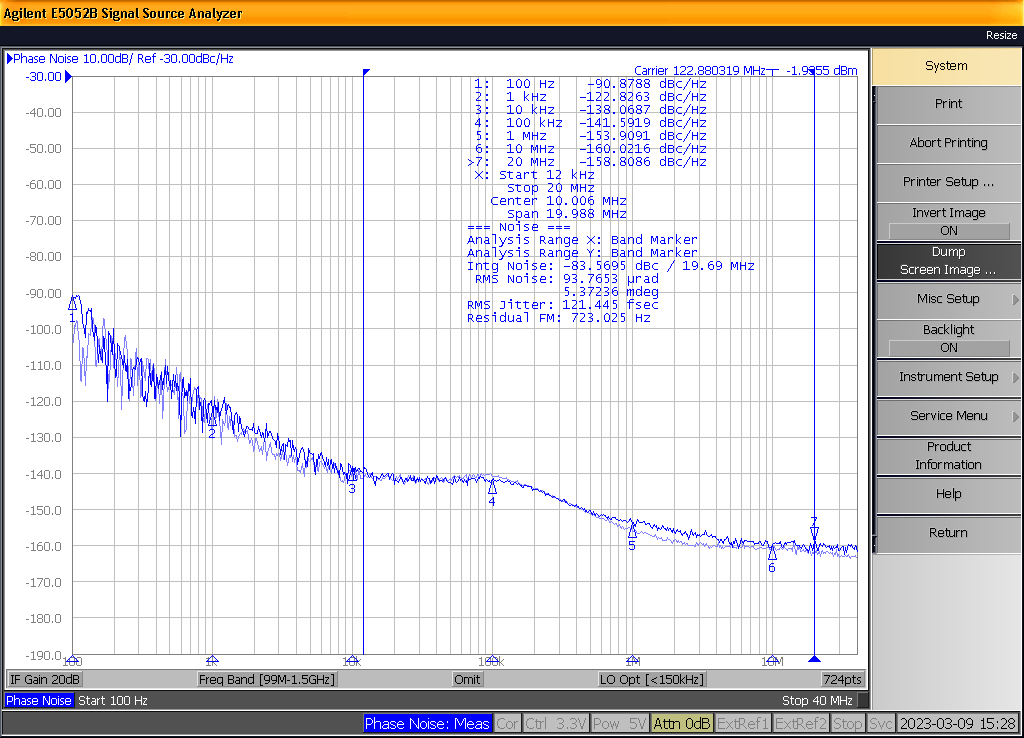

下图为SQ82100附加抖动测试:时钟频率122.88MHz,附加抖动测试值为48fs。

通道间skew<50ps

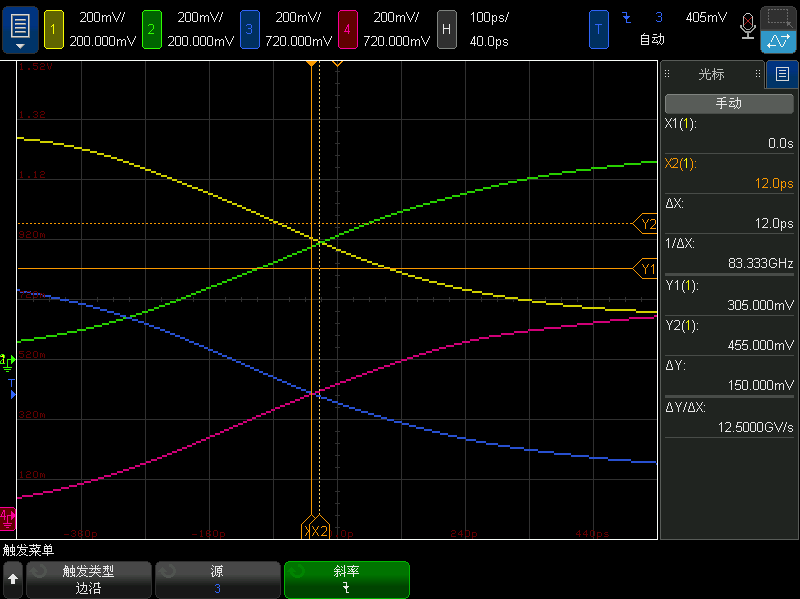

通道间skew将影响各PCIe终端之间的时钟同步,甚至限制系统速率和PCIe速率。SQ82100通道间skew<50ps,实现了20路输出时钟的精确同步,可保证PCIe系统正常工作,充分发挥PCIe Gen5.0, Gen6.0传输速率。

-

时钟缓冲器

+关注

关注

2文章

273浏览量

51954 -

计算机

+关注

关注

19文章

7837浏览量

93447 -

PCIe

+关注

关注

16文章

1474浏览量

88897 -

矽力杰

+关注

关注

4文章

161浏览量

2878

发布评论请先 登录

高性能时钟缓冲器LTC6955:特性、应用与设计要点

CDCM1802时钟缓冲器:高性能与灵活性的完美结合

深入解析CDCLVP2106:高性能时钟缓冲器的卓越之选

CDCLVP1204:高性能时钟缓冲器的技术剖析与应用探索

深入剖析CDCLVP1208:高性能时钟缓冲器的卓越之选

深入剖析CDCLVC11xx:高性能时钟缓冲器的卓越之选

CDCLVC11xx:高性能LVCMOS时钟缓冲器的卓越之选

CDCLVD2106:高性能双路 1:6 低附加抖动 LVDS 时钟缓冲器的深度解析

CDCDB2000:PCIe时钟缓冲器的卓越之选

探秘LMKDB11xx:PCIe时钟缓冲器的卓越之选

探索LMKDB11xx:PCIe时钟缓冲器的卓越之选

高性能PCIe Gen7 1.8V扇出缓冲器RC191xx:特性、应用与设计指南

Microchip SYA7560系列PCIe时钟缓冲器技术总结

矽力杰高性能20路PCIe时钟缓冲器

矽力杰高性能20路PCIe时钟缓冲器

评论