在最近的IEDM大会上,英特尔表示,已将 CMOS 硅晶体管与氮化镓 (GaN) 功率晶体管集成,用于高度集成的48V设备。

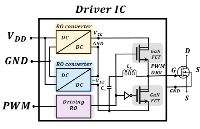

具有集成驱动器的 GaN 器件由 Cambridge GaN Devices、EPC 和 Navitas 以及英飞凌领导的欧洲重大研究项目开发。

Components Research 芯片中尺度工艺开发总监 Paul Fisher 表示:“英特尔是唯一一家专注于 48V 及以下电压下 GaN 效率利用的公司。”

“去年,我们展示了具有业界最佳品质因数的 GaN 晶体管,增益比 LDMOS 或 e-mode GaN HEMT 等硅器件高出 20 倍。这对我们来说是一个真正的突破,我们正在通过在 300mm 硅片上使用 Gan 和 CMOS 的大规模 3D 单片工艺,更进一步地迈出这一一步。”英特尔首席工程师 Han Wui 说道。该论文将于本周在美国举行的 IEDM 2023 会议上发表。

“不仅如此,我们还为第一个集成 CMOS 驱动器提供了 DR 驱动器 GaN,并在同一个芯片上单片集成了 GaN 电源开关,”他说。

英特尔于 2004 年推出首款 DR MOS,并成为同时向 PC 和数据中心服务器供电的行业标准。驱动器和电源集成使用硅晶体管提供了具有低寄生效应的高密度解决方案。

Wui 表示:“我们的工作表明,可以将硅 PMOS 晶体管与 GaN 晶体管结合起来,并具有高品质因数,以跟上功率密度的增长步伐。”

“GaN 器件对于 n 沟道来说是一种很棒的器件,但作为一种补充技术,在使用空穴承载电流方面将面临 p 模式的挑战,因为它们的迁移率非常低,而这正是硅 p 沟道的用武之地,”他说。“我们的 DR GAN 具有一个GaN N 沟道和一个硅 p 沟道器件,具有高迁移率以及栅极氧化物和触点。”

在 300 mm 硅片上堆叠 GaN 和硅晶体管

2020年时候,英特尔高管曾发文表示,向 5G 及更高技术的过渡预计将推动联网移动设备数量呈指数级增长。为它们供电的集成电路需要以更小的外形尺寸提供更高的能效。因此,对功能更强大的晶体管以及在微芯片上集成越来越多的组件的需求很大。

满足这些要求绝非易事,因为当今的晶体管技术都无法满足与电力传输和射频前端设计相关的多样化需求。由于这个问题,电路设计人员正在组合许多不同的、独立的芯片。这不太好,因为它会导致封装体积庞大。

为了解决这个问题,英特尔位于俄勒冈州技术开发小组的英特尔组件研究部门的团队开发了第一个单片、三维 GaN 和硅晶体管堆叠技术。它提供一流的性能和效率,同时允许将多种功能集成在单个芯片上。

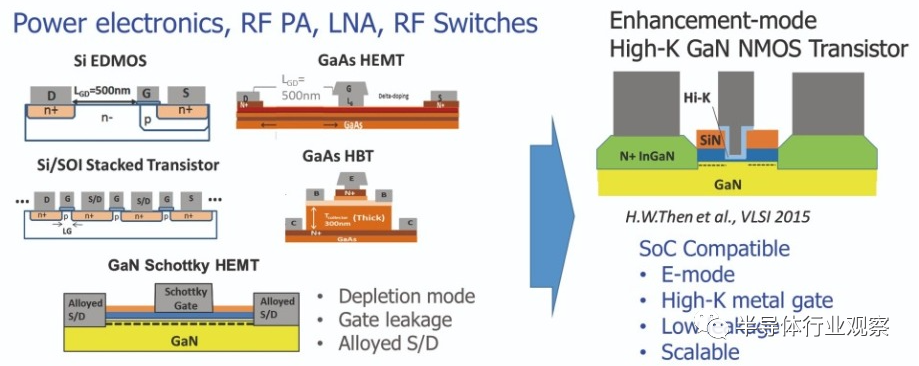

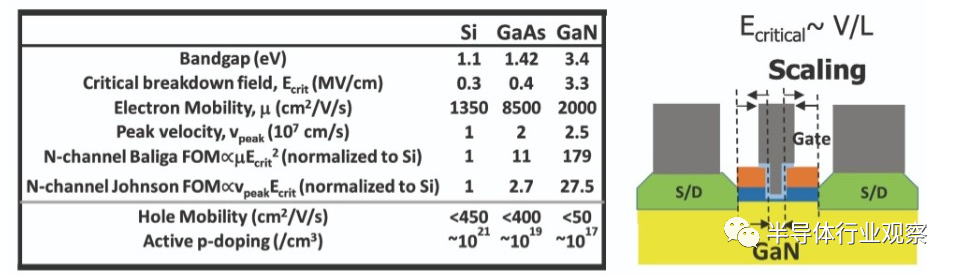

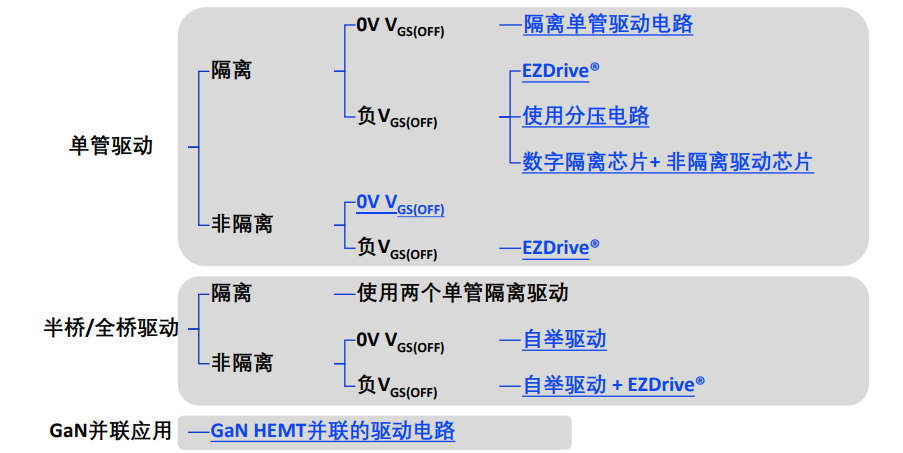

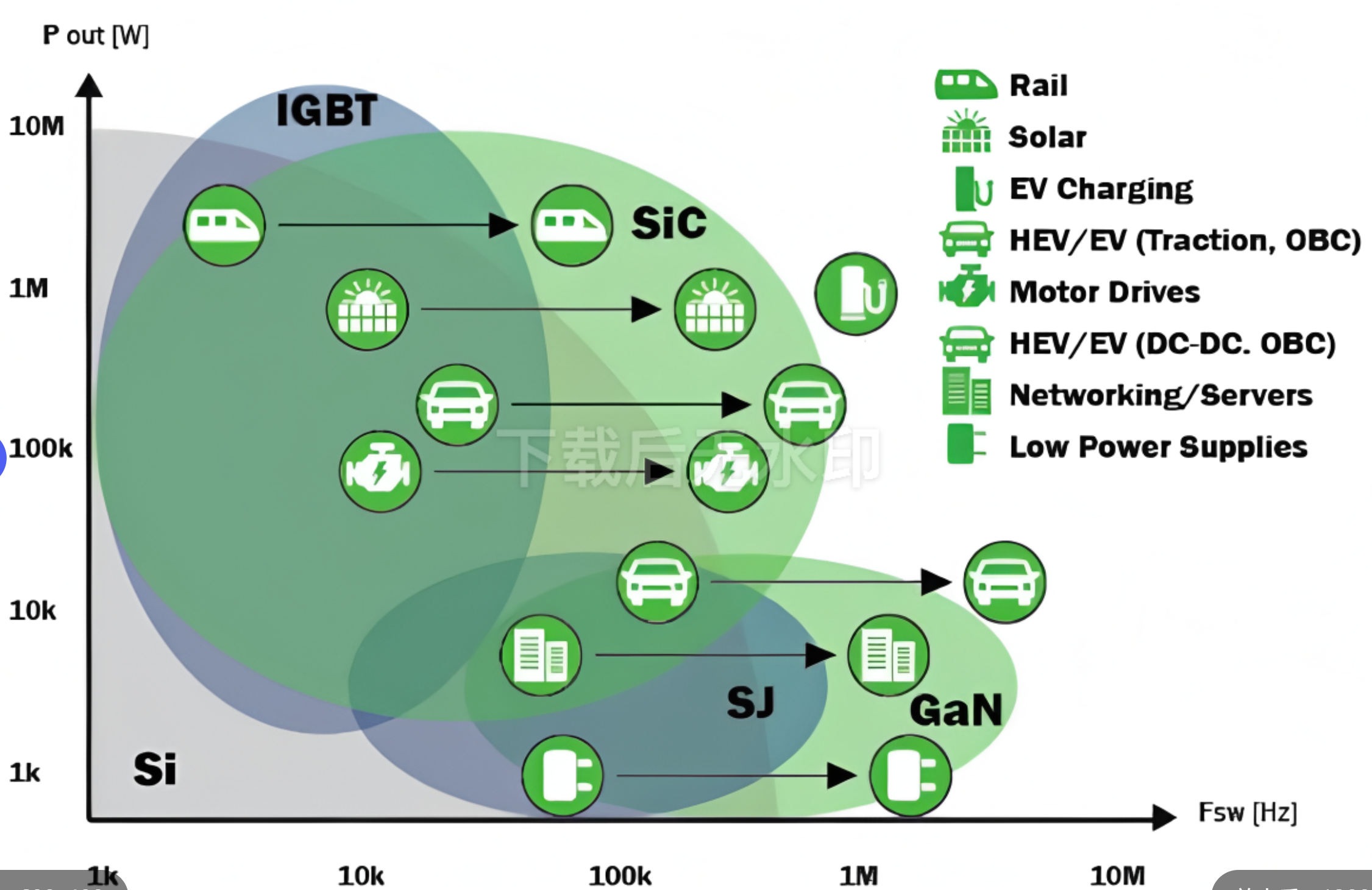

将硅和氮化镓结合起来是一个有吸引力的提议。硅是当今电力电子和射频开关的主力,但它难以提供高频、高功率性能,因此对于射频功率放大来说它不是一个好的选择(见图 1)。对于该特定任务,GaAs HBT、GaAs HEMT 和 GaN HEMT 是领先者。然而,这些技术并不是制造高效电力电子器件的理想选择:耗尽型 GaAs HEMT 和 GaN HEMT 因其始终开启的特性而不受青睐;GaAs HBT 不适合,它是电流驱动而不是场驱动。

幸运的是,有一种在各方面都表现出色的晶体管:增强型(e 模式)GaN 晶体管。最近,我们已经证明,当此类器件配备高 K 介电金属栅极技术时,它可以在功率传输和射频前端功能方面提供一流的性能。在此成功的基础上,我们使用三维单片集成将 GaN 功率和 RF 晶体管技术与 300 mm 硅基板上的硅 PMOS 结合起来。因此,所有功能都可以集成在单个芯片上,从而首次形成片上系统。

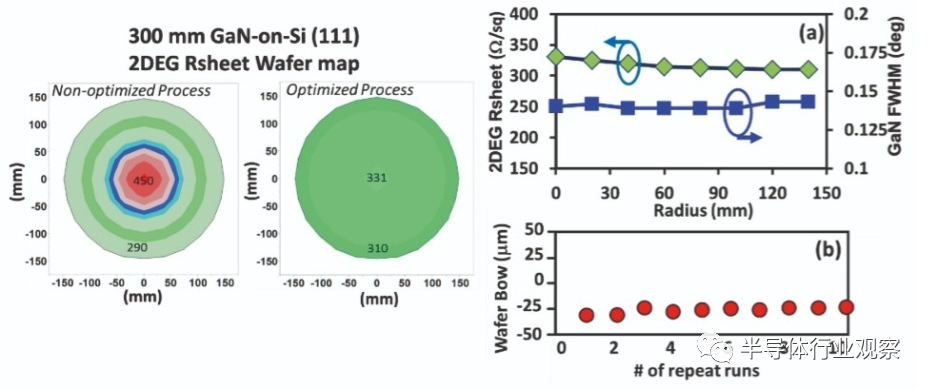

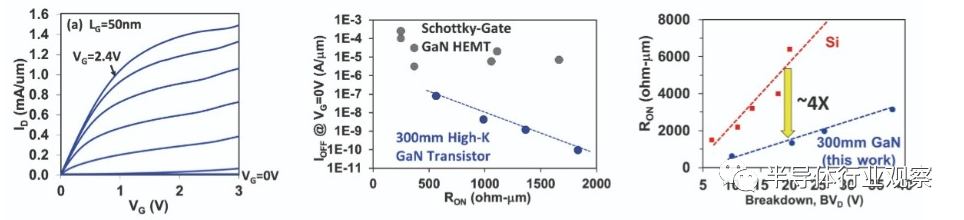

我们的努力取得的成功之一是在 300 mm 硅 晶圆上制造了第一批高性能 GaN 晶体管(见图 2)。我们采用与领先 CMOS 晶圆厂兼容的 300 毫米工艺技术制造这些晶体管。

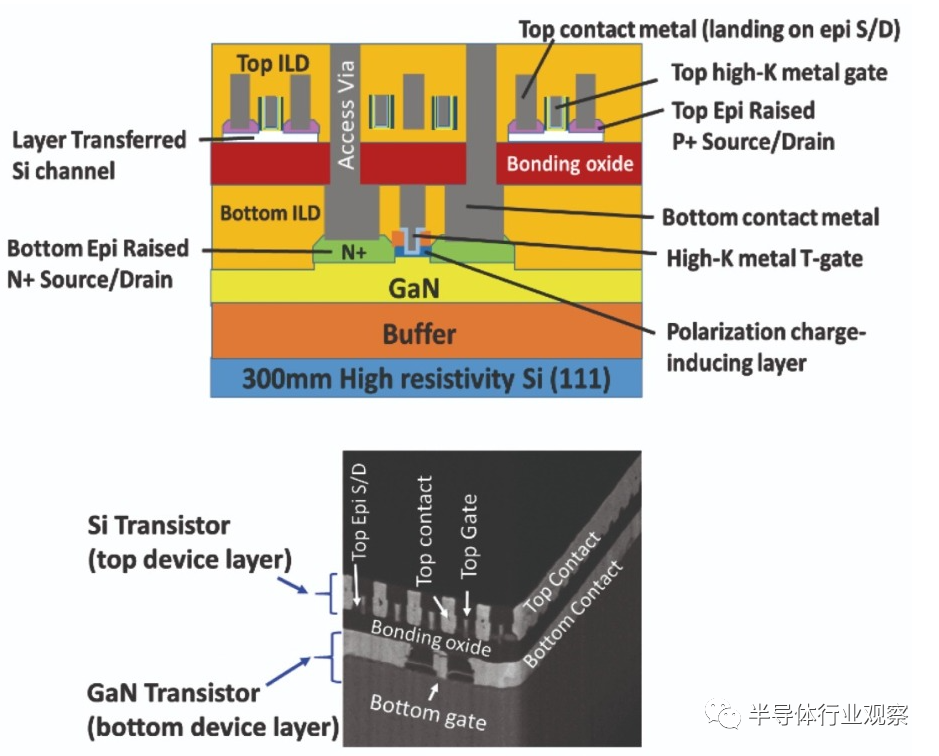

另一项成就是英特尔使用了基于层传输的三维单片集成新技术。通过这种方法,英特尔在 GaN NMOS 晶体管之上堆叠硅 PMOS 晶体管以实现 CMOS 功能,从而开辟了新天地。这项新技术显着扩展了可在高效、微型片上系统中实施和集成的解决方案范围。

使用英特尔领先的 CMOS 工厂之一在 300 mm 硅片上加工 GaN 晶体管可以获得额外的回报——为所有最新工艺创新打开了大门。它们包括高κ技术、三维层转移、化学机械抛光、光刻技术和铜互连。此外,我们还受益于更便宜的 300 mm 硅基板和大批量生产带来的成本显着降低。

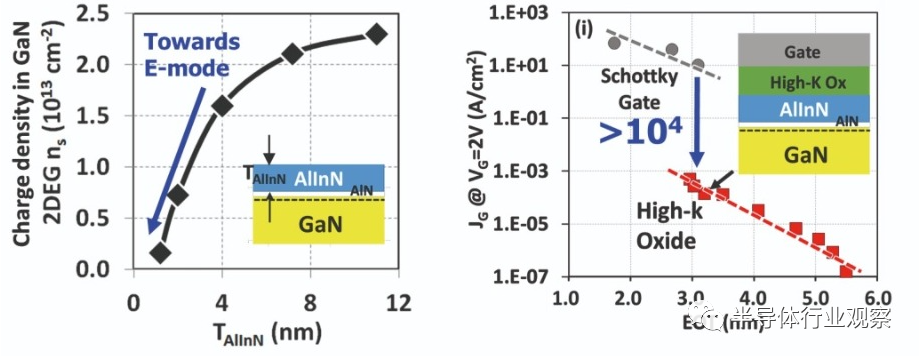

由于缺乏原生衬底,几乎所有的GaN都生长在异质衬底上,例如蓝宝石、SiC和硅。最流行的平台是相对昂贵的3英寸和4英寸SiC,以及4英寸、6英寸和8英寸硅。相比之下,英特尔使用经济高效的 300 mm 硅 基板(见图 3)。在此平台上,英特尔将 GaN 与 300 mm 晶圆厂中最先进的高 K 介电金属栅极技术结合起来。这使得增强模式操作和栅极堆叠缩放成为可能,并最终实现高性能和低泄漏,这是提高效率的关键。请注意,泄漏的减少非常显着——它比肖特基栅极 GaN HEMT 好超过四个数量级(见图 4)。

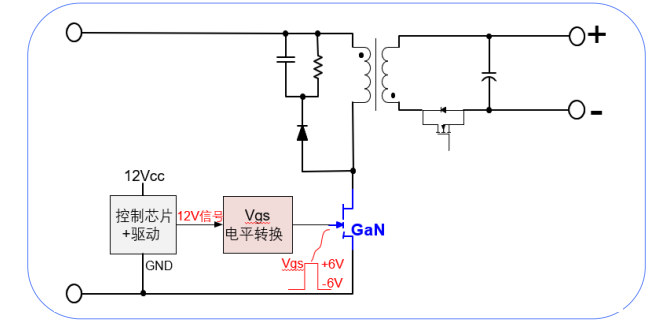

增强型 GaN 晶体管技术的另一个优点是它简化了电路架构。由于增强型晶体管是常关型的,因此不需要负电源。相反,该设备可以直接由电池驱动,从而节省了微芯片上宝贵的空间。

对 300 mm 硅片上的高 K 介电增强模式 GaN NMOS 晶体管进行的测量显示出出色的电气特性以及一流的功率传输和射频性能。该器件具有低漏极泄漏、高驱动漏极电流、低拐点电压和低导通电阻。这些特性表明,高 K 电介质技术使 GaN 晶体管能够将低漏电与卓越性能结合起来,其功率传输性能比行业标准硅晶体管好约四倍(见图 5)。

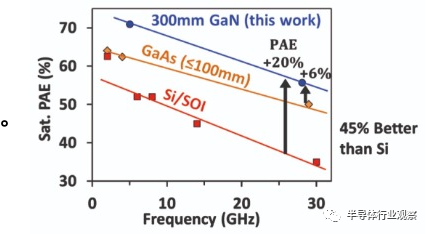

英特尔的设备还提供出色的射频性能。这些高 K GaN NMOS 晶体管在 1 GHz 至 30 GHz 的宽频率范围内的功率附加效率显着优于基于 GaAs 和硅/SOI 晶体管的晶体管(见图 6)。由于具有出色的拐点电压和导通电阻,可以在低至 1V 的漏极电压下实现高效的功率放大器 (PA) 操作(见图 7)。

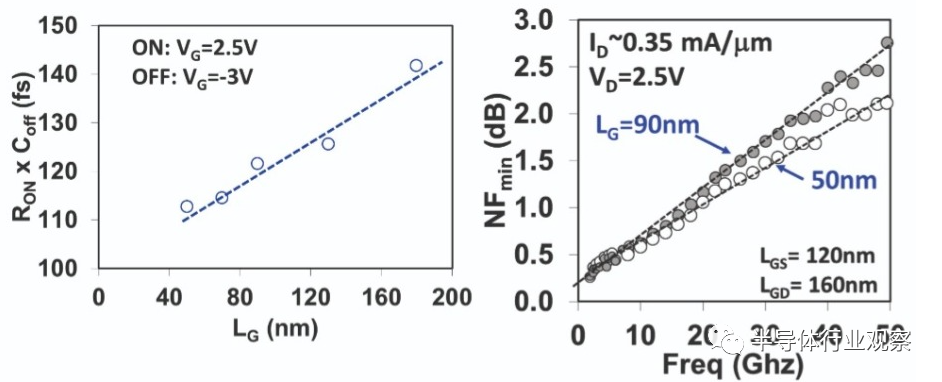

该值远低于典型 GaAs HBT 的最小截止电源电压,凸显了高 K GaN NMOS 晶体管显着延长电池寿命的潜力,同时使用包络跟踪 RF PA 架构提供无与伦比的效率。高κ GaN NMOS 晶体管还可用作出色的射频开关和低噪声放大器。例如,它们的开关具有出色的品质因数,导通电阻和关断电容的乘积仅为 110 fs。5 GHz 时的最小噪声系数仅为 0.4 dB,28 GHz 时的最小噪声系数仅为 1.36 dB(见图 8)。

功率放大器、低噪声放大器、射频开关和功率晶体管的出色性能相结合,使增强型高κ GaN NMOS 晶体管技术能够提高射频前端和功率传输的效率和性能系统超越了当今 GaAs 和硅技术的能力。但这还不是全部——通过采用高κ GaN NMOS 晶体管技术,英特尔在单个芯片上实现了多种功能的紧凑集成,从而节省了空间并实现了无与伦比的小外形尺寸。

当今市场的一个卖点是 CMOS 模拟和数字逻辑/控制功能以及 CMOS 存储器的紧密片上集成。这些类型的 CMOS 芯片目前是作为独立单元构建的,但随着功能和复杂性的增加,将需要单片系统级芯片解决方案来提供更高的效率、更低的成本和更高的集成密度(见图 9)。

然而,由于 GaN 的空穴迁移率较低,且难以实现高p 型掺杂在该材料中。好消息是,英特尔的团队与康奈尔大学和麻省理工学院的研究小组之间的合作取得进展。这项工作希望实现 GaN PMOS 宽带隙、高电压运行的承诺。虽然这项工作还处于起步阶段,但希望标准高 K 金属栅极硅 PMOS 能够介入,为 GaN NMOS 提供出色的互补 p 沟道技术,因为它具有高空穴迁移率并有可能实现非常高的源极-漏极接触的掺杂。

为了将多种不同的半导体材料单片集成在单个硅基板上,英特尔转向了层转移技术。这使其能够将硅 PMOS 晶体管单片堆叠在 GaN NMOS 晶体管之上。利用这种形式的三维单片集成有很多优点,因为它允许单独构建和优化每种组成的晶体管技术,以提供最佳的性能和成本。

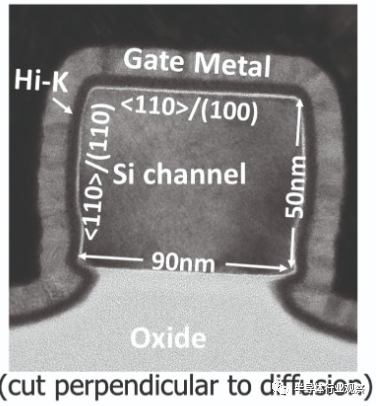

英特尔通过将标准 300 mm 晶体硅供体晶圆氧化物熔合到完整的 300 mm 硅基 GaN 晶圆来开始三维层转移工艺。此后,英特尔移除体供体晶圆并制造硅 PMOS 晶体管(见图 10)。通过将 finfet 对准可提高空穴迁移率的方向来确保高性能硅 PMOS。这是通过将侧壁上的晶体管沟道定向为特定晶面和载流方向来实现的(见图 11)。

据英特尔所说,这样的方法有很大的自由度。硅 PMOS 晶体管的设计和架构可以独立于底部 GaN 晶体管的选择。例如,通过为硅 PMOS 选择适当的沟道方向和为 GaN NMOS 选择适当的沟道长度,可以使两个沟道的驱动电流和断态泄漏相匹配(见图 12)。

英特尔的 GaN NMOS 和硅 PMOS 晶体管的单片三维堆叠提供了一种强大的方法,可以在同一晶圆上集成两种不同的一流半导体技术,并提供最佳性能、更高的密度和更强大的功能。

这项技术具有巨大的前景,因为它可以实现具有改变游戏规则功能的全新产品类别。许多令人兴奋的机遇摆在面前,包括高效、高性能射频和电力传输与标准硅基处理器的全面集成。这种技术有潜力满足 5G 及更高版本的下一代移动设备、数据基础设施和通信网络的需求。

由于其宽带隙,与 GaAs 和硅相比,GaN 具有远远优越的 Johnson 和 Baliga 品质因数(见表 1)。这些优点使 GaN 能够在高频和高功率下工作。

GaN 的另一个优势源于与该系列材料相关的自发极化效应和压电极化效应。因此,在GaN和相关三元合金界面处的GaN沟道中产生二维电子气,而不需要杂质掺杂。

由于电子有效质量低且不存在杂质散射,所得的 GaN 异质结构具有高载流子浓度和高电子迁移率。

GaN 的另一个优点是,由于其宽带隙,它的临界击穿场至少是 GaAs 和硅的十倍。这使得 GaN 晶体管可以缩小到更小的长度,从而获得更高的性能。例如,对于由锂离子电池提供的3.7V电源电压,GaN晶体管可以更短、具有更低的电阻并提供更高的驱动电流。诸如此类的优势使 GaN 成为当今生产中功率和射频性能最佳的半导体技术。

审核编辑:刘清

-

CMOS

+关注

关注

58文章

6189浏览量

241582 -

驱动器

+关注

关注

54文章

9016浏览量

153370 -

英特尔

+关注

关注

61文章

10275浏览量

179317 -

氮化镓

+关注

关注

66文章

1858浏览量

119215 -

硅晶体管

+关注

关注

0文章

10浏览量

3488

原文标题:英特尔发力氮化镓

文章出处:【微信号:第三代半导体产业,微信公众号:第三代半导体产业】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

如何在开关模式电源中运用氮化镓技术

CE65H110DNDI 能华330W 氮化镓方案,可过EMC

氮化镓(GaN)充电头安规问题及解决方案

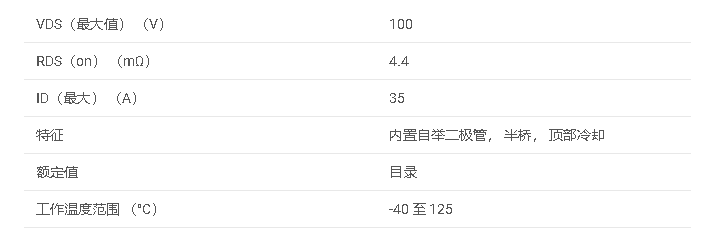

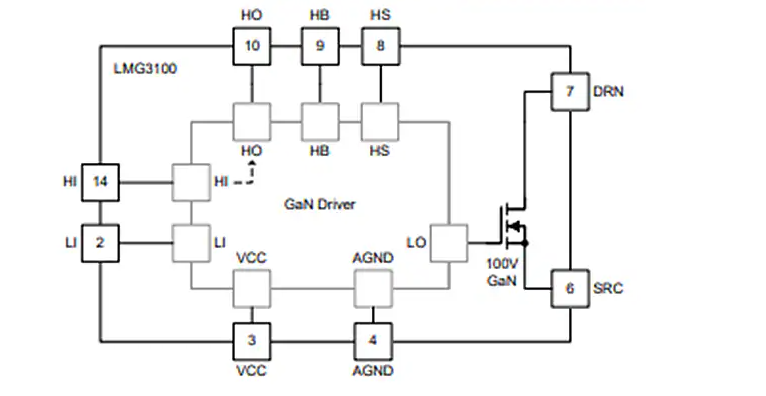

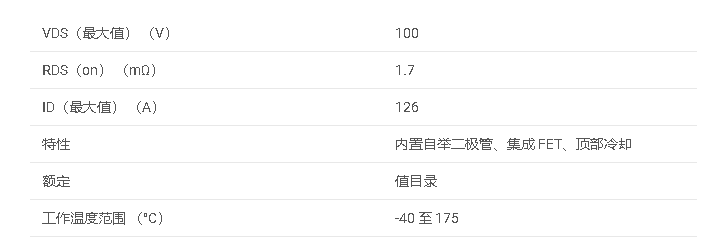

技术资料#LMG2100R026 100V 2.6mΩ 半桥氮化镓 (GaN) 功率级

TI LMG2100R044 具有集成驱动器和保护功能的 100V 4.4mΩ 半桥 GaN FET应用与设计

TI LMG2100R044 具有集成驱动器和保护功能的 100V 4.4mΩ 半桥 GaN FET

英特尔发力具有集成驱动器的氮化镓GaN器件

英特尔发力具有集成驱动器的氮化镓GaN器件

评论