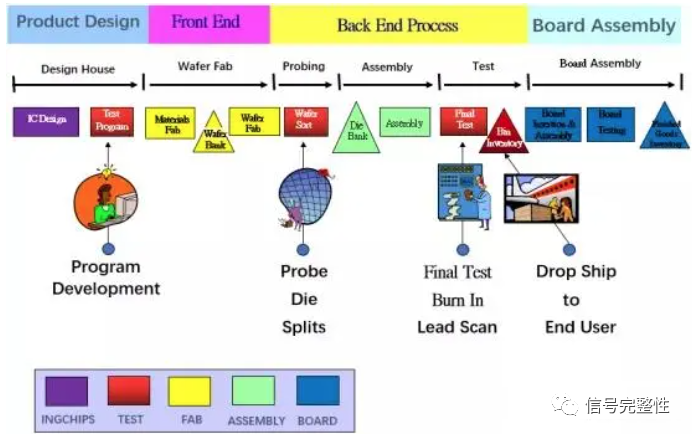

半导体生产流程由晶圆制造,晶圆测试,芯片封装和封装后测试组成。而测试环节主要集中在CP(chip probing)、FT(Final Test)和WAT(Wafer Acceptance Test)三个环节。

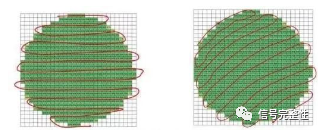

CP测试,英文全称Circuit Probing、Chip Probing,也称为晶圆测试,测试对象是针对整片wafer中的每一个Die,目的是确保整片wafer中的每一个Die都能基本满足器件的特征或者设计规格书,通常包括电压、电流、时序和功能的验证,如vt(阈值电压),Rdson(导通电阻),BVdss(源漏击穿电压),Igss(栅源漏电流),Idss(漏源漏电流)等,可以用来检测fab厂制造的工艺水平。可以更直接的知道Wafer的良率。

CP的难点是如何在最短的时间内挑出坏的die,修补die。

常用到的设备有测试机(Tester) 、探针台(Prober) 以及测试机与探针卡之间的接口(Mechanical lnterface)。一般测试机台的电压和功率不会很高。

FT测试,英文全称Final Test,是芯片出厂前的最后一道拦截。测试对象是针对封装好的chip,CP测试之后会进行封装,封装之后进行FT测试,也叫“终测”。可以用来检测封装厂的工艺水平。FT是把坏的chip挑出来;检验封装的良率。测试完这道工序就直接卖去做应用了。

FT测试一般分为两个步骤:1)自动测试设备 (ATE) 2) 系统级别测试SLT) --2是必须项,1一般小公司可能用不起,ATE试一般只需要几秒钟;SLT一般需要几个小时,逻辑比较简单。

FT的难点是如何在最短的时间内保证出厂的Unit能够完成全部的功能。FT需要tester (ATE) + handler + socket。

CP对整片Wafer的每个Die来测试,而FT则对封装好的Chip来测试。CP Pass 才会去封装。然后FT,确保封装后也Pass。

WAT是Wafer Acceptance Test,对专门的测试图形(test key)的测试,通过电参数来监控各步工艺是否正常和稳定;WAT(Wafer Acceptance Test)测试,也叫PCM(Process Control Monitoring),对Wafer 划片槽(Scribe Line)测试键(Test Key)的测试,通过电性参数来监控各步工艺是否正常和稳定。

WAT测试有问题,超过SPEC,一般对应Fab各个Module制程工艺或者机台Shift,例如Litho OVL异常,ETCH CD 偏小,PVD TK偏大等等。WAT有严重问题的Wafer会直接报废。

对于测试项来说,有些测试项在CP时会进行测试,在FT时就不用再次进行测试了,节省了FT测试时间;但是有些测试项必须在FT时才进行测试(不同的设计公司会有不同的要求)。

一般来说,CP测试的项目比较多,比较全;FT测的项目比较少,但都是关键项目,条件严格。但也有很多公司只做FT不做CP(如果FT和封装yield高的话,CP就失去意义了)。

在测试方面,CP比较难的是探针卡的制作,并行测试的干扰问题。FT相对来说简单一点。还有一点,memory的CP测试会更难,因为要做redundancy analysis,写程序很麻烦。

CP在整个制程中算是半成品测试,目的有2个,一个是监控前道工艺良率,另一个是降低后道成本(避免封装过多的坏芯片),其能够测试的项比FT要少些。

最简单的一个例子,碰到大电流测试项CP肯定是不测的(探针容许的电流有限),这项只能在封装后的FT测。不过许多项CP测试后FT的时候就可以免掉不测了(可以提高效率),所以有时会觉得FT的测试项比CP少很多。

应该说WAT的测试项和CP/FT是不同的。

CP不是制造(FAB)测的!而CP的项目是从属于FT的(也就是说CP测的只会比FT少),项目完全一样的;不同的是卡的SPEC而已;

因为封装都会导致参数漂移,所以CP测试SPEC收的要比FT更紧以确保最终成品FT良率。还有相当多的Design House把wafer做成几个系列通用的die,在CP是通过trimming来定向确定做成其系列中的某一款,这是解决相似电路节省光刻版的最佳方案;所以除非你公司的wafer封装成device是唯一的,且WAT良率在99%左右,才会盲封的。

CP用prober,probe card。FT是handler,socket CP比较常见的是room temperature=25度,FT可能一般就是75或90度 CP没有QA buy-off(质量认证、验收)。

FT测试通常是测试项最多的测试了,有些客户还要求3温测试,成本也最大。至于测试项。如果测试时间很长,CP和FT又都可以测,像trim项,加在probe能显著降低时间成本,当然也要看客户要求。•关于大电流测试,FT多些,但是我在probe也测过十几安培的功率mosfet,一个PAD上十多个needle。

有些PAD会封装到device内部,在FT是看不到的,所以有些测试项只能在CP直接测,像功率管的GATE端漏电流测试Igss CP测试主要是挑坏die,修补die,然后保证die在基本的spec内,function well。FT测试主要是package完成后,保证die在严格的spec内能够function。

关于3温测试:这是一种特殊的测试方法,它要求在三个不同的温度下对产品进行测试,通常是常温(25℃左右)、高温(如60℃或70℃)和低温(如-20℃或-40℃)。这种测试的目的是为了检查产品在不同温度下的性能和可靠性,以确保产品能在不同环境下正常工作。

审核编辑:刘清

-

半导体

+关注

关注

339文章

31292浏览量

266840 -

晶圆

+关注

关注

53文章

5451浏览量

132799 -

芯片封装

+关注

关注

14文章

625浏览量

32403 -

击穿电压

+关注

关注

1文章

63浏览量

9568 -

漏电流

+关注

关注

1文章

280浏览量

17993

原文标题:芯片的几个重要测试-CP、FT、WAT

文章出处:【微信号:SI_PI_EMC,微信公众号:信号完整性】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

如何区分CP测试和FT测试

季丰嘉善车规芯片量产测试线能力介绍——三温CP、三温FT、Burn-in、三温SLT

半导体制造的关键环节:芯片测试

芯片的几个重要测试环节-CP、FT、WAT

芯片的几个重要测试环节-CP、FT、WAT

评论